硅基沟槽功率器件漏电检测及异常分析

2022-10-08陈章隆范江华巩小亮

金 磊,魏 唯,陈 龙,陈章隆,范江华,巩小亮

(中国电子科技集团公司第四十八研究所,长沙410111)

随着新能源电动汽车及5G互联网市场的突飞猛进,功率半导体器件的市场需求依然保持旺盛地增长。尽管碳化硅、氮化镓、氧化锌等第三代半导体在材料本征性能上有一定先天优势[1-2],但受限于高成本、大规模量产的可控性问题,目前硅基沟槽功率器件仍然是主流产品[3]。

硅基功率产品最基本的器件是场效应晶体管(MOSFET)和肖特基势垒二极管(SBD),它们是组成MCU等模块的关键单元。在量产的晶圆代工厂中,均保留了MOS和SBD相关工艺。以硅基沟槽SBD产品为例,CP测试可完成管芯正向导通压降(VF)、导通电阻(Rd)、反向峰值电压(VR)、反向饱和漏电流(IR)等电性参数的收集。VF与晶圆外延层厚度关联较大,Rd与晶圆外延层电阻率、晶圆减薄厚度相关,VR与器件栅氧厚度相关性最强,而代表漏电参数的指标IR无法直接进行判断,往往需要结合制备工艺流程进行逐步排查及探究,从而进行问题分析及后续改善[4]。

本文介绍了微光显微镜(EMMI)及聚焦离子束-扫描电镜(FIB-SEM)检测方法,用于快速找出器件漏电相关电性趋势及对应的结构失效[5],其中,EMMI用于寻找晶圆或封装器件的漏电区域位置,FIB-SEM法用于漏点区域实时观测。这两种方法的有效结合可使晶圆漏电失效分析效率提高,漏电区域的SEM切片图片清晰度较高,为量产或中试晶圆代工生产线快速排查提供重要帮助。

1 实验方案及失效分析原理

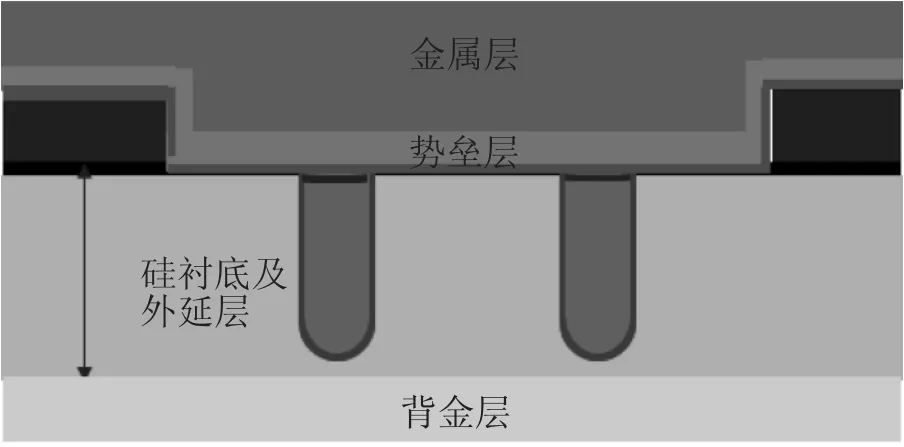

1.1 沟槽型功率器件制作流程

本实验采用200 mm(8英寸)n型<100>单晶Si外延片,在Si外延层上采用CVD淀积一层厚度为0.3 μm的SiO2作为坚膜层,用光刻和反应离子刻蚀制作出关键线宽为0.25~0.4 μm的Si深沟槽并依次填满栅氧及多晶硅,完成P阱和N阱注入后,采用CVD淀积SiO2及BPSG的中间隔离层,完成接触孔光刻、刻蚀及填孔后,采用PVD法沉积4 μm的AlCu金属层;背面则减薄至200 μm,最终在背面沉积Ti、Ni、Ag金属层,器件的最终结构示意图如图1所示。

图1 沟槽型肖特基势垒二极管横截面结构

1.2 EMMI热点分析原理介绍

EMMI(波长范围:400~1 100 nm),用于侦测晶圆异常失效点定位,寻找亮点、热点的工具。EMMI属于非破坏性试验,可以从标本的背面或正面进行,发射的光子由高灵敏度的CCD相机检测,能够检测当电子/空穴对在设备中重新结合时发射的光子以获取信号,对于器件而言,EMMI可用于检测由器件缺陷引起的泄漏电流,例如栅极氧化缺陷/泄漏、闩锁、ESD故障、结泄漏等。实验采用InGaAs EMMI技术,检测范围最大可达1 700 nm的红外波段,响应速度较普通EMMI快5~10倍,具备更快速、灵敏的优势。

1.3 FIB-SEM原理介绍

聚焦离子束(FIB)仪器几乎与SEM相同,但使用的是离子束而不是电子束。聚焦离子束可以通过溅射过程直接修改或“研磨”样品表面,并且这种研磨可以以纳米精度进行控制。通过精确控制离子束的能量和强度,可以进行非常精确地纳米加工。FIB系统与普通扫描电子显微系统同时放置在同一机台内,样品可调节至共心高度的位置,可在测试过程中旋转样品台,使样品表面垂直于电子束或离子束,以实现电子束实时观察及离子束切割或微纳加工的功能。FIB-SEM超高分辨率双束系统,可满足样品检测,半导体器件形貌观察等用途。结合实验采用的硅基沟槽型功率器件产品,FIB技术可实现截面分析,即精确完成漏电或失效特定区域切割后,对其横截面/断面的分析。与传统SEM对比,其优势在于是切割加工时有极高的定位精度,样品受到应力影响较小,可保留完整的切割横截面。

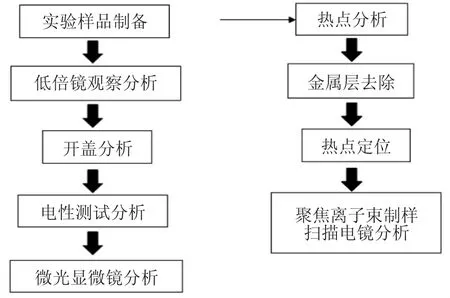

1.4 晶圆失效分析流程及测试仪器设备

图2为晶圆的失效分析流程图。如测试样品为未封装样品,则直接从I-V测试开始进行作业流程。测试仪器包括:超景深三维显微镜(基恩士VHX-7000)、半导体分析仪(是德科技B1500A)、微光显微镜(滨松PHEMOS-1000)、双束聚焦离子束显微镜(赛默飞Helios 5 UX)。

图2 晶圆漏电失效分析流程

2 结果与讨论

按照沟槽工艺、势垒层溅射及减薄背金的顺序制备沟槽SBD产品,即最大正向电流(Io)为30 A、最大反向峰值电压(VRM)为45 V。实验选取了4颗已完成封装的产品,采用晶圆失效分析流程方法对器件依次检测,并快速找到异常。

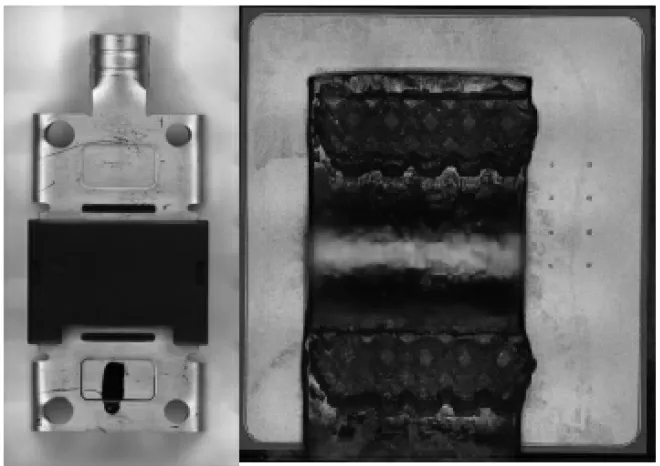

2.1 揭盖及电性能测试

完成目检、镜检确认器件外观无明显异常后,采用机械揭盖的方法将封装器件进行开盖处理。图3为封装器件开盖前后宏观及显微镜下照片。

图3 封装硅基SBD器件(左)及开盖后图(右)

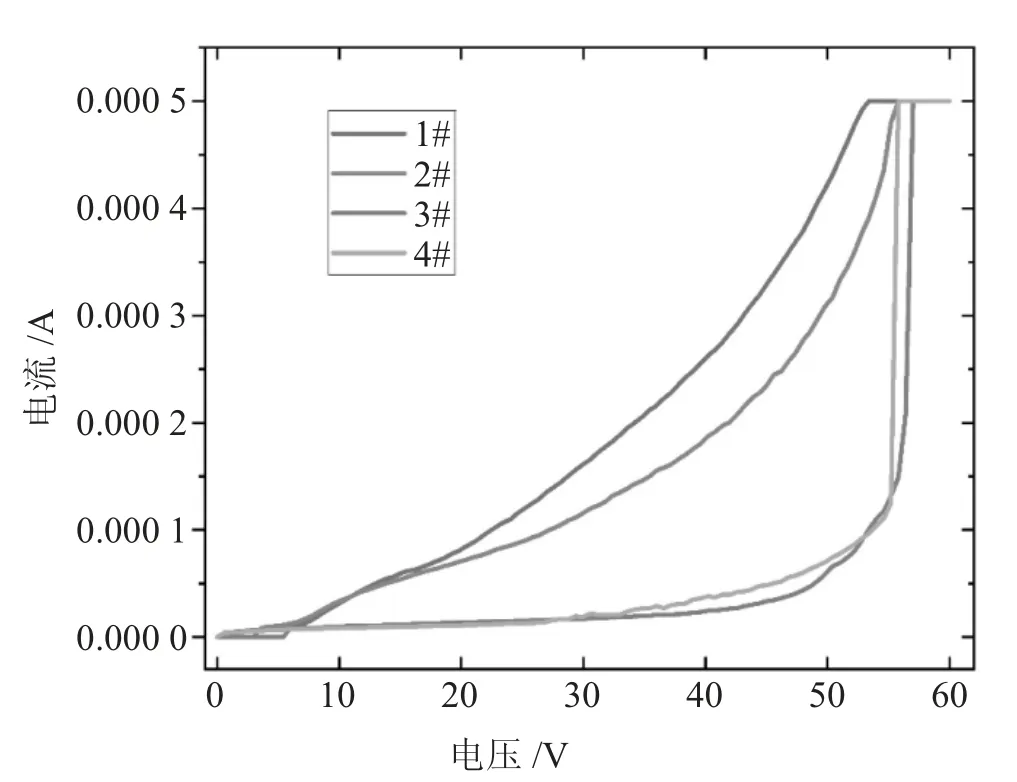

对4颗开盖后器件进行I-V曲线测试,测试条件为电流恒定为500 μA,因器件VRM为45 V,电压测试区间调整为0~60 V。图4为4颗管芯进行I-V测试后的曲线图。图4中,3#、4#符合器件VR变化规律,在50 V有漏电变大趋势;但是1#、2#在20 V以下漏电有显著增大,疑似出现软击穿的效应。为进一步验证,采用在低电压漏电更大的1#进行EMMI及热点分析。

图4 3045沟槽SBD产品Decap后I-V测试曲线图

2.2 EMMI、热点及热点定位分析

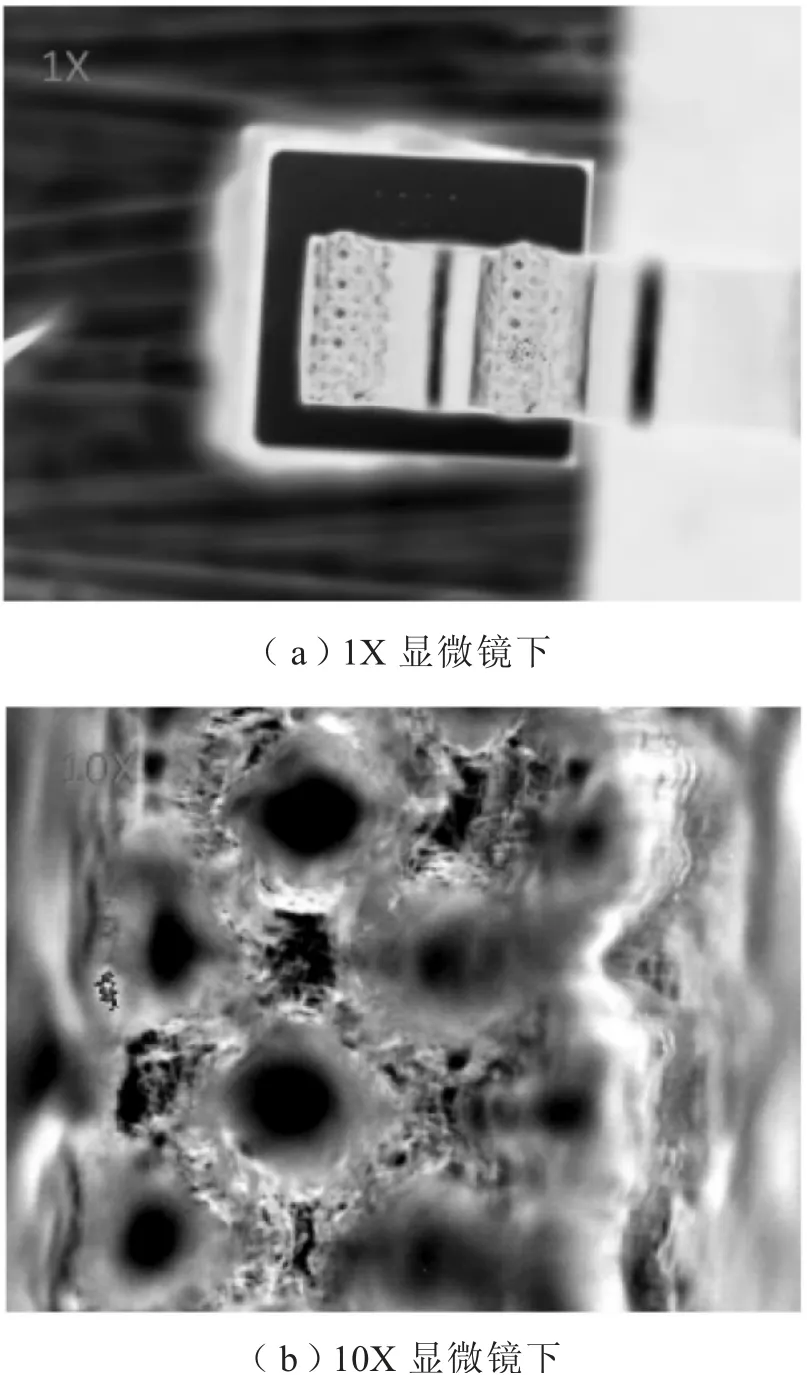

EMMI测试结果在50 V、500 μA下无明显异常,采用热分析法后,在40 V、316.3 μA的有明显热点,图5为不同倍率热点分析检测图片。

图5 不同倍率热点分析

热点问题,即本文所述漏电问题与器件栅、漏极存在关系,而上层铝金属仅用于减小导通电阻的平面互联层,为进一步更好地定位,采用湿法进行铝及引线腐蚀,得到有源区器件并采用EMMI分析,去除铝层后在50 V、50 μA下发现异常并迅速定位以便于下一步FIB切片寻点。

2.3 FIB-SEM切片形貌分析

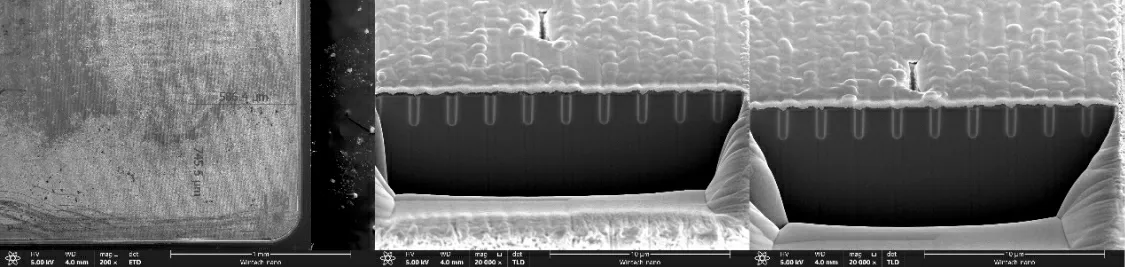

在热点分析完成后,在定位处进行FIB样品制备及推刀处理。图6为推刀过程器件剖面形貌图,可看出器件栅氧、多晶硅侧壁无锯齿状,倒角较为圆滑,及中间隔离层部分无明显颗粒及空洞。

图6 FIB-SEM推刀过程动态图

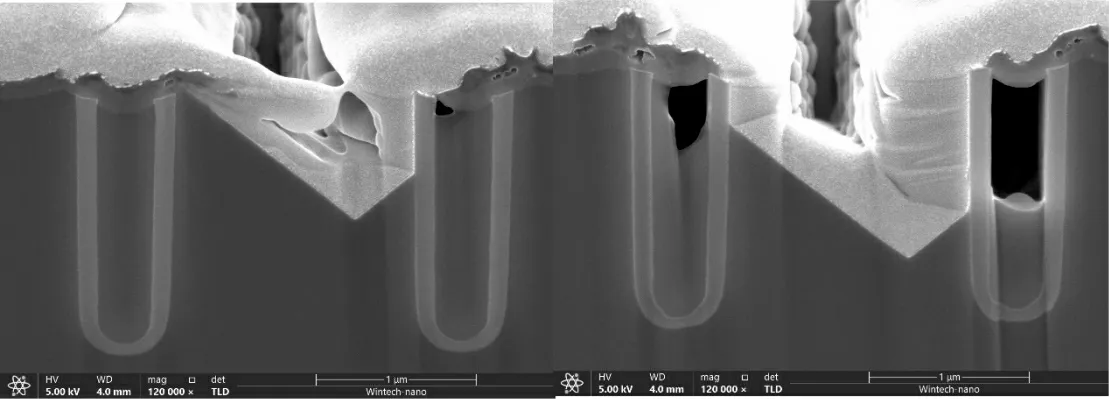

图7为器件明显异常处的剖面图,有2个管芯内沟槽内多晶硅部分存在异常空洞。

图7 器件沟槽空洞失效剖面图

2.4 形貌异常分析及后续预防措施

结合FIB-SEM推刀过程中形貌图,出现异常空洞的部分为沟槽内的多晶硅处,而多晶硅刻蚀后沉积了一层厚度约为800 nm的SiO2中间隔离层,对沟槽部分影响不大,因而异常空洞在多晶硅刻蚀及更前端工序发生;

多晶硅刻蚀过程是控制时间的方式来停止,而沟槽外的硅与多晶硅表面的高度差一般在100 nm以下,因此不会出现沟槽内部刻蚀过量导致的空洞形成;

多晶硅淀积过程中,生长方式为先从底部开始不断生长多晶硅,逐渐从底部向上、向侧壁不断生长,该生长方式与图7沟槽内空洞形成方式较为相似;在多晶硅淀积前的栅氧侧壁厚度较为均匀,无明显锯齿状及空洞、颗粒;因此可判断器件失效是多晶硅沉积过程中异常导致,即完成底部多晶硅淀积后,由于设备管路中或腔体内颗粒掉落至管芯沟槽处,阻塞了反应气体进入沟槽内部进行反应,导致异常产生。

结合实际机台作业情况,由于工艺环境条件发生变化或工艺操作过程中,硅片表面被“损伤”或“污染”,导致淀积的掺杂多晶硅出现填孔覆盖率低或颗粒变粗等异常情况。由于设备使用时间长(超期使用)、频率高,导致系统稳定性退化。可采取的措施是定期对系统进行清洗,保持系统的洁净,同时适当减小吹气阀和放气阀使用的N2流量,以减小管路内多晶硅颗粒及其他杂质的形成。

3 结束语

通过EMMI及FIB-SEM的检测方法,沟槽SBD器件多晶硅淀积异常已快速排查。器件电性、结构的快速检测能更好的解决量产器件漏电失效问题,对功率器件的低成本生产提供保障。