基于自动检测与动态补偿的DC-DC 转换器抗单粒子加固设计方法

2022-09-17郭仲杰刘楠卢沪刘申曹喜涛

郭仲杰,刘楠,卢沪,刘申,曹喜涛

(西安理工大学 自动化与信息工程学院,陕西,西安 710048)

在空间应用中,航天器主要受到总剂量效应、单粒子效应等辐照效应的影响,从而导致半导体器件出现功能性错误、失灵甚至毁坏. 随着工艺尺寸的缩小,单粒子效应的影响越来越严重. 半导体集成电路是电子设备的核心部件,其抗辐照能力直接决定了整 个 航 天 器 的 可 靠 性 水 平[1-2]. 尤 其 是 作 为 供 电 设 备之一的DC-DC 转换器,其抗辐照性能备受关注.

DC-DC 转换器属于数模混合集成电路,单粒子辐照对模拟电路的影响主要表现为模拟单粒子瞬态效 应(analog single event transient, ASET). 研 究 表 明,高能粒子穿透半导体材料的深度取决于粒子能量[3],粒子能量可以通过线性能量传输(linear energy transfer, LET)表述.

多模冗余设计是目前最常见的加固方案之一,SCHRAPE 等[4]中提出了一种基于三模冗余设计的D 触发器,并通过一级滤波延时单元消除单粒子瞬态效应的影响,该方案对SET 的抑制能力需要折中考虑延时的时间常数和时钟周期的大小. AKETI等[5]中指出传统冗余技术需要从一个电路或先前的输出中获得第3 个输入到判决器,弊端在于其面积消耗较大,然而为了节省面积会引入额外的延迟.

ANDREOU 等[6]中通过对比不同拓扑结构的带隙基准电路,对版图级的电荷共享机制做出了详细说明,然而其加固效果极大程度上依赖于版图布局.FAN 等[7]中为了较少面积开销,在传统环形栅工艺的基础上通过工艺改进,对总剂量效应和单粒子闩锁效应的抑制能力有显著提升,但是工艺级加固方案多基于较成熟工艺进行优化.

上述方案会带来较大的面积、功耗,抗单粒子辐照性能评估滞后等不利因素,导致电路设计者在前期设计中难以评估电路抗辐照性能. 针对上述不利因素,基于一款商用0.18 μm BCD 工艺单片集成的Boost 型DC-DC 转换器,对单粒子瞬态敏感特性进行了分析验证,并提出了一种ASET 检测与加固电路,实现了自动检测与动态补偿.

1 电路结构及敏感性分析

如图1 所示,是本文所研究的Boost 型DC-DC 转换器系统架构. 以峰值电流型PWM 控制器为核心的控制系统为双环结构,其中电压环为外环,输出电压经过分压得到的反馈信号与基准电压经过误差放大后得到的误差信号送入PWM 比较器,电流环为内环,逐周期采样电流信号. 电流信号和反馈信号共同对占空比进行控制.

图1 Boost 型DC-DC 转换器系统框架Fig. 1 System framework of boost DC-DC converter

当高能粒子撞击半导体材料中的敏感区域时,可能会产生ASET. 在ASET 的电路分析中,电荷收集机制可以通过在发生粒子碰撞的电路节点引入具有适当特性的瞬态电流源来表示. 瞬态电流源可用双指数函数进行建模,该电流模型[8-10]是由Messenger 等提出的,能够较为准确地模拟高能粒子对电路敏感节点的作用. 该模型在推导时假设电子空穴的产生率是恒定的,因此双指数电流模型和实际单粒子轰击产生的波形之间存在一定的误差. 然而,由于双指数瞬态电流模型形式简单易于操作,模拟精度较准确,因而仍被广泛应用于单粒子效应电路级仿真中. 其表达式如式(1)所示.

式中,q为一个电子的电荷量,q=1.6×10-19C;ρ为目标材料的体密度,本文基于硅材料,因此在计算时基于硅材料的体密度进行计算,ρSi=2 328 mg/cm3;t为高能粒子入射的深度,以μm 为单位,为了方便计算,本文忽略了其实际大小,以1 μm 为标准进行计算;LET 的含义是高能粒子穿过目标材料单位长度路径上所丢失的能量除以受到轰击半导体材料的密度;Eeh是在目标材料中电离一对电子-空穴对所需要的最小能量,在硅材料中每电离一对电子空穴对需要3.6 eV;Q的单位为pC.

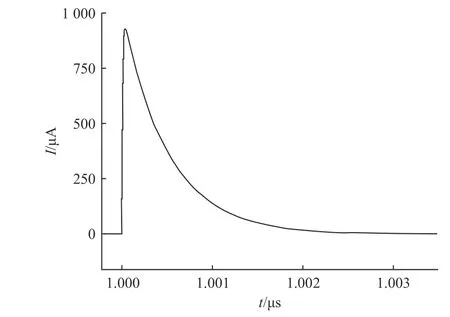

本文将采用上述单粒子瞬态电流模型进行电路级仿真 验证,文中τα与τβ分别设置 为500 ps、10 ps.LET=50 MeV·cm²/mg 的 高 能 粒 子 产 生 的 电 荷 量 为Q≈0.717 pC,对应双指数电流峰值为I0≈1 mA.

图2 给出了LET=50 MeV·cm2/mg 对应的双指数瞬态电流脉冲波形,电流峰值为905 μA,脉冲宽度约为3 ns. 进行ASET 仿真分析时,将此电流注入电路的敏感节点中模拟单粒子对电路节点的轰击,脉冲注入时间和脉冲幅度、宽度均可根据需要调整.

图2 单粒子瞬态电流脉冲波形Fig. 2 Single event transient current pulse waveform

高能粒子作用于模拟电路时,其表现形式较之于数字电路更复杂,更多样,更加难以预测. 对模拟电路进行加固首先要对其性能和电路特性进行分析与验证,因此,需要对DC-DC 转换器环路的敏感特性 进 行 分 析 与 验 证. 误 差 放 大 器(error amplifier,EA)作为DC-DC 转换器电压环的核心模块之一,将反馈电压VFB与基准电压VREF的差值放大,其输出作为PWM 比较器的反向端输入信号,如图1 所示. 同时,EA 为环路提供足够的增益,保证反馈调节的精度.系统稳态下,当EA 输出共模电平由于ASET 的影响产生变化时,会导致PWM 比较器输出宽窄脉冲,进而导致占空比D 发生变化,引起输出电压VOUT产生较大的波动或VOUT纹波电压增加.

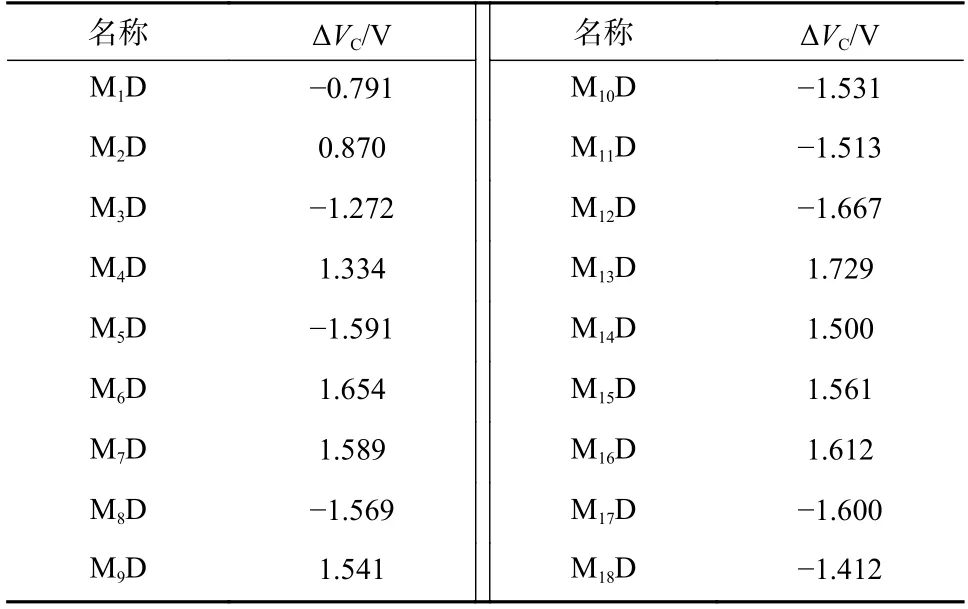

根据上述分析,需要对EA 的敏感节点进行确认. 图3 是本文所采用的EA 结构,将瞬态电流脉冲注入到该误差放大器的敏感节点展开了分析验证.通常情况下,单粒子敏感节点是包含反向偏置pn 结的节点,这是由于pn 结耗尽区的强电场可以非常有效地收集电荷. 根据注入节点为pmos 管或nmos 管注入不同方向的瞬态电流[11],表1 列出了EA 输入电平VFB=VREF正常偏置下,在全部反偏pn 结节点注入瞬态电流后,观察到的EA 输出共模电平跳变情况.

图3 误差放大器结构Fig. 3 Error amplifier topology

表1 EA 注入ASET 电流时输出变化情况Tab. 1 Output changes when EA injects SET current

当粒子轰击EA 各个节点并产生ASET 时,结合表1 的数据,轰击M12漏极时产生的上脉冲跳变幅度达到最大值1.667 V,轰击M13漏极时产生的下脉冲跳变幅度达到最大值1.729 V,最终确定EA 的输出节点是对单粒子最敏感的节点. 这是由于EA 输出节点与频率补偿电容相连接所导致的.

为了确定加固方案,进一步确认了ASET 对系统环路的影响. 在系统等效环路(如图4 所示)中进行了单粒子瞬态电流脉冲注入,在不同负载条件下,验证了ASET 对输出电压VOUT的影响. 分别在0、10 mA、55 mA、100 mA 和150 mA 负载下进行了验证分析,仿真结果表明(如图5 所示),随着负载电流的增大,ASET 对VOUT的影响更加恶劣. 对于相同能量的ASET,VOUT的恢复时间基本相同,约为35 μs. 图5 的波形是在系统等效环路上验证的,主要反应了ASET 与负载电流的关系,VOUT的变化量只反应随负载电流增大,注入相同能量ASET 的变化趋势.

图4 系统等效环路Fig. 4 System equivalent loop

图5 不同负载下等效环路验证结果Fig. 5 Results of equivalent loop validating under different loads

如图6、图7 所示,给出了150 mA 负载下,本文在系统环路中验证ASET 时观察到的宽窄脉冲现象和PWM 比较器的脉冲缺失现象.

图6 150 mA 负载下宽窄脉冲现象Fig. 6 Wide and narrow pulse phenomenon under 150 mA load

图7 150mA 负载下输出脉冲缺失Fig. 7 Output pulse missing phenomenon under 150 mA load

由图6、图7 可观察到,宽窄脉冲现象和脉冲缺失现象并非同时出现. 在650 μs 时刻向EA 输出节点注入ASET 瞬态电流,当PWM 比较器响应EA 输出节点变化时,导致PWM 比较器提前翻转,进而出现宽窄脉冲现象,如图8(a)所示,可以解释这一现象.而PWM 比较器中所出现的脉冲缺失现象可解释为:如图8(b)所示,当输出电压VOUT响应EA 变化持续掉电后(这需要持续一段时间),导致反馈电压VFB低于基准电压VREF而使得VC被拉高且VSIGMA持续一段时间低于VC,使得PWM 比较器未翻转.

图8 波形分析Fig. 8 Waveform analysis

2 单粒子加固设计方法

本文提出的抗单粒子瞬态效应加固电路框架如图9 所示. 通过一级模拟缓冲器隔离EA 输出节点与采样开关、采样电容CS之间的连接. 当DC-DC 环路正常工作时,采样开关每100 个时钟闭合一次,刷新采样电容CS上的电荷,以保证采样电容CS上的电压保持不变,并将该电压VCS作为基准电压接入加固电路正向端. 加固电路的反向端直接与EA 的输出节点相连接,用于检测ASET. 加固电路将VCS与VC进行比较,VCS大于VC时,加固电路提供一路灌电流为EA 节点充电;反之,加固电路提供一路拉电流为EA节点放电. 通过快速充放电加速EA 节点ASET 瞬态电流的释放,以缓解ASET 对EA 输出共模电平VC的影响,从而达到加固目的.

图9 电路级单粒子加固电路框架Fig. 9 Circuit level single event RHBD circuit framework

如图10 所示,给出了抗单粒子瞬态加固电路的结构. 其工作原理为:首先通过M1~M24组成的轨对轨运放电路将VCS与VC转化至电阻R1、R2两端,当单粒子轰击EA 输出节点并引发ASET 时,若发生单粒子瞬态下脉冲电流,此时VC小于VCS,电阻R2所在支路的PMOS 管M28导通,由M33~M36组成的加固电路充电支路开始工作,为EA 输出节点提供灌电流Iout1,以快速使其恢复;若发生单粒子瞬态上脉冲电流,此时VC大于VCS,电阻R1所在支路的PMOS 管M27导通,由M29~M32组成的加固电路放电支路开始工作,为EA 节点提供拉电流Iout2,以加速其恢复. 当EA 输出节点未发生ASET 时,M27、M28均截至,此时,电阻R1、R2所在支路的电流完全由M25、M26提供,充放电支路的管子均截至.

图10 抗单粒子加固电路结构Fig. 10 SET RHBD circuit topology

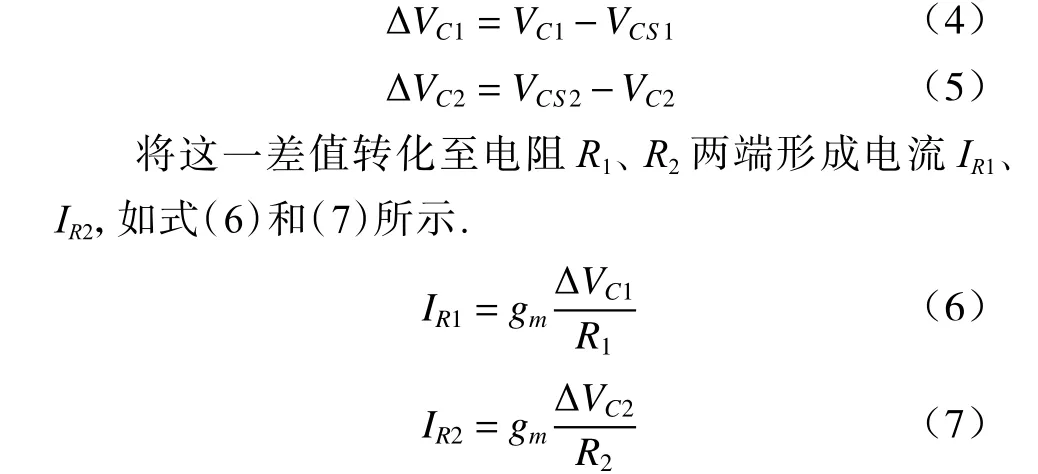

当EA 输出节点遭受单粒子轰击而引发ASET时,其共模电平升高或降低,通过检测其电压跳变量ΔVC,如式(4)和(5)所示.

为了提供一定的裕量,本文将其设置为±15 mV,即只有当IR1或IR2大于Ibias5时,充放电支路才会有一条支路正常工作,Iout1、Iout2的表达式分别如式(8)和(9)所示.

图10 中的加固电路采用轨对轨输入级适应了EA 较大的输出共模范围,拓宽了检测区间. 跨导变化并未引起IR1、IR2线性区间的大幅度变化,能够满足加固需求. 本电路的优点是能够根据检测到的ASET 幅值大小,提供对应大小的补偿电流,实现了自适应补偿效果.

3 加固效果验证与分析

基于0.18 μm BCD 工艺对所提出的电路进行了物理版图设计与全面仿真验证,图11 为芯片的版图照片.

图11 芯片版图照片Fig. 11 Chip layout photo

整体芯片的面积为700 μm×663 μm,其中误差放大器的版图面积为250 μm×117 μm,本文所提出的加固电路面积为263 μm×99 μm. 输入电压为2.9~4.5 V,输出电压为5.9~7.9 V.

为验证所提方案的可行性与创新性,重点对加固前后的环路瞬态进行了详细的测试验证.

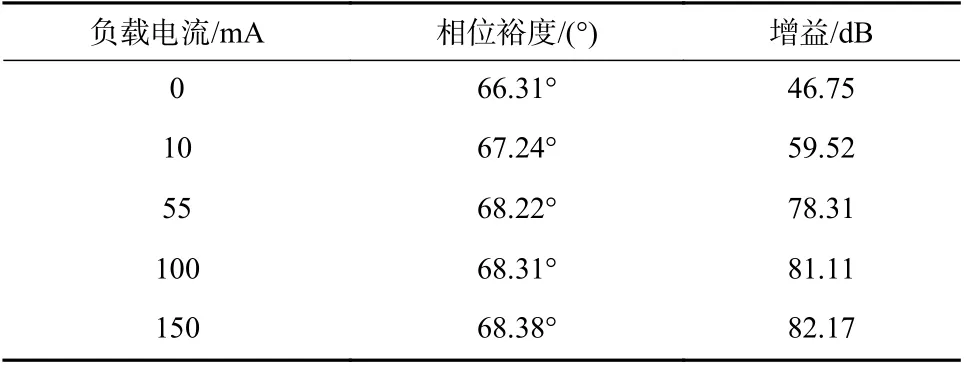

电压环的稳定性体现在输出电压是否振荡,是衡量电压环特性的关键参数之一. 为了验证加固电路对系统稳定性的影响,进行了分析验证,得到了表2和表3 的数据. 表2 是加固前电压环稳定性验证结果,表3 是引入加固电路后电压环稳定性验证结果. 通过对比加固前后数据可知,无论是加固前还是加固后,电压环相位裕度均满足稳定性设计要求. 值得注意的是,随着负载电流的增大,环路增益也随之增大,这可能是随着负载电流增大,ASET 对输出电压VOUT影响越大的原因. 因此,最大负载电流是验证ASET的最坏情况.

表2 加固前电压环稳定性验证结果Tab. 2 Results of normal voltage loop stability

表3 加固后电压环稳定性验证结果Tab. 3 Results of RHBD voltage loop stability

典型情况下,针对不同负载电流下的ASET 进行了加固前后的仿真验证,仿真波形如图12 所示. 随着负载电流的增大,ASET 对输出电压VOUT的影响越来越大,由轻载10 mA 下的2 mV 跳变量增大到重载150 mA 下的10 mV,这与前文分析的结果是一致的.引入加固电路后,系统抑制ASET 的能力显著提升,重载下跳变量最大不超过1 mV,如图12(b)所示. 图12中的仿真结果表明,提出的加固方案能够适应不同负载条件下的ASET.

图12 不同负载下加固结果Fig. 12 Results under different loads

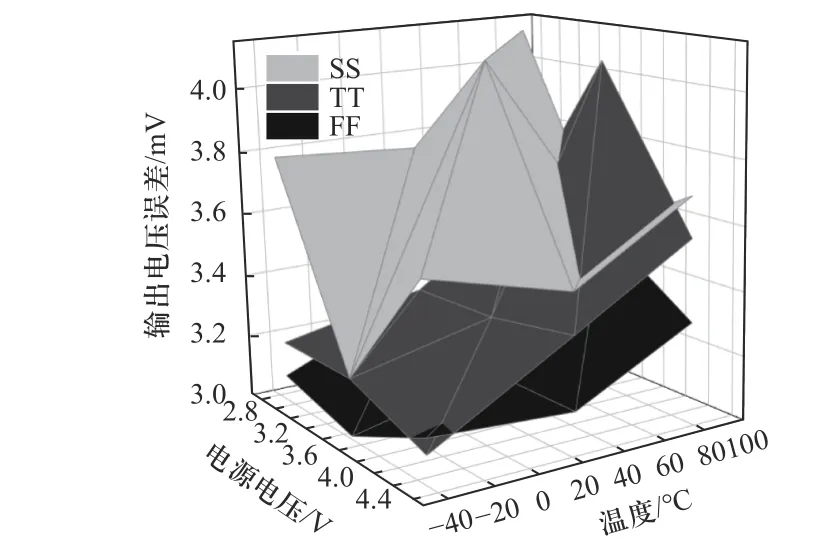

经过前文的分析可知,最大负载电流是ASET 最坏情况. 在这种前提条件下,验证了PVT 变化下的情况,如图13 所示. 随着工艺角从FF 变化到TT 再变化到SS 下,系统受到ASET 的影响越来越严重. 尤其是在SS 工艺角、85 °C、2.9 V 电源电压下,ASET 对输出电压VOUT的影响最恶劣.

图13 在PVT 影响下ASET 对输出电压的影响Fig. 13 The influence of ASET on output voltage under PVT

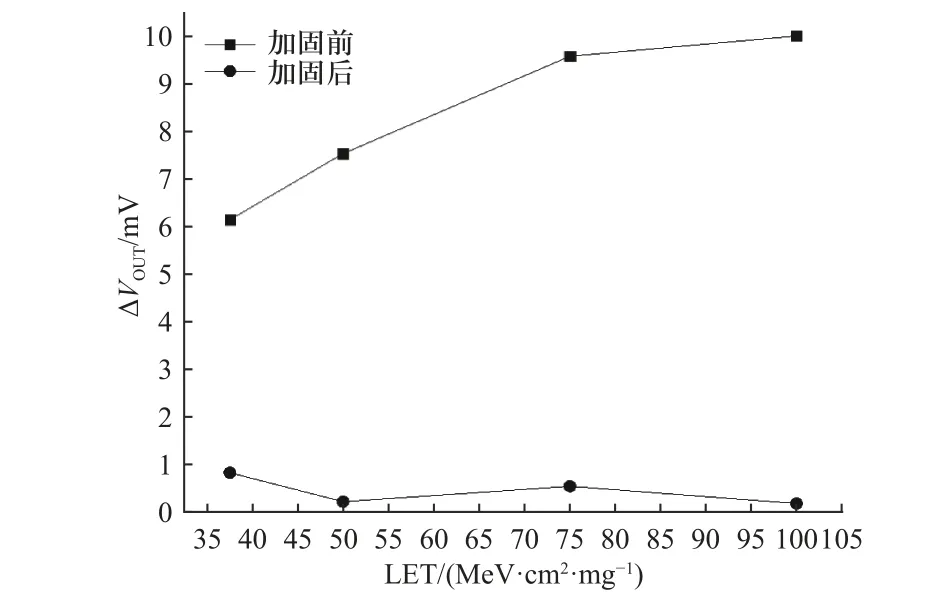

在上述最恶劣情况下,针对不同LET 值,验证了加固电路的加固效果,结果如图14 所示. 这里,定义对单粒子瞬态效应抑制能力σ,如式(10)所示.

图14 PVT 最坏情况下不同LET 值ASET 对输出电压加固前后影响Fig. 14 Influence of ASET on output voltage at different LET and the worst case of PVT

式中:VSET,non是正常情况下注入ASET 输出电压VOUT跳变幅度;VSET,RHBD是加固后注入ASET 输出电压VOUT跳变幅度. 本文所提出的电路最大能够免疫LET=100 MeV·cm2/mg 的粒子轰击产生的瞬态影响. 针对不同LET 的空间粒子,抑制能力达到86.07%以上,LET=100 MeV·cm2/mg 时抑制能力最佳,达到97.70%.

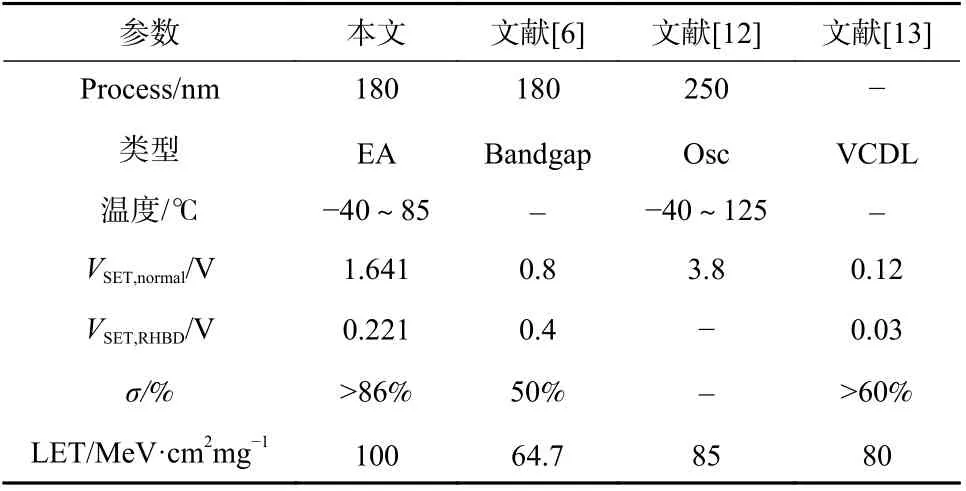

表4 列出了本文所提出电路的加固效果与文献[6]、文献[12]、文献[13]的对比. 本文提出的加固电路对ASET 的抑制能力优于文献[6]、文献[13];WANG 等[12]设计的振荡器并未缓解SET 产生时所引起的电压幅度变化,而是提出了一种双互锁存结构RS 触发器,同时对栅极尺寸进行了设计,提高了临界电荷,并且引入了三模冗余技术和施密特触发器,最终还利用了版图级加固方法才消除了SET 对输出的影响;本文提出的电路能在LET=100 MeV·cm2/mg下正常工作,优于上述文献.

表4 文献对比Tab. 4 Literature comparison

4 结 论

本文对DC-DC 转换器中的单粒子瞬态特性进行了分析,研究了单粒子瞬态对环路响应的影响. 根据分析验证结果,提出了一种电路级ASET 自动检测与加固电路. 通过检测单粒子瞬态电压跳变量并将其转化为动态补偿电流参数对敏感节点提供灌电流或拉电流,根据不同大小的电压变化转换为对应电流,实现了对不同单粒子能量下的自适应检测与加固. 最后基于0.18 μm BCD 工艺完成电路设计与全面验证,结果表明本文所采用加固电路可以抑制ASET对Boost 型DC-DC 转换器的误差放大器节点的影响,能够抵抗LET=100 MeV·cm2/mg 的单粒子轰击,输出电压VOUT的波动最大不超过1 mV,抑制能力达到86.07%以上.