双肖特基势垒型异或非可重构场效应晶体管研究

2022-09-02靳晓诗

王 妍,靳晓诗

(沈阳工业大学信息科学与工程学院,沈阳 110870)

1 引言

在当前集成电路的发展中,MOSFET的尺寸已缩减到10nm节点,这也伴随而生了功耗、制造、物理和芯片成本等技术问题[1-2],可重构晶体管(RFET)便应运而生了。RFET可通过改变外加电压的极性来控制沟道内部载流子的极性,实现器件N型与P型之间的转换[3],相当于单个器件有了两个器件的功能,从而能够使用更少的晶体管来实现功能更复杂的电路[4-6]。依据RFET特殊的工作方式,在此提出一种新型的可重构晶体管,仅通过一个晶体管就实现集成电路中异或非逻辑功能[7-8],能够极大简化异或非门电路的复杂度。

2 器件结构与工作原理

与传统的可RFET不同,新设计的器件采用源区和漏区双层具有肖特基势垒的阻挡型接触结构,在源区或漏区缩减至纳米级尺寸时,结合栅电极的共同作用,即可使器件实现异或非功能。在简化异或非门电路结构的同时,确保集成电路在极端尺寸下可以稳定工作。无论两个栅极中哪个为主控栅极,哪个为辅助栅极,都可获得更高晶体管输出工作一致性,功耗需求也更小。

新设计器件可称为双肖特基势垒型异或非可重构场效应晶体管(BSBRFET),其结构图如图1所示。此处以N型为例,源极和漏极分别位于结构两侧,源极为梯形结构,位于左侧,漏极为矩形,位于右侧;浮动源极为正八边形结构的一半,嵌在本征半导体中。源极、漏极和浮动源极都直接与半导体接触,形成肖特基势垒。栅极有两个,其一为位于中间的栅极(CG),分两部分,隔着栅极绝缘层靠在浮动源极右半边的前后两侧,其长度与浮动源极相同;另一个为两侧的栅极(PG),由四部分构成,分别隔着栅极绝缘层靠在源极的前后两侧(长度长于源极一倍,隔着栅极绝缘层与浮动源极左侧齐平)和隔着栅极绝缘层靠在距离漏极左侧5nm处的前后两侧。

图中,LS、LD分别源和漏的长度;tox为栅极氧化物的厚度;LSF是源和浮动源极内硅区域的长度;LFD是浮动源极到漏极内硅区域的长度;LF为浮动源极长度;WSO为源极到栅极绝缘层宽度;WSI为硅体的宽度;TSI为硅体的高度。

图1 新设计BSBRFET结构图

金属和半导体接触形成肖特基势垒。由于需要的输出工作的一致性更高,肖特基势垒要位于禁带中央位置,设置为等于。以N型为例,能带示意图如图2所示。

图2 新设计BSBRFET能带图

如图2(a),主栅极PG和辅助栅极CG都处于正向偏置,电子空穴对在源极与半导体接触处发生带带隧穿,流向中间浮动源极处,并在浮动源极与右侧半导体接触处再次发生带带隧穿,导带中的电子流到漏极,器件从而导通。

如图2(b),主栅极PG反向偏置而辅助栅极CG仍然保持正向偏置状态,中间由带带隧穿产生电子空穴对,然而由于主栅极反向偏置,电子流向金属一侧,在价带留下空位,形成空穴堆积状态;又由于正向偏置的辅助栅极产生势垒阻挡,可有效防止电子流过,因此大量反向偏置漏电流在此被阻拦。

3 晶体管特性分析

为验证该结构的性能,通过Silvaco TCAD软件进行模拟仿真,验证BSBRFET的特性。仿真采用的物理模型包括迁移率模型、俄歇复合模型、Shock-Read-Hall模型、带隙变窄模型、标准带带隧穿模型和Boltzmann统计模型。

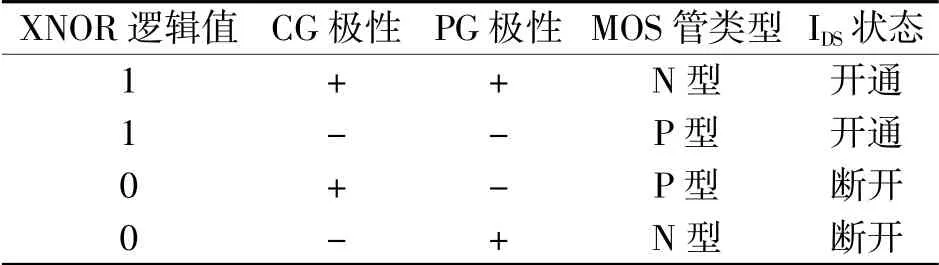

3.1 XNOR逻辑功能

在源极和漏极之间施加电势差,通过对CG和PG同时施加负电压,即两个栅极同时处于“0”状态,利用本征半导体的左右两侧在高电场强度的作用下所产生的隧道效应,使得带正电的载流子——空穴可以从源极和漏极之中处于电势较高的一端流向电势较低的一端,晶体管处于导通状态,即“1”状态。

在源漏极之间存在电势差时,对CG和PG同时施加正向电压,即同时处于“1”状态,同样由于隧道效应,使得带负电的载流子——电子可以从源极和漏极之中处于电势较低的一端流向电势较高的一端,晶体管处于导通状态,即“1”状态。

同样,在源极和漏极之间施加电势差,再对CG和PG同时施加彼此相反的电压,即一个处于“0”状态,一个处于“1”状态,利用当中处于“1”状态下的那一个来阻挡半导体隧道效应导致的空穴载流子流动,同时利用处于“0”状态的一个来阻挡半导体隧道效应导致的电子载流子流动,使器件处于关断状态,即“0”状态。

通过上述操作,即可实现异或非(XNOR)逻辑功能:两个栅极作为XNOR门的两个输入,漏极电流作为输出;正电压为“1”,负电压为“0”;器件导通为“1”,截止为“0”。器件的操作类型(N或P)也取决于两个栅极和漏极的极性。整体逻辑功能的实现情况如表1所示。

表1 实现XNOR运算的BSBRFET状态表

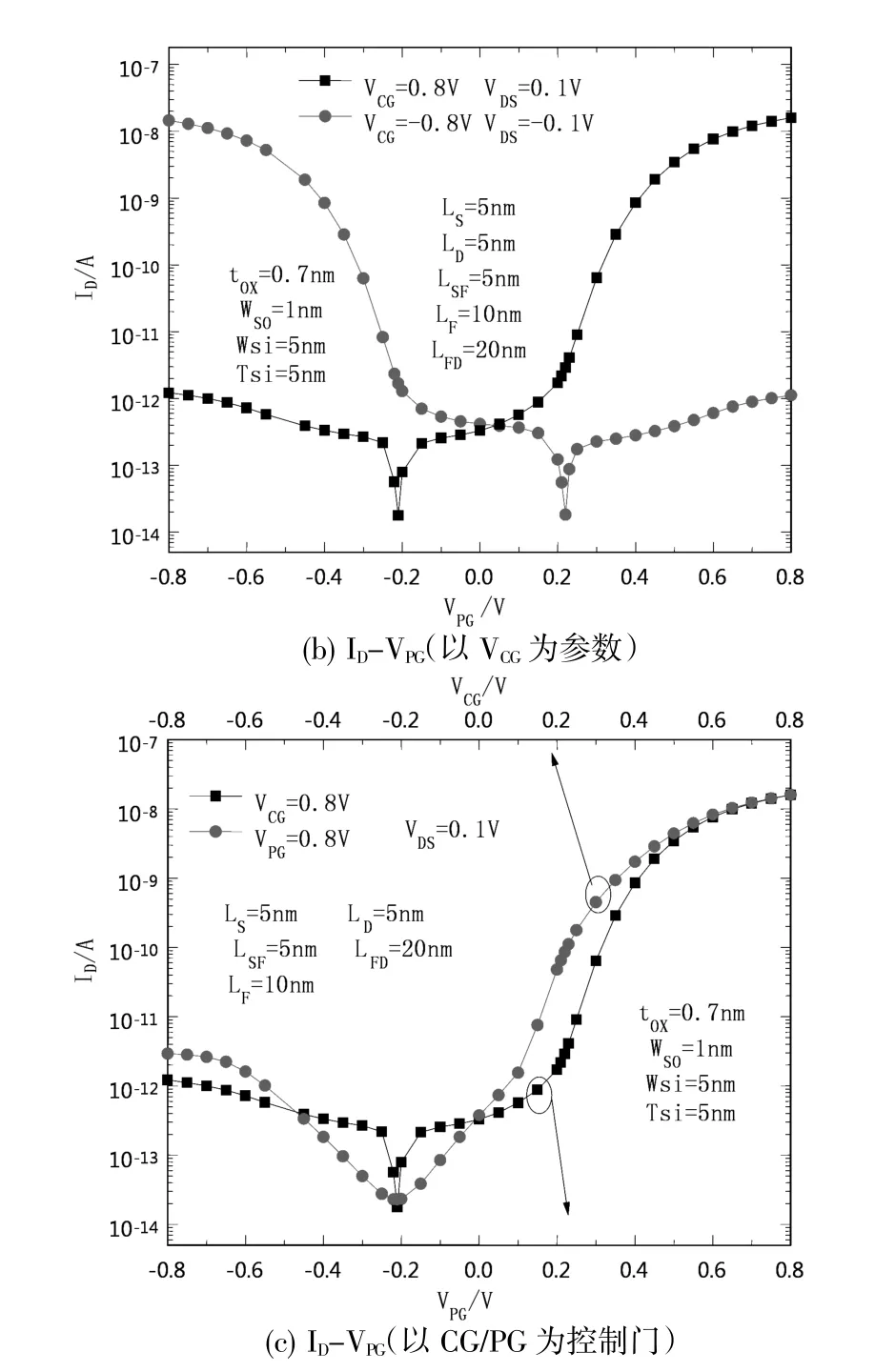

3.2 输出特性一致性功能

传统的RFET中当两个栅极分别作为控制栅极时,导通机理是不同的,其一是MOS导通,另一个是肖特基势垒导通。MOS导通需要在沟道内形成反型层,而电子在反型层具有电阻的特性,使得在小范围内相同电压下的导通电流更小。

BSBTFET中两个栅极分别做控制栅时,导通机理都是肖特基势垒带带隧穿导通。电压相同时,能带弯曲程度相同,电子隧穿数量相近,导通电流接近,曲线输出一致性高。

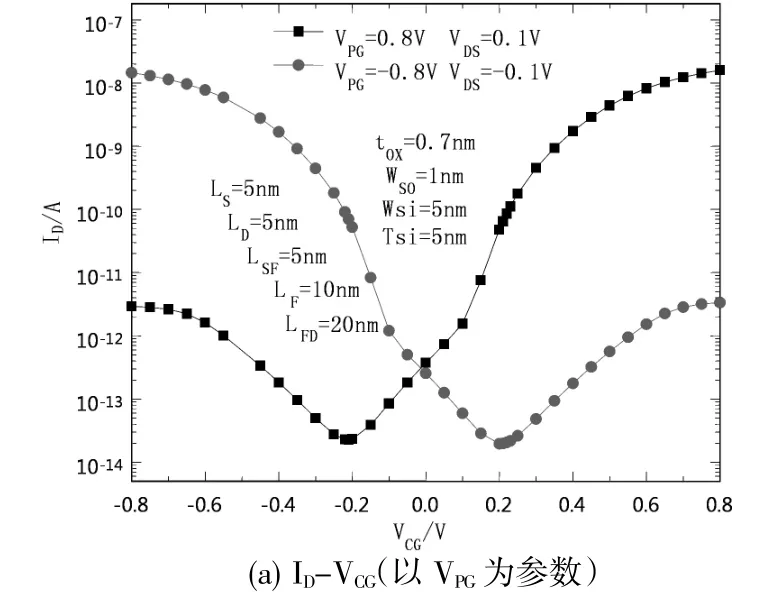

仿真最终得到一系列以栅压作为参数的转移特性曲线,如图3所示。

图3 以栅压为参数的转移特性仿真曲线

图3(a)、图3(b)所描述过程,对应了XNOR功能的实现;在图3(c)中,ID-VCG/ID-VPG曲线重叠程度高,这是因为不论对于PG与CG哪一个控制门,设备的传导机制都是基于肖特基势垒的隧穿,导通机理相同,输出特性就趋于一致。

4 结束语

有着全新设计结构的双肖特基势垒型异或非可重构晶体管,是对现有RFET产品的一次成功的改进,它在单个器件结构中完全利用肖特基势垒隧穿效应导通机制,实现了XNOR逻辑门功能。新设计BSBRFET的输出工作一致性更高,同时还具有高导通电流、低亚阈值摆幅、小漏电流、高灵敏度和高集成度等优点,具有广阔的应用前景。