一款10 bit斜坡发生器的研究与设计

2022-08-17赵鹏

赵鹏

(榆林学院信息工程学院,陕西榆林 719000)

随着CMOS 图像传感器的广泛应用,各大高校和研究机构都对CMOS 图像传感器进行了大量资金投入和研究[1-4]。而ADC 作为CMOS 图像传感器中的核心模块,自然得到了高度的关注。其中列并行结构的单斜ADC 因其结构简单、易于扩展而得到广泛的应用[5-8]。斜坡发生器作为单斜ADC 结构中最重要的模块,其能否产生线性度较好的斜坡电压对整个ADC 至关重要。故该文基于单斜ADC 的结构,设计了一款粗分电流源加细分电流源的分段型10 bit斜坡发生器,电路主要由电流源及开关阵列、输出电路和校准电路构成。

1 电路设计

斜坡发生器,也即数模转换器DAC。根据处理信号的不同分为电流型、电压型、电荷型。该文采用的是目前应用最为广泛的电流型电流舵DAC[9-11],其根据电流源权重不同可以分为两种:二进制编码电流舵DAC 和温度计编码电流舵DAC。二进制编码方式虽然所需电流源数目较少,但随着转换位数N的提高,最大电流源和最小电流源的精确匹配很难实现。温度计编码的电流源匹配容易实现,但随着转换位数N的增加,电流源数目成指数增长,从而占用太多的芯片面积。故该文设计的DAC 采取分段方式,整体电路结构框图如图1所示。根据文献[12-13]可知,温度计编码部分所占的最佳比例为60%~70%,故该文设计10 bit 斜坡发生器的编码方式为低4 bit二进制编码和高6 bit温度计编码。

温度计编码的电流源为粗分级电流源,其大小为16IU,共64 个,其中63 个为6 bit 温度计编码方式控制,剩下1 个粗分电流源为4 bit 二进制编码的电流源提供电流,IU为电流源的最小单位。每个粗分电流源在流入负载之前,都经过校准电路进行校准。然后根据输入数字码的不同控制,不同的温度计码电流源和二进制码电流源分别流入到负载电阻RL上形成输出电压,输出电压通过一个P 型输入缓冲器来增加输出驱动能力,同时通过合理设计运放参数,把输出电压移位到后续电路所需的合适的电压范围,如该文设计所需要的DAC 的斜坡范围为0.5~1.3 V。

1.1 电流源及开关电路设计

对电流舵DAC 来说,电流源对整个DAC 性能至关重要,电流源的匹配和理想度对INL 和DNL 有决定性的影响。

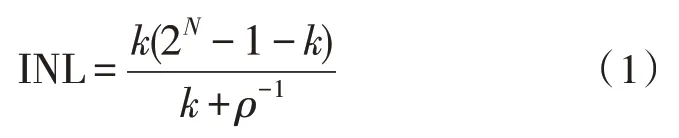

根据文献[14-16]可知,有限的输出阻抗和斜坡发生器的静态性能有如下关系:

其中,N为转换位数,k为电流源的个数,为负载电阻RL与单位电流源有限输出阻抗R0之比。从上述公式可以看出,ρ越小,即电流源的输出阻抗越大,INL 和DNL 越小,系统的线性度就越好。

有限的输出阻抗和DAC 的动态性能的关系如式(3)所示:

由式(3)可知,负载电阻每增大一倍或N每增加一位,SFDR 都会下降6 dB。

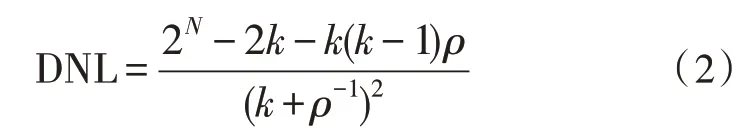

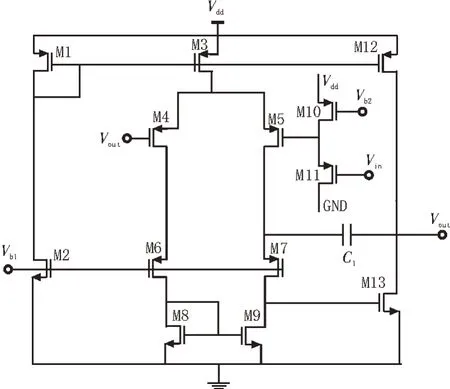

根据上述公式可知,电流源的输出电阻对斜坡发生器的静态和动态性能都有很大的影响,其输出电阻越大,电路线性度就越好。所以该次电流源结构采用的是共源共栅电流源结构,以此来提升电流源的输出电阻,增加电路的线性度。因传统电流源开关的开启和关段,不可避免地引起电流源输出节点电压的变化,从而改变电流源的源漏电压,进而改变偏置电流,影响整个电路的线性度。为此,该文提出了一种带有电流调节功能的改进型电流开关。电流源及电流源开关电路整体结构如图2 所示。

图2 共源共栅电流源及开关电路结构

Q1和Q2是共源共栅电流源结构,增大电流源的输出电阻。Q3和Q4组成了改进型电流源开关电路,这种开关结构和普通的双开关电路的区别是晶体管Q4的栅极并不进行切换,直接连接至偏置电压Vdc上,其值由偏置电路决定。这样Q3和Q4就构成了全差分的开关对。通过Q3栅极输入时钟的高低来控制电流是流入地还是负载。这种结构中,由于节点A的电压与Vout无关,而是由偏置电压Vdc、偏置电流和晶体管Q4的栅源电压共同确定,从而确保整个电流源的源漏电压与输出电压无关,始终保持恒定,因此电流源的输出电流也保持不变。该设计中共有5 种电流源,即粗分电流源16IU,二进制权重电流源8IU、4IU、2IU和IU,IU即带隙基准电路输出的参考电流,不同的参考电流源大小只需要调整电流源尺寸即可实现,粗分电流源在输出之前还需经过校准电路的动态校准,来实现各个粗分电流源之间的精确匹配。

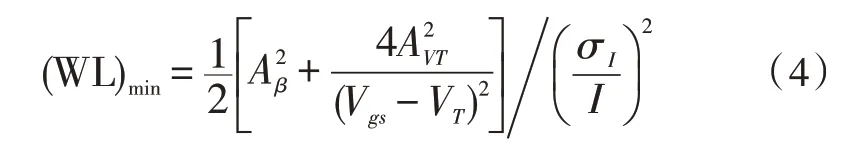

晶体管的面积和工艺参数的关系如式(4)所示:

式中,参数AVT、Aβ是与工艺有关的MOS 管参数,I是电路中实现的最小单个基本电流源的电流,σI是基本单位电流源设计时所要求的标准差。从式(4)可以看出,电流失配与电流源面积(WL)成反比关系,构成电流源的MOS 管面积越大,其实现精度也就越高,电流失配就会越小,但是MOS 管面积的增大,又会导致电流源中寄生电容的增大,会使电路速度降低,同时也会使整个芯片的面积有所增大。这就需要在确定电流源管子尺寸时,在失配、速度和面积之间综合考虑,确定合适的电流源尺寸比。

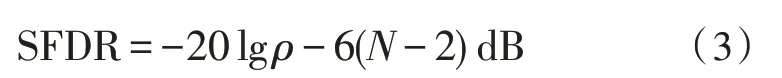

1.2 输出驱动电路设计

该文设计的输出电路主要作用是增加输出驱动能力和调整DAC 的斜坡输出范围到后续电路合适的电平范围。采用PMOS 共源共栅作为电流源,在负载电阻RL上形成电压,负载电阻RL一端接地,理论上最低电压为0,故需采用PMOS 源级跟随器来提高输出电压至合适的范围。该文采用PMOS 输入源级跟随器和共源共栅放大器组成单位增益缓冲器来实现驱动电路,电路结构框图如3 所示。

图3 输出电路结构图

其中,M10 和M11 构成PMOS 的源跟随器,把DAC 的输出电压平移至后级电路接收的合适范围,通过把输入PMOS 管M10 单独做在一个n 阱中,然后将其衬底和源极连接在一起来消除其体效应。所以该电路中的源极跟随器有更好的线性度。M3~M9 构成了共源共栅放大器,连接形式为单位增益缓冲器形式,增加了信号的驱动能力,其余MOS管为偏置电路。

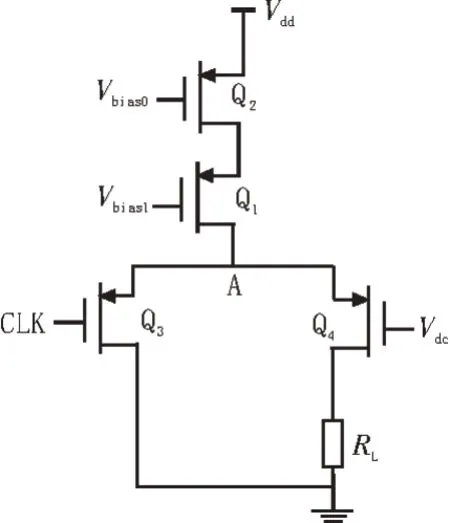

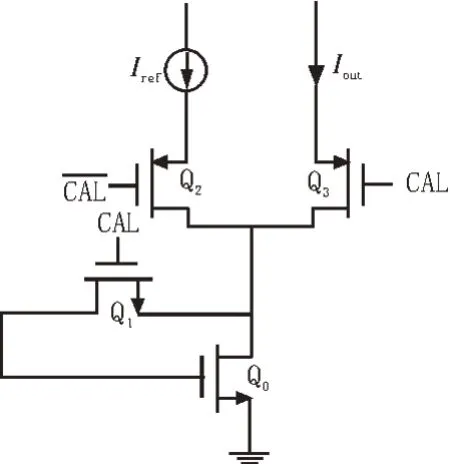

1.3 校准电路设计

对于分段电流型DAC 来说,粗分电流源的匹配性能对整体DAC 的精度起着决定性的作用。虽然粗分级电流源阵列中MOS 晶体管的对称版图布局可以提高精度,但是在标准CMOS 工艺中,基于器件匹配性能来提高精度的效果并不十分有效。因此,必须利用一些校准技术来实现粗分级电流源的精确匹配。故该文只对每个粗分电流源在流入负载之前,采用动态匹配电流源技术进行校准。具体校准电路结构原理如图4 所示。

图4 单个电流源校准原理图

在校准周期内,信号CAL 为高,Q1和Q2导通,Q3关断。因此参考电流源Iref流过Q0,其为二极管连接形式,会在Q0的栅源电容Cgs上形成电压Vgs,这个电压的大小依赖于具体晶体管的尺寸,需根据系统时序要求合理设计。当CAL 为低,Q1和Q2关断,Q3导通,由于Q0的栅源电容Cgs的存在,导致其栅源电压不会立即消失,仍然存储在其Cgs上。由于Q0的漏极电压保持不变,其漏极电流也就等于参考电流源Iref。该漏极电流作为输出电流Iout进行输出。完成校准后可以保证每个粗分电流源Iout都和参考电流Iref保持一致,从而保证了DAC 的精度。

2 仿真与测试

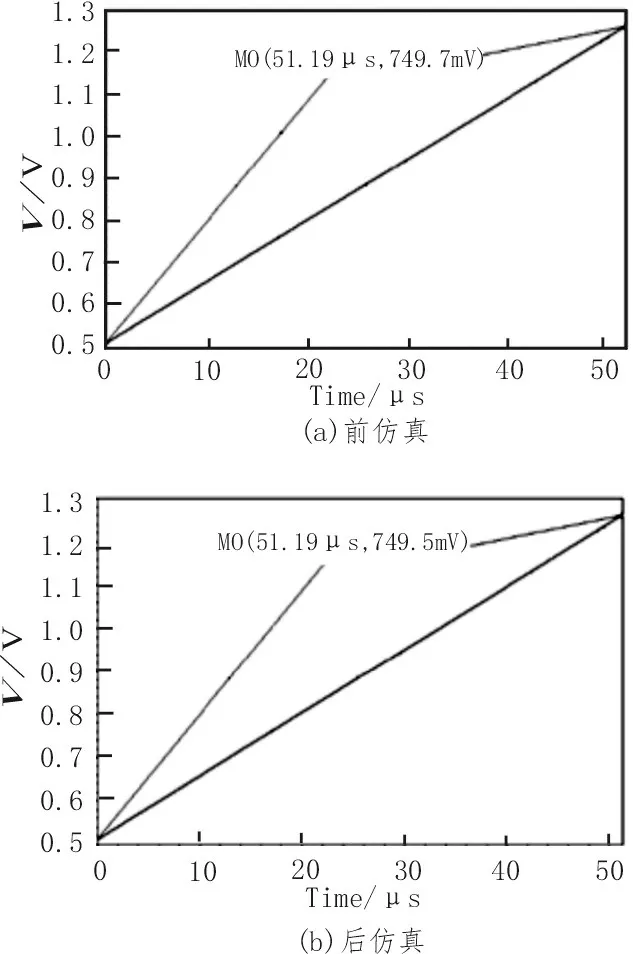

在UMC0.18 μm CMOS 工艺下对斜坡发生器进行设计,用spectre 仿真工具对斜坡发生器的输出特性进行仿真测试,结果如图5 所示。

图5 输出特性仿真

图5(a)为DAC 的前仿真输出特性图,从图中可以看出,在整个斜坡输出周期中,前仿真输出差值为749.7 mV,整体斜坡输出范围在0.5~1.3 V 之间,满足设计要求。图5(b)为后仿真输出特性图,从图中可以看出其输出差值为749.5 mV,整体斜坡输出范围在0.5~1.3 V 之间,满足系统要求。对DAC 的静态特性进行仿真,结果如图6 所示。

图6 斜坡发生器的静态仿真

从图6 中可以看出,DNL 为-0.012~+0.095 LSB,INL 为-0.012~+0.008 LSB,满足系统要求。对斜坡发生电路进行版图绘制,并进行相应后仿真,结果如图7 所示。

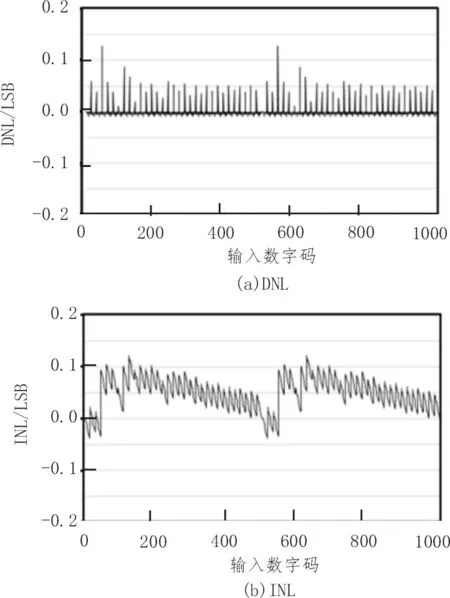

图7 斜坡发生器静态后仿真

从图7结果可以看出,DNL为-0.005~+0.135 LSB,INL 为-0.045~+0.115 LSB,满足系统要求。

3 结论

该文设计了一款适用于CMOS 图像传感器中单斜ADC 的10 bit 斜坡发生器。该斜坡发生器采用粗分电流源加细分电流源的分段方式。针对粗分电流源,电路采用动态校准技术,对流入负载的每个粗分电流源进行动态校准。为了提高单位电流源的输出阻抗,电流源采用共源共栅电流源结构。为了改善开关切换对电流源输出节点电压的影响,提出了一种改进型电流源开关电路。在UMC0.18 μm CMOS工艺下设计实现了提出的DAC 电路。采用spectre对电路进行仿真验证,前仿真DNL 为-0.012~+0.095 LSB,INL 为-0.012~+0.008 LSB。对电路进行版图绘制,提取寄生参数后仿真,DNL 为-0.005~+0.135 LSB,INL 为-0.045~+0.115 LSB。表明该DAC 具有良好的线性度,满足高精度单斜ADC 的需求。