一种用于红外焦平面阵列的读出电路设计

2022-08-17杨海钢

郑 宾,杨海钢

(1.中国科学院 空天信息创新研究院,北京 100094;2.中国科学院大学,北京 100049;3.山东产研集成电路产业研究院有限公司,山东济南 250001)

采用红外焦平面阵列的成像系统已经被广泛应用于军事国防和民用领域[1-2],读出电路是该系统的重要组成部分,一方面读出电路连接红外探测器,给其提供稳定的偏置电压;另一方面读出电路输出的电压信号提供给A/D 转换器进行模数转化,可提高读出电路的噪声抑制能力以及信号处理水平,有利于提升系统成像的质量[3-6]。随着第三代红外探测器的提出,大规模、低功耗、低噪声的读出电路成为了研究热点[7]。

文献[6]采用SFD 结构作为读出电路的像素单元,该结构构造简单,不能给探测器提供稳定的偏置电压,进而会产生非线性响应[6]。文献[8]采用具有相关双采样功能的放大器以便抑制噪声,该结构较为复杂,具有较大的面积和功耗[8]。针对以上问题,文中采用CSMC 0.18 μm 工艺设计了一种低噪声、高线性度的红外焦平面阵列读出电路。该设计采用带有注入管的DI 结构作为像素单元,因此可以给探测器提供稳定的偏置电压。同时,该设计简化了相关双采样电路结构,在降低电路噪声的同时减小了功耗与面积,具有一定的应用价值。

1 读出电路架构设计

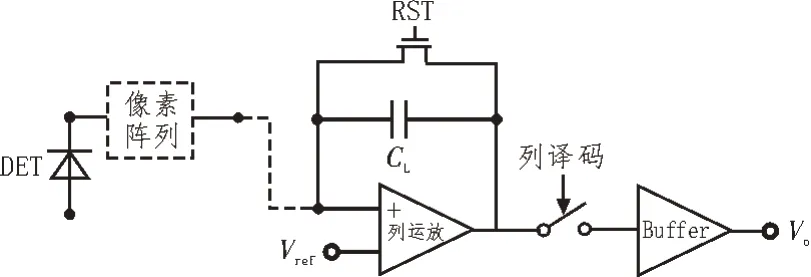

图1 所示为传统的读出电路原理图[9],其中,模拟通路包括像素阵列、列信号处理模块和输出缓冲电路。光子探测器将获取到的光信号转换成电流信号,并输出给读出电路。读出电路中的像素单元对电流信号进行电流-电压转换后,输出电压信号给列信号处理模块。信号经过放大后通过输出缓冲电路输出。

图1 传统读出电路原理图

常见的像素结构包括直接注入(Direct Injection,DI)、电容反馈跨阻抗放大器(Capacitance Trans-Impedance Amplifier,CTIA)、源级跟 随(Source Follower Device,SFD)等结构。CTIA 结构由运放和积分电容构成,具有很高的注入效率和稳定的探测器偏置,但是运放的存在使得面积以及功耗较大。SFD 结构简单,具有较低的功耗和噪声,但是探测器的偏置电压会随积分电压变化而变化,从而造成非线性变化。该设计采用DI 结构作为像素单元,DI 结构具有结构简单,可以给探测器提供稳定的偏置电压的优点。

由于制造工艺的限制,像素单元会产生非均匀现象,导致不同像素的输出结果存在一个固定偏差。这种偏差也被称为固定模式噪声(Fixed Pattern Noise,FPN)。同理,列读出电路也会因FPN 噪声导致不同列之间存在差异。对于传统的读出电路,像素单元的输出仅通过运放进行信号放大处理,进而通过输出缓冲器输出到片外,这种结构不能抵消掉FPN 噪声带来的影响。

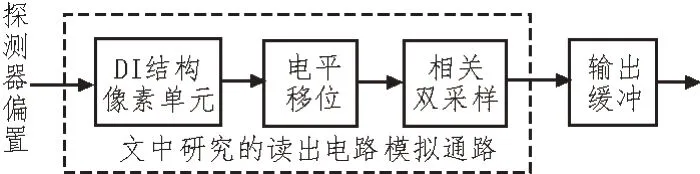

文中提出了一种新颖的读出电路模拟通路,该通路可以在减小电路面积的同时,消除存在的FPN噪声,其结构如图2 所示。

图2 文中提出的读出电路原理图

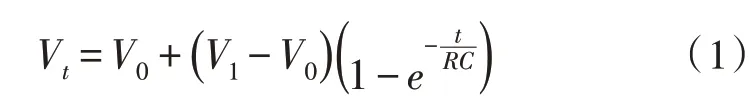

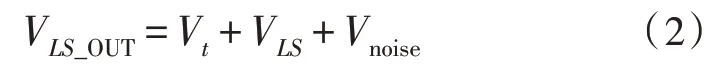

首先采用DI型像素单元将探测器产生的电流信号转化成电压信号,再通过电平移位器对信号进行移位处理,提高其整体幅值。由于积分电流值非常小,积分电压也较小,因此提高电压值有利于抵消噪声带来的影响,最后通过相关双采样电路消除电路中存在的FPN 噪声[10-11]。读出电路整体架构可以等效为简单的数学模型,像素单元电容积分公式为:

其中,Vt为t时刻电容上的电压值;V0为电容初始电压值;V1为电容最大可充到的电压值。经过电平移位器进行电压移位后,输出的电压为:

其中,VLS为电平移位器整体移位的电压值,Vnoise是像素单元中存在的FPN 噪声值。当电路正常工作时,相关双采样结构输出值与上述电压相同:

当电路进行复位时,相关双采样结构输出值为:

最终电路的输出电压为:

此时系统输出的电压消除掉电路中存在的FPN噪声,同时也提高了有效信号的幅值,有利于信号的后续处理。

2 读出电路模块实现

2.1 像素单元的设计

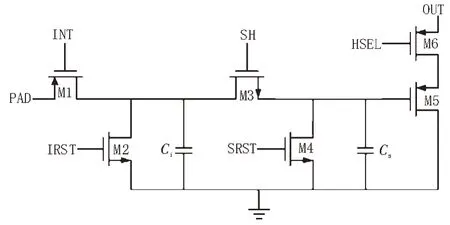

光子探测器生成的积分电流信号由光电流和暗电流组成。其中光电流与光子探测器本身的特性和光通量有关,是一个常量;暗电流则会受偏置电压的改变而呈非线性变化[12]。因此,探测器偏置电压的稳定程度决定了其输出电流的线性度。文中通过在DI 型结构像素单元内增加选通管的方式来提高线性度。图3 为DI 结构电路图。

图3 DI结构电路图

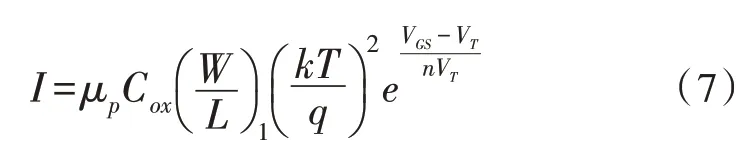

图中PAD 端与探测器阵列对应单元相连接,探测器生成的电流信号经此流入像素单元;INT 信号控制注入管M1 使其工作在亚阈值区;IRST 和SRST分别是积分电容和采样电容的复位信号;当SH 信号导通时,积分电容Ci上的电荷流入采样电容Cs;M5为源跟随器;HSEL 为选通管。当M1 管处于亚阈值区时,其漏电流计算公式如下[13]:

其中,μp是PMOS 管迁移率;Cox为单位面积的栅氧化层电容;W/L为宽长比;VT与kT/q相等;VGS为栅源电压;VDS为漏源电压。当T=300 K 时,VT≈0.026 V。VDS增加到远大于VT时,上式可以化简为:

可以看出此时漏电流的大小不随漏源电压而变化,因此,当积分电容上的电压变化时,漏电流的大小不改变,从而探测器的偏置电压不会变化。

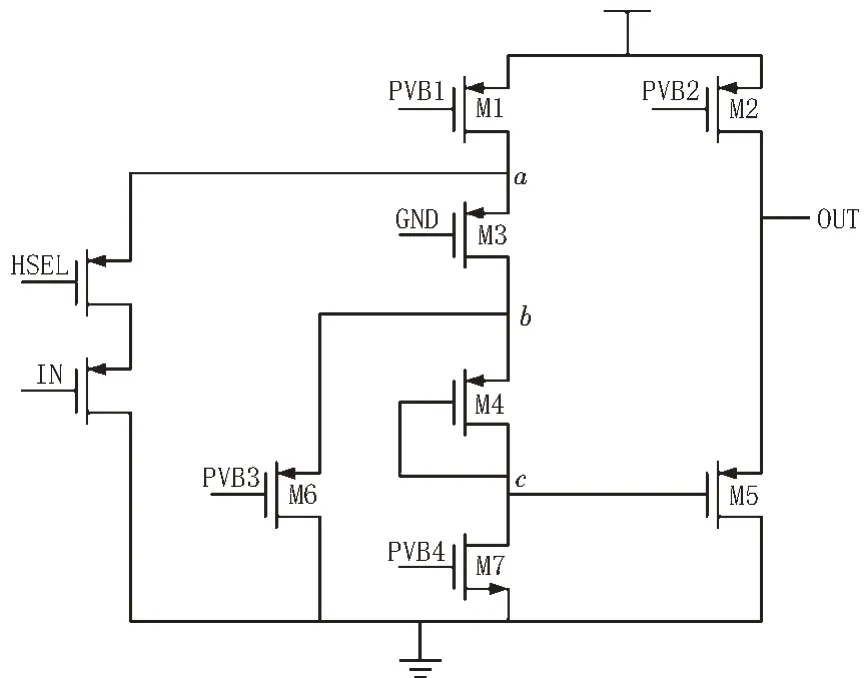

同时,由于MOS 器件电容值会伴随偏置电压的改变而改变,为了提高该电路的线性度,积分和采样电容采用无源器件MIM 电容。对于源跟随器,与NMOS 器件相比,PMOS 器件有良好的线性度以及抑制噪声能力,因此该电路采用PMOS 作为源跟随器。源跟随器具有输入电阻大、输出电阻小的特点,具有良好的输出特性。对于M5 管,假设其负载电阻为RL且无穷大时,其增益如下[14]:

由此可见,当源跟随器处于饱和区时,具有良好的线性度。

该电路输入电流在皮安(pA)级,要保持读出电路的增益,积分电容值要非常小。出于提高增益以及降低电路噪声的考虑,采用的电容值为Ci=65 fF,Cs=32 fF。源跟随器也会引入1/f噪声,可通过增加其面积来减小噪声。最终采用的尺寸为(W/L)5=1.8/1 μm,(W/L)6=3.9/0.8 μm。

2.2 电平移位器的设计

电平移位器作为像素单元的缓冲电路,可以帮助信号在后续电路中快速建立,并隔绝前后级电路以防止互相影响[15]。该设计通过控制电流的线性变化,从而控制电压的线性输出,可以大幅度提高输出电压的摆幅,同时也保证了较高的线性度。

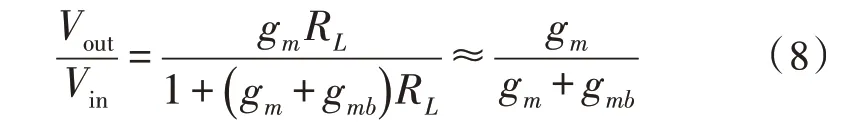

图4为该设计采用的电路图。其中,PVB1-PVB4是偏置信号,用来控制MOS 管的工作状态以及其漏电流大小,使得电流线性变化;M1 管提供上拉电流,M7 管提供下拉电流;M3 管作为隔离管,避免节点a与节点b直接相连;M4 管用作负载;M5 源级跟随节点c输出。

图4 电平移位器电路图

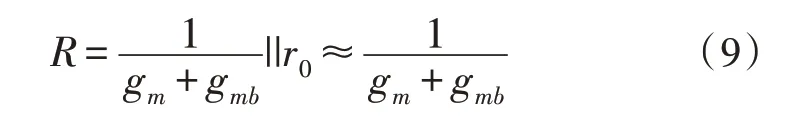

电路输入部分即为像素单元内部的源跟随器,当电路正常工作时,电流从节点a流入电平移位器,使得原本电流受到变化,从而节点c的电压发生变化,由M5 管跟随输出。当像素单元输入不同的电流值时,M5 管即输出线性变化的信号。由式(3)可知,为了具有良好的线性度,M5 管需要工作在饱和区。对于M4 管,其阻抗计算公式为:

因此,当流经M4 管的电流线性变化时,c点电压也呈线性变化。出于减小1/f噪声以及提高驱动能力的考虑,源跟随器M5 的面积较大,该设计采用的尺寸为(W/L)5=19/1.8 μm。

2.3 相关双采样电路的设计

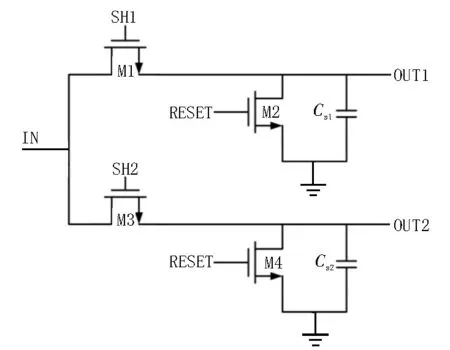

经过分析可知,DI 像素单元会带来FPN 噪声以及非均匀性误差的问题,相关双采样结构可以很好地解决该问题[16]。图5 为文中采用的相关双采样电路结构图,该结构由两组MOS 开关和电容构成。

图5 相关双采样电路结构图

首先RESET 端输入有效信号,M2 和M4 管导通,电容Cs1和Cs2进行放电复位。当像素单元内采样保持电压进行复位时,M1管导通,其输出信号存储在Cs1中;当像素单元内进行采样保持时,M3管导通,其输出信号存储在Cs2中,则OUT2-OUT1即为系统最终输出信号值,此方法可以消除电路中存在的FPN噪声。

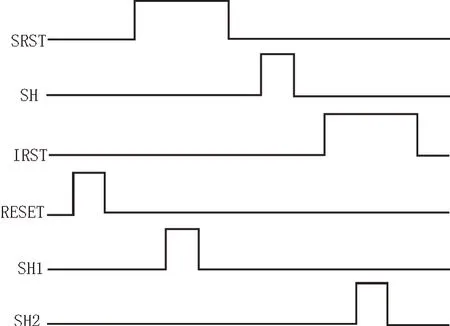

图6 为系统一个周期的工作时序图,像素单元采用边积分边读出模式工作,SH1 和SH2 信号分别在SRST 和IRST 信号有效时,给予高电平。其中电路元件的选取:M1 与M3 采用PMOS 器件,Cs1和Cs2采用MIM 电容,以便提高电路的线性度。(W/L)1=(W/L)3=1.8/2 μm,以此增强输入能力,Cs1=Cs2=32 fF,使得电流快速积分,提高电路的增益。

图6 系统工作时序图

3 仿真结果与分析

该设计采用CSMC 0.18 μm 3.3 V 工艺进行设计,利用spectre 工具进行功能验证以及仿真。在输入电流为500 pA 时,在1~100 kHz 频率范围内对电路进行噪声分析,得到电路输出电压噪声频谱图如图7(a)所示。通过计算可得,在此期间累计输出噪声电压为150 μV。

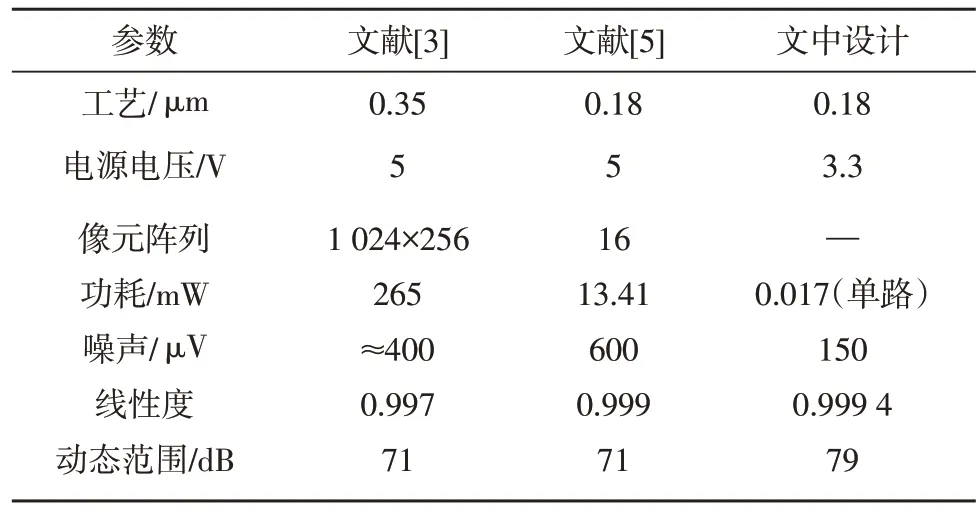

通过对输入电流60~500 pA,间隔10 pA 线性变化进行瞬态仿真,测得OUT2 端电压输出值。对输入电流和OUT2 端输出电压值进行线性拟合,验证系统的线性度。线性度拟合效果图如图7(b)所示。通过曲线可以观察到线性拟合效果较好,利用函数计算拟合线性度为0.999 4。表1 给出了该设计仿真参数值以及与几种读出电路的对比情况,可以看出,该设计的线性度与对比文献相同,输出噪声及功耗相比于其他设计具有一定的优势。

图7 仿真结果图

表1 该设计与几种读出电路的仿真参数对比

4 结论

文中采用CSMC 0.18 μm 3.3 V 工艺设计了一种应用于红外焦平面阵列读出电路的模拟通路结构。该结构主要包括像素单元、电平移位器和相关双采样电路,有效地抑制了FPN 噪声,并且具有很高的线性度。测试结果表明,在输入电流为500 pA 时,电路输出噪声为150 μV,线性拟合度0.999 4,动态范围为79 dB,为电路后续进行数字化输出提供了实现可能。