Q波段氮化镓功率放大器芯片

2022-08-17王海龙

王海龙,崔 亮

(中国电子科技集团公司第十三研究所,河北 石家庄 050000)

0 引 言

毫米波段雷达系统受大气成分的低衰减特性影响,广泛应用在30 GHz以上的频段,其射程主要取决于射频(Radio Frequency,RF)功率放大器的输出功率。先前系统中使用的砷化镓(GaAs)功率放大器受材料的限制,工作电压较低,输出功率一般在几瓦特,效率不高。近年来,氮化镓(GaN)器件迅速发展,其性能远远超过砷化镓器件[1]。氮化镓功率放大器具有更高的工作电压和输出阻抗,使得匹配网络的设计更容易,同时具有更高的效率[2]。而高输出功率的毫米波段功率放大器作为毫米波段雷达系统的重要部件,其工作在发射通道的末级,主要对前级微小射频信号进行功率放大和发射,用于微波通信和遥感测控等领域[3-5]。本文设计实现的GaN功率放大器芯片是在0.15 μm GaN 假态高电子迁移率晶体管(Pseudomorphic High Electron Mobility Transistor,pHEMT)单片工艺线上制作完成,采用有耗匹配、电感电容匹配网络以及4级级联放大等技术设计电路,利用仿真软件进行电路优化、电磁场仿真以及芯片版图设计。

1 功率放大器设计方法

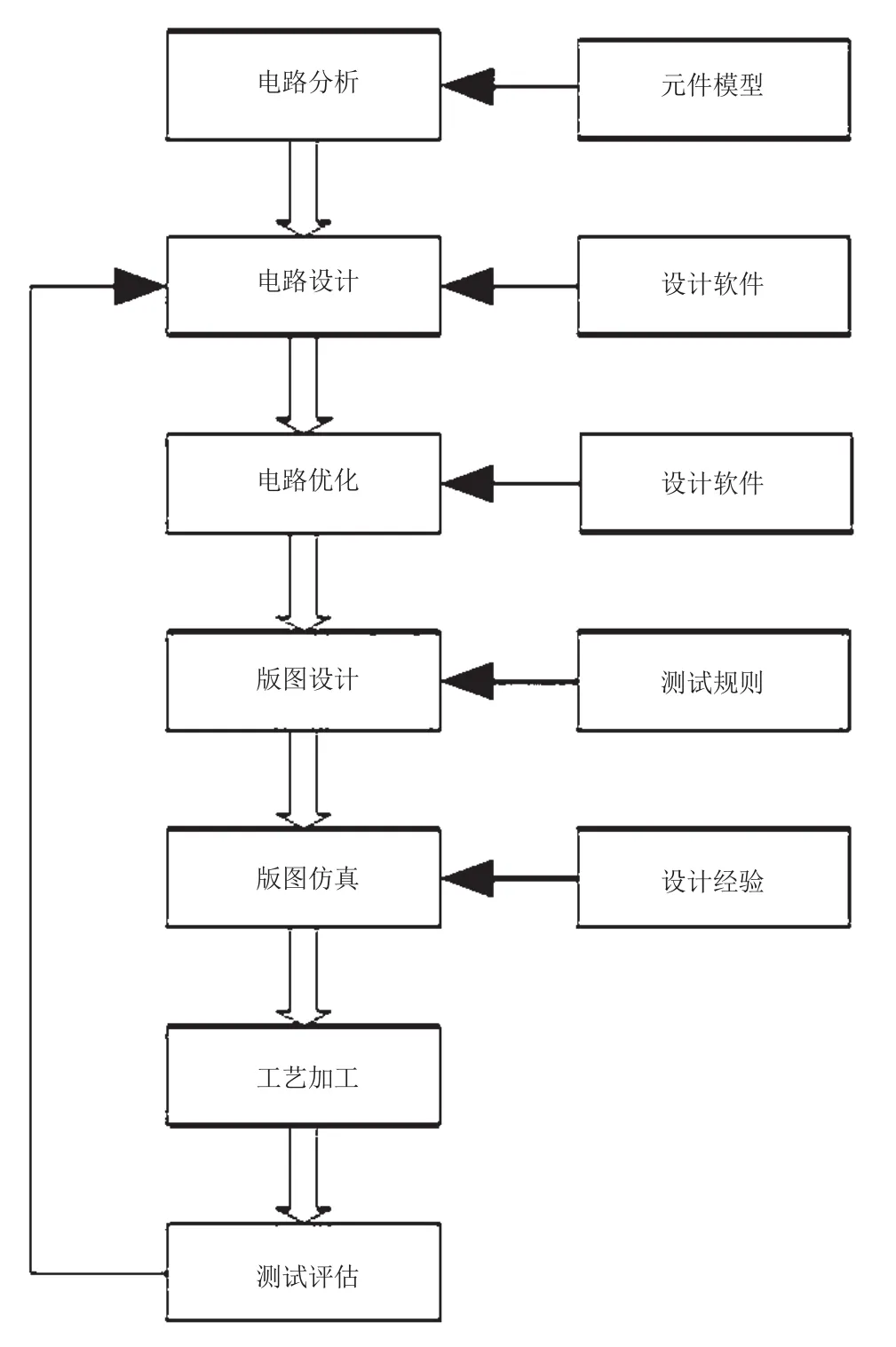

设计GaN单体微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)功率放大器,整个电路设计的流程如图1所示。

图1 MMIC电路设计流程

(1)电路分析。在确定芯片工艺种类后,仿真该单片工艺下不同晶体管尺寸pHEMT器件的直流与射频性能,确定晶体管使用的偏置条件,规划芯片电路拓扑结构。

(2)电路设计。利用电路仿真软件对所选择的晶体管进行源级负载牵引与漏极负载牵引,仿真出晶体管的最佳源极阻抗与漏极阻抗后,用工艺库中的器件模型设计晶体管之间的匹配网络。通过改变匹配网络中的各元器件参数值,确保电路在全工作频带内可以稳定工作。

(3)电路优化。搭建晶体管之间的匹配损耗电路后,综合考虑级间增益、输出功率及功率平坦度、功率附加效率(Power-Added Efficiency,PAE)、每一级电路的稳定性以及芯片面积等,优化仿真,使整个电路性能达到最优。

(4)版图设计。完成芯片各项射频性能指标仿真后,需要设计芯片版图。绘制Layout时,在芯片面积达到最小的同时应尽量减少各无源器件之间的射频耦合、微带线和微带线之间的耦合串扰以及加电微带线可能交叉的问题,既要保证芯片的射频性能指标,又要确保实际工艺加工上的可实现性。

(5)版图仿真。完成最后的版图排版后,需要对最终版图进行仿真。电路仿真软件有强大的电磁仿真能力,结合射频电路设计师的设计电路经验对版图进行微调,进一步优化芯片射频指标。

(6)工艺加工。当最终的版图在仿真软件中仿真完成后,设计师需要使用专业版图软件准确无误地画出最终的版图,送到Foundry去加工并进行流片。

(7)测试评估。芯片流片回来后,在微波探针台对设计芯片的每项射频性能指标进行评估测试。一旦探针台测试数据不符合设计要求,设计师就需要对芯片进行重新设计改进,直至流片测试数据符合最初的设计要求为止。

2 MMIC芯片设计

功率放大器在实际电路设计中采用4级级联放大,前级选用1个300 μm(单指栅宽为50 μm)的单胞器件,第二级选用两个300 μm(单指栅宽为50 μm)的单胞器件,第三级选用4个300 μm(单指栅宽为50 μm)的单胞器件,第四级采用8个360 μm的单胞晶体管来完成功率合成(总栅宽为2 880 μm),满足10 W功率输出指标要求。采取并联方式可以合理分散晶体管热源,从而降低芯片的热阻,进一步提高器件的可靠性。设计芯片的最终拓扑采用对称结构,芯片输入级和第二晶体管、第三晶体管级间采用低通有耗匹配网络,这样可以扩展带宽,提高芯片的小信号增益。芯片输出级使用带通滤波网络,可以有效抑制2次谐波,在保证输出功率满足要求的前提下,提升芯片的工作效率。除此之外,为了提高本芯片的工作稳定性和小信号增益带内平坦度,4级芯片均采用有耗匹配方法。

3 芯片加工与测试

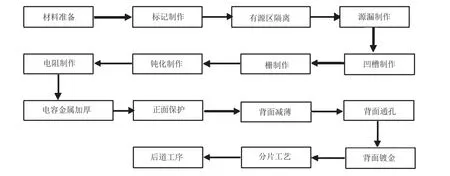

根据产品性能指标要求,本文设计的Q波段功率放大器芯片采用0.15 μm GaN pHEMT芯片工艺,具有功率密度大、批产一致性高等特点。MMIC的主要加工工艺流程如图2所示。

图2 MMIC加工工艺流程

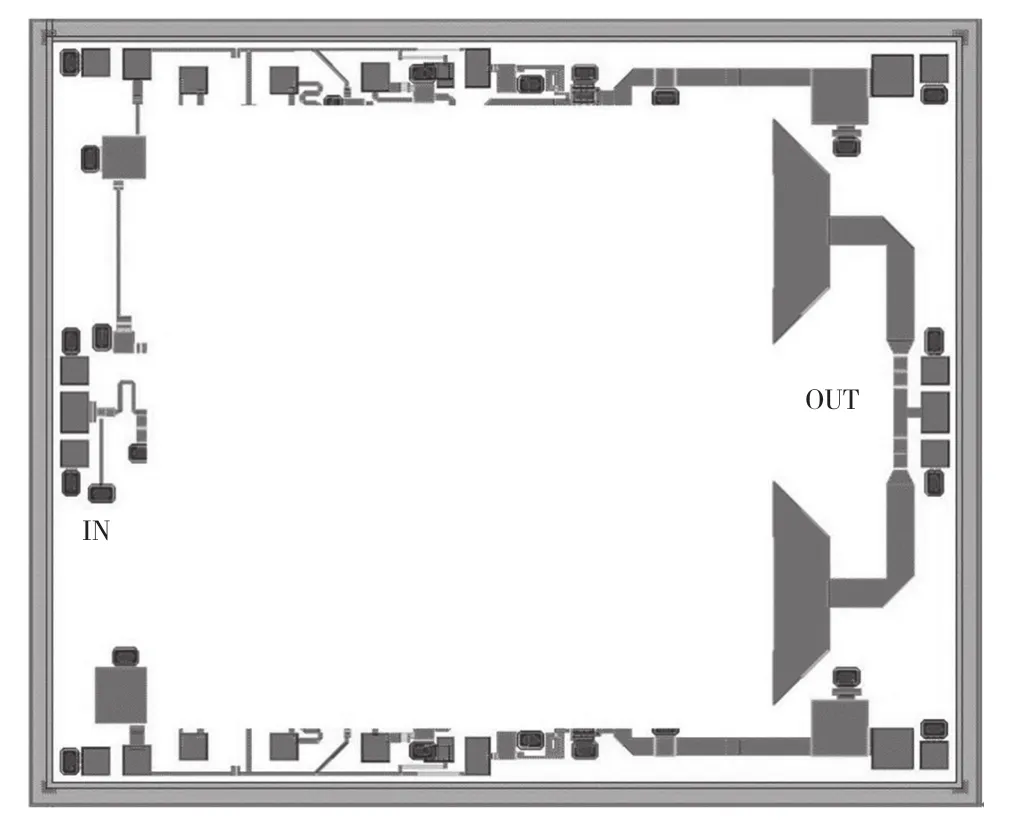

对材料结构进行分析和研究,加强通用工艺能力建设,对器件的制造工艺进行严格控制,通过优化设计生产兼顾线性的高效率、高功率密度GaN HEMT材料,从而获得良好的器件性能。最终的电路版图如图3所示。

图3 芯片最终版图

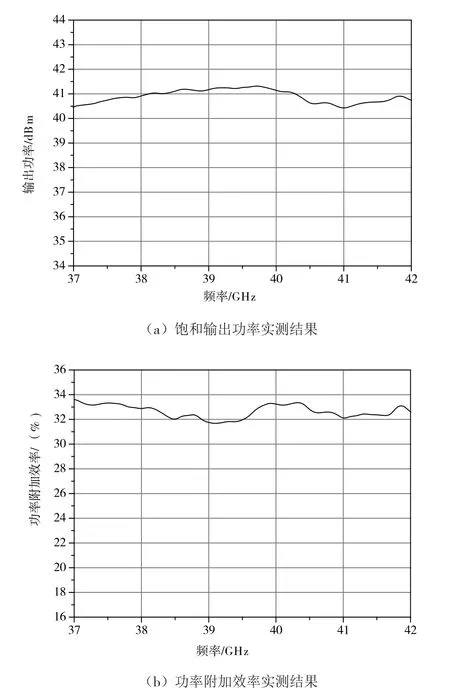

基于GaN pHEMT工艺制作电路,采用氮化硅进行钝化隔离保护。制作电路中使用的芯片电容,对晶圆背面和地孔电镀Au完成元器件接地,降低源电感。设定工作电压为20 V、脉冲宽度为100 μs、占空比为10%、测试频率为37~42 GHz,芯片饱和输出功率实测结果如图4(a)所示,功率附加效率实测结果如图4(b)所示。

根据图4可知,本文研制的功率放大器芯片实测的饱和输出功率大于40 dBm、功率效率大于30%,符合预期目标,应用效果较好。

图4 芯片性能测试结果

4 结 论

基于0.15 μm GaN HEMT单片工艺设计了一款适用于37~42 GHz的波段功率放大器芯片,电路使用4级级联放大的拓扑形式,利用微带线、到地电容实现芯片射频输入级、输出级以及其他各级间的阻抗匹配。该放大器的实际测试结果符合预期,具有一定的参考意义。