基于ZYNQ 的双ADC 数据采集系统的设计与实现

2022-08-15麦超云黄传好刘子明

麦超云,黄传好,刘子明

(五邑大学 智能制造学部,广东 江门 529020)

0 引 言

随着射频传感器在工艺上的突破,毫米波雷达已经应用在不同领域,包括自动驾驶的巡航系统、路面测速及安防方面。不同于目前主流光学摄像头设备,毫米波雷达具备了高精度、抗干扰、全天候工作的特性,在自动驾驶、安防检测等领域具有更加优秀的表现。对毫米波雷达目标检测性能的要求不断提高,导致大量数据需采集和处理,因此对数据传输的实时性要求严苛。

通常在数字信号处理领域,常用的核心器件主要集中于微型处理器,专用DSP 和FPGA。目前一些主流的信号处理核心器件采用STM32 高端单片机等微处理器,虽然该方案功耗低、价格低廉,但是这种架构的数据采集传输方式因为单片机时钟频率较低,导致速率不满足实时数据传输处理的要求,仅仅应用在低速数据采集和对实时性要求不高的场景,同时采集精度误差较大。而另一种方法则是采用DSP+FPGA 架构的平台,FPGA采用并行处理,可大幅度提高数据的采集传输速率,但这些平台接口单一不利于标准化,操作不易随时控制,同时基于FPGA 实现网络传输较为困难,开发难度较大。相较于上述两种方式,Xilinx 公司推出的一款SoC(System on Chip)芯片ZYNQ,其内部可分为逻辑处理(Processing Logic,PL)与处理系统(Processing System,PS)两部分,其中PL 端采用Xilinx 7 系列的现场编程阵列,PS 端则是一块双核ARM Cortex⁃A9 处理器。ZYNQ内部实现了PL 与PS 之间高带宽、高性能的AMBA⁃AXI总线互联,不仅降低了硬件设计难度,而且增加了毫米波大量数据接收传输的稳定性和传送速率。本文采用ZYNQ 的7Z020⁃400 系列芯片,配合2 颗4 路AD9228的ADC 芯片,外加DDR3 内存构成毫米波雷达采集系统。首先利用ZYNQ 逻辑部分编写ADC 控制电路;然后将雷达射频前端的数据经过ADC 采集,并将4 组正交数据通过千兆网口发送到上位机;最后上位机对数据进行处理,获取目标信息。实际测试结果表明,该系统可满足数据传输的实时性和可靠性。

1 系统整体方案

采集系统整体利用上位机通过串口进行控制,可同时配置工作模式及控制系统的启动终止。系统方案如图1 所示。上位机通过串口通信接口将控制命令传送到ZYNQ 的采集板上;指令解析模块将这些指令通过不同的通信方式发送到目的模块,其中内部数据通信采用了双口BRAM,该IP 核将两个不同时钟域的数据进行调制,保证数据的准确性。当射频前端正确配置完毕之后,会返回同步脉冲,此时数据采集模块的状态机捕获该脉冲上升沿,依照配置参数在短时间内完成对中频信号数据的采集和DDR3 内存的写入,当满足采集要求之后触发网口进行发送。上位机控制指令的下发和上传数据的处理。

图1 系统整体方案

2 系统模块设计

结合软硬件的分布和功能,整个系统主要分为4 个模块:射频参数控制模块、系统时钟控制模块、数据存储及传输模块、ADC 数据采集模块。

2.1 射频参数控制

采集系统雷达前端的参数配置指令是通过SPI 协议进行。该射频前端需要同时配置两种参数,一种是其工作方式,包括功放大小设置;另一种则是毫米波发送波形的控制,包括线性调频波的周期、脉冲宽度及带宽配置。ZYNQ 芯片集成2 个SPI 控制器,同时系统要做到上位机随时可控,指令解析模块对上位机串口配置参数进行解析;然后依据射频芯片数据手册,采用SPI 接口按照时序完成相关寄存器的配置。

2.2 系统时钟控制实施方案

为了满足系统长时间稳定的工作,保持信号相位的一致性,系统时钟由射频前端晶振提供,通过ZYNQ 内部时钟管理模块将时钟分别输入到PS 与PL 端。其内部各个模块的时钟分布如图2 所示。

图2 时钟控制实施方案

PL 部分的时钟通过ZYNQ 的DCM 时钟模块将输入的40 MHz 时钟降为10 MHz,作为ADC 的采集频率,同时为了ADC 数据精确对齐,设置一个参考延迟时钟。另外为消除各个模块时钟之间的差异性,通过DCM 将时钟校正,作为数据采集模块的输入时钟,最后数据通过千兆以太网口上传。

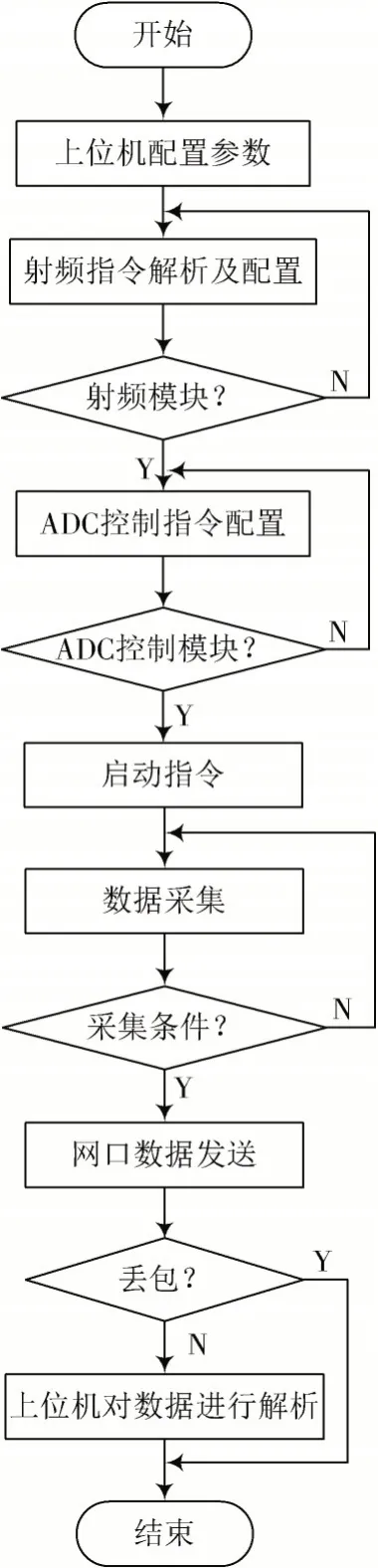

2.3 数据存储及传输模块

数据采集及传输采用状态机的方式,其实施方案流程如图3 所示。具体步骤如下:首先状态机处于空闲状态,等待上位机发送开始指令,如果上位机的指令完整无误通过解析模块传输,则此时空闲状态跳转到判断状态;在此状态会依次判断各个模块是否配置完毕,当满足条件,则进行数据采集,CPU 进而将状态机写入BRAM 里面的数据调入内存中,并触发网口,通过UDP协议上传,上位机也将调用算法模块对数据进行处理。

图3 数据存储及传输流程

2.4 ADC 时钟及数据控制

ADC 负责将前端数据由模拟信号转为数字信号,其采集速度与精度将会影响整个系统的性能。本系统采用2 片AD9228 芯片构成4 对IQ 通道。ADC 控制模块的主要功能是控制ADC 数据与时钟。当雷达的参数配置完成之后,射频前端将返回同步信号脉冲,表示射频前端已配置完成,此时ADC 采集的数据才为有效数据。ADC 时钟与FPGA 接口数据如图4 所示。

图4 ADC 时钟与FPGA 接口数据

ADC 采集数据对时钟要求十分严格,数据的处理是采集系统的关键。AD9228 支持10~40 MHz 采样率,通过FPGA 内部将时钟分频得到10 MHz,通过OBUFG分为ADCClkIn+和ADCClkIn-一对差分时钟,作为AD9228 的输入时钟,同时AD9228 芯片会返回两对差分时钟,分别为数据输出时钟对(DCO+)和(DCO-)以及数据帧输出时钟(FCO+)和(FCO-)。FPGA 在接收ADC 输出的差分串行信号时,需要考虑DCO 边沿与数据边沿所存在的相位差,只有设置合理的时序约束以满足建立时间和保持时间,才能消除亚稳态。同时DCO 也要和FCO 确定相位关系,因为仅靠DCO 采集到的数据虽然是正确的,但只是一串比特流,而不能确定数据的最高位或者最低位,只有通过FCO 进行比特序列调整才可以恢复数据。针对FCO 时钟,利用FPGA 内部可编程IO资源将(FCO+)和(FCO-)时钟转换为一路时钟FCO,再通过FPGA 内部的DCM 资源将FCO 的相位转换为初始时钟120°作为数据输出的最终时钟;对于DCO 路的时钟,首先采用IBUFG 将(DCO+)和(DCO-)数据时钟转换为单路DCO,接着对该路数据进行延迟。AD9228 输出的原始数据也是经过特定的处理,首先将原始差分信号转化为单路信号,然后经过延迟单元IDELAY2,最终通过IDDR 模块,将单时钟边沿改为双边沿输出,此时一个时钟周期内将输出两位数据。处理之后的数据与FCO 的相位基本同步,FCO 的上升沿与数据的最高位对齐。

3 系统整机测试

3.1 硬件测试

为了验证整个采集板卡的工作状态,对系统整机进行了多方面测试。毫米波雷达采集系统的整体硬件组合如图5 所示。该采集系统主要由一个ZYNQ⁃7Z020 芯片,配合2 颗4 路AD9228 的ADC 芯片,外加DDR3 内存构成。利用ZYNQ 逻辑部分编写ADC 控制电路,将雷达射频前端的数据经过ADC 采集并将4 组正交数据通过千兆网口发送到上位机。

图5 采集系统硬件

为了验证该硬件整体的功耗,利用可编程电源提供12 V 电压,设定额定电流1 A,测得采集系统在无射频前端的情景下,功耗为1.116 W,如图6 中电源显示屏所示。当接上射频前端,工作电流达到0.724 A,这时系统功率为8.689 W。当经过8 h 测试,功耗维持在8.6 W附近,表明该系统具有低功耗、稳定的特点。

图6 硬件功耗测试

3.2 实时性测试

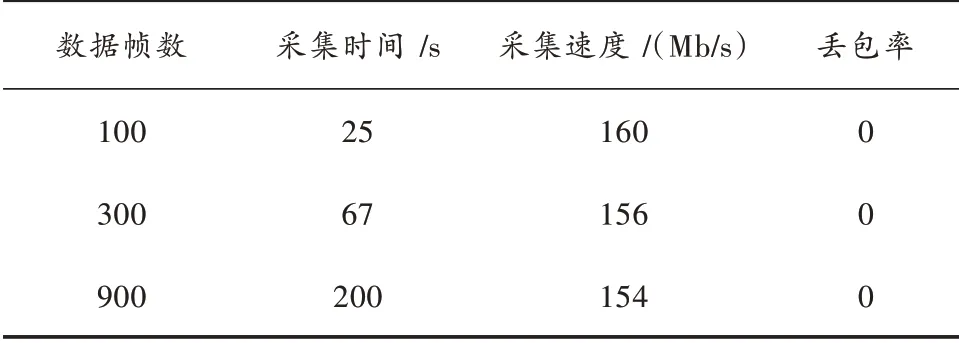

为了验证系统数据传输速率,对千兆网口数据传输速率进行了测试,其数据传输结果如表1 所示。

表1 网口数据传输结果

测试结果表明,该采集系统长时间采集之后,数据传输速率稳定在150 Mb/s,实时性较好,数据丢包率为0。

3.3 采集板卡功能有效性测试

为了验证整个采集板卡的功能有效性,进行实地测试。设置射频前端带宽为5 MHz,脉冲宽度为5 μs,脉冲周期为10 μs,数据采集格式为150 帧,帧间隔为220 ms。具体的参数配置如图7 左边所示,37 ms 静态目标的时域信号及傅里叶频谱图如图7 右边所示。

图7 参数配置及时频图

为了验证环境对毫米波采集的影响,在夜幕下进行实地测试。设置前端带宽为5 MHz,脉冲宽度为5 μs,脉冲周期为10 μs,数据采集格式为150 帧,帧间隔为220 ms。20 ms 左右的动态目标的时域信号及距离多普勒如图8 所示。

图8 测试效果图

通过多次户外测试结果表明,针对24 GHz 毫米波雷达短时间内产生的大量数据,本文所设计的采集系统都能稳定、高速地上传中频回波数据,同时上位机也能实时将数据通过算法处理之后显示目标的相关信息。

4 结 论

本文基于ZYNQ 平台提出了一套适用于24 GHz 毫米波雷达的高速数据采集系统。该系统通过上位机控制界面,能够将相关配置参数通过串口发送至采集板卡,同时针对不同的应用场景控制数据的采集格式,最终通过千兆以太网完成采集数据的上传和处理。测试结果表明:该系统可以满足多种场景下对目标的检测,同时满足实际需求;并且数据传输快、功耗低,在检测方面具有较高的实用价值。