一种宽频段软件无线电平台的设计与实现*

2022-08-01黄忠凡赵文超

李 翔,黄忠凡,赵文超,张 健

(武汉中原电子集团有限公司 研发中心,武汉 430205)

0 引 言

战术通信中,不同电台装备因工作频段、调制方式和通信协议不同而无法实现互联互通。此外,背负式或手持电台由于采用电池供电,其平均功耗决定了在战场的可运作时间。所以,小型化、低功耗、宽频段、可编程是现代化战术通信装备设计的重要目标。

软件无线电技术是解决上述问题的有效手段。它是基于一个开放性、标准化、模块化的通用硬件平台,通过灵活的可编程软件实现多种通信功能[1]。虽然软件无线电的特点主要体现在软件可编程和可升级上,但是其实现功能的多样性要求硬件系统必须具备相应的处理能力。软件无线电硬件平台是处理信号和实现不同通信功能的基础,是使软件发挥出灵活功能的前提,其设计是软件无线电系统的重要内容。

目前,高集成度、小型化、低功耗的软件无线电的硬件平台实现方式主要有三种。

一是采用离散器件,包括射频放大器、模拟混频器、模数和数模转换器以及模拟滤波器等[2],在射频前端采用二次变频的超外差结构。这种结构的优点是灵敏度高、稳定性好,降低了对射频器件的性能要求。但是由于使用了大量的模拟分离器件,导致射频前端结构复杂,一致性差,硬件设计和调试都极为不便。

二是射频集成套片与编程逻辑器件相结合,优点是软件化程度较高、平台小型化,更贴近软件无线电的思想,功耗低,大部分功能可通过软件实现,后续维护和升级成本较低;缺点是支持的通信频段受限于射频集成套片[3]。目前,使用最广泛的是ADI公司的AD9361集成射频捷变收发器,其工作频段为70 MHz~6 GHz。

三是采用射频直接采样,选用很高采样率和较宽输入带宽的转换芯片,优点与第二种方案相似,缺点是随通信频率的提高,对采样率的需求也提高,功耗也随之提高,同时外置滤波器的设计要求也越来越高。

本文在采用基于AD9361实现70 MHz~6 GHz频段信号收发的基础上,进一步通过射频直接采样技术实现70 MHz以下频段信号的收发,设计了一种结构简单、小型化的宽频段软件无线电平台,并通过实验测试验证了该平台的通信效果。

1 硬件平台方案设计

通用硬件平台主要包括由天线、功放、射频前端组成的信道模块和模数/数模转换、数字信号处理组成的数字基带综合处理模块。本设计聚焦于数字基带综合处理模块的设计。

1.1 数字基带综合处理模块总体方案设计

为了构建一种宽频段的软件无线电硬件平台,本设计联合采用了零中频采样技术和射频直接采样技术。数字基带综合处理模块的设计主要包括模数和数模转换功能以及数字信号处理功能的实现。

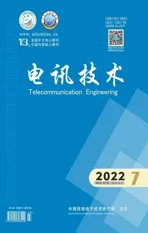

综合处理模块总体方案如图1所示,射频接插件用于实现本模块与信道模块信号的互联。为了减少射频接插件的数量,选用四选一的射频开关将不同频段的收发信号合并成一路射频信号,这样只需一个射频接插件即可实现全频段射频信号的收发。此外,射频开关还用于控制不同频段信号收发的通路,使得70 MHz~6 GHz频段的信号通过AD9361实现收发,70 MHz以下的射频信号通过模数转换芯片AD9467和数模转换芯片AD9142直接收发。数字信号处理模块使用ZYNQ芯片实现数字基带处理、波形控制、系统接口管理等功能。本设计将模数及数模转换部分和基带数据处理集成在一块电路板中,使得平台整体结构更紧凑,适用于小型化通信设备。此外,为了保证模数和数模转换器及数据处理模块的ZYNQ中的现场可编程门阵列(Field Programmable Gate Array,FPGA)时钟同源,由专用时钟管理芯片SI5338生成平台各器件所需的时钟频率,并由一个较低时钟频率的晶体振荡器为时钟管理芯片提供参考时钟,在保证时钟同源性的同时也保证了时钟的品质,实现了高性能的时钟管理。

图1 硬件平台数字基带综合处理模块总体框图

1.2 模数和数模转换模块设计

模数转换是将射频前端模块的射频模拟信号转换成数字信号,数模转换是将经过数字处理模块的信号转换为射频信号。为了简化射频前端的电路设计,模数和数模转换模块综合运用了零中频采样[4]和射频直接采样技术,省去了模拟混频电路,使该平台尽可能接近理想软件无线电的结构。

零中频采样技术直接将天线接收的射频信号混频至基带的 I/Q 两路信号,基带信号首先由数据转换器进行采样和量化,再由数字处理器进行解调。零中频采样由于具有抑制镜频干扰、电路设计简单、易于集成等优点而成为目前最主要的射频信号收发技术。早期的零中频采样技术存在直流偏置和正交误差的问题,ADI公司基于零中频采样技术的射频捷变收发器AD9361因具有直流偏置校准和正交误差校准的功能而受到青睐[2]。该芯片内部除了集成有12位的模数及数模转换器,还集成了模拟射频前端、混频器、频率合成器等众多模块,不仅降低了射频收发模块体积和功耗,而且可以满足当前绝大多数通信制式的需求。由于AD9361的工作频段覆盖范围在70 MHz~6 GHz,要实现与工作频段低于70 MHz的通信设备进行通信,就需要在射频模拟部分增加模拟混频电路,增加了系统设计和调试的复杂度。为了简化系统结构,降低调试难度,本设计对70 MHz以下的信号采用射频直接采样技术。

射频直接采样是直接对射频信号进行数字化处理,无需进行模拟下变频,通过高带宽和高采样率的模数转换器将射频信号直接转换为数字信号,由数字信号处理器进行数字下变频及滤波转换等后续处理。模数转换芯片选用ADI公司的AD9467,可以满足高动态范围无线接收的需求。数模转换芯片选用ADI公司的AD9142,可以产生接近奈奎斯特频率的多载波。

数模和模数转换芯片AD9467、AD9142和AD9361与基带处理芯片ZYNQ之间的数据交互采用低电压差分信号(Low-Voltage Differential Signaling,LVDS)总线连接。模数和数模转换芯片的寄存器配置都是通过SPI(Serial Peripheral Interface)总线来实现,本设计将三个芯片的SPI配置接口挂在ZYNQ芯片PS端的SPI总线上,使用PS部分通过SPI接口可以方便地配置相应寄存器,使其按照需要工作。

1.3 数字信号处理模块设计

数字信号处理模块主要功能包括实现数字信号的处理、平台对外接口管理和通信波形的接入链路控制等。为了降低系统功耗和硬件设计复杂度并有效减小系统尺寸,本设计数字处理模块采用Xilinx公司的高度集成SOC芯片ZYNQ-7000系列芯片中的XC7Z030,其内部集成了嵌入式双核ARM即PS(Programmable System)部分,以及高灵活性与可扩展性的Xilinx FPGA即PL(Programmable Logic)部分[5]。PL部分是采用Kintex -7架构FPGA,具有丰富的逻辑资源,可以满足数字信号处理模块实现高速接口逻辑和复杂运算的需求。PS部分集成了存储器控制器、千兆网口、USB 控制器、SD卡等外设,通过在ARM核上运行操作系统可实现平台对外接口的有效管理。利用PS部分的另一个ARM核可以实现通信波形的接入链路控制。此外,芯片内部集成的AXI高速总线接口最高吞吐量可达到9.6 Gb/s,可以满足PL端数字信号处理模块与PS端波形接入链路控制的高速数据交互的需求。

2 平台软件架构设计

平台软件架构设计是实现不同体制通信波形的核心。通信波形一般由网络管理及上层应用、通信链路控制、数字基带处理和射频控制等组成。各功能模块分别运行在芯片的不同内核中,网络管理及上层应用、通信链路控制、外设驱动和平台对外接口管理等模块部署在PS部分,数字基带处理和射频控制等运行在PL部分。模块化的软件架构设计,降低了各模块之间的耦合度,通过重配置不同的模块,可以方便地实现不同体制的通信波形。平台软件各模块在ZYNQ芯片中的部署情况以及各模块之间的连接关系如图2所示。

图2 平台软件框图

2.1 PS部分软件设计

PS部分软件设计主要完成平台对外接口管理、平台中外设驱动、音频数据采集、上层应用及波形网络管理、通信波形链路控制等功能。平台对外接口主要有以太网、串口、USB接口等,在PS部分的ARM0中运行LINUX操作系统,可以简单实现对这些接口的管理。此外,平台上层应用和波形网络管理以及外设的驱动也都是运行在PS部分的ARM0上(比如语音信号采集芯片),并通过IIS总线采集音频信号。在ARM1中运行裸机程序,实现通信波形链路的控制,PS部分的两个ARM核通过共享内存的方式进行数据交互。

2.2 PL部分软件设计

PL部分软件主要完成数字基带处理、数字上/下变频、模数和数模转换芯片数据的收发逻辑等功能。数字下变频模块主要包括数字控制振荡器(Numerically Controlled Oscillator,NCO)、数字混频器和低通滤波器。NCO产生一个理想的正弦和余弦样本,分别输入到数字混频器与模数转换器输出的射频信号样本相乘,然后经低通滤波器滤除倍频分量和带外信号,经过频段选择就得到基带信号,再进行匹配滤波,这样就完成了正交数字下变频。数字上变频是数字下变频的逆过程,两者的工作原理基本一样,只是处理顺序相反。NCO产生的正弦和余弦样本的质量会直接影响基带处理中的信号解调,设计一个性能好的NCO非常关键,它的性能也就决定了数字上/下变频的性能。本设计中NCO采用Xilinx提供的IP核实现,它可以通过AXI接口配置输出的频率,相位和频率精度可以根据设计需求进行配置,使用简单方便。滤波器及混频器也均采用IP核来实现,保证了设计的可靠性。

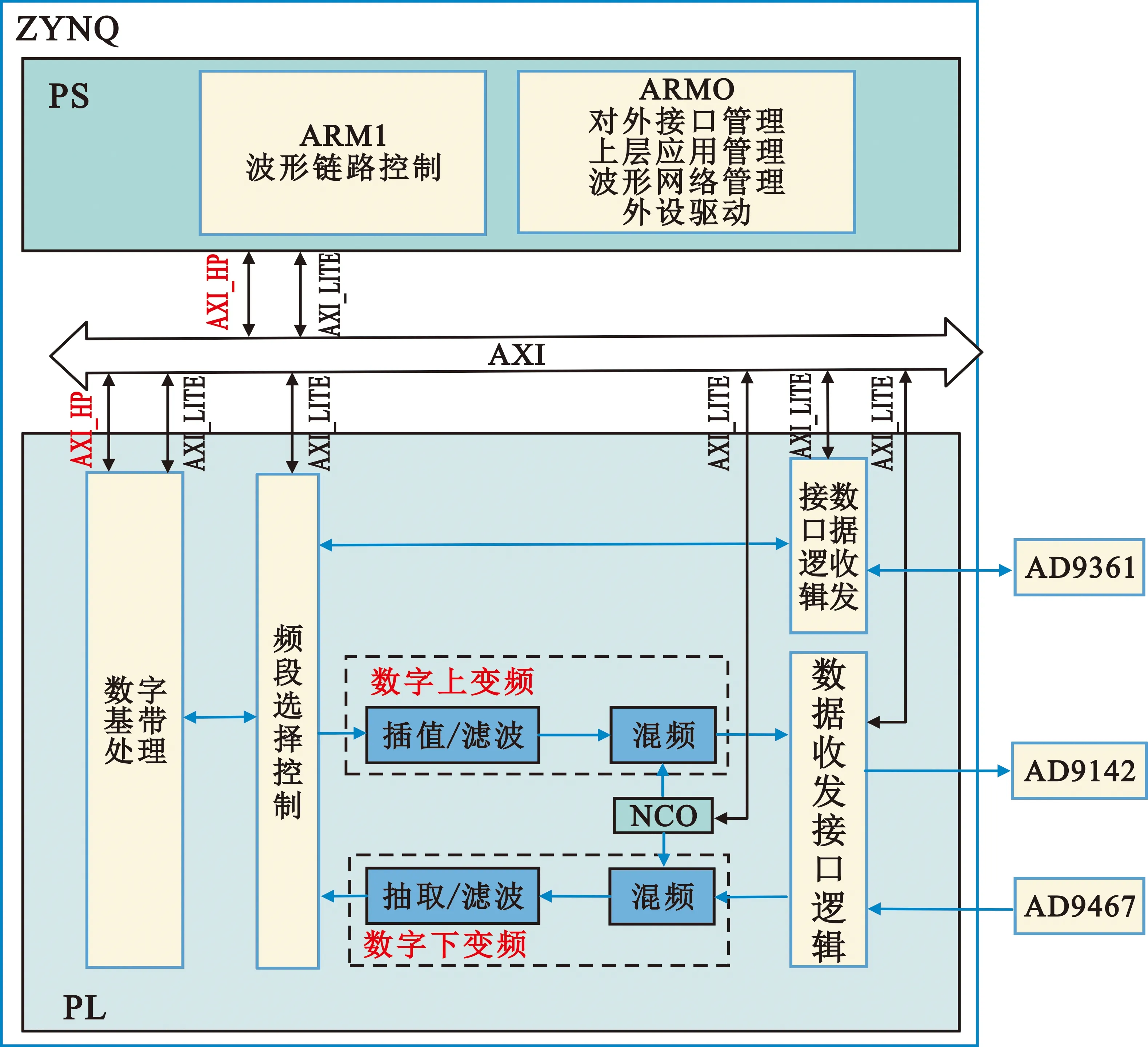

PL部分中模数和数模转换数据的收发需严格按照各芯片的数据接口时序开发相应逻辑控制程序。AD9361的接口时序随工作模式的不同而不同,本设计选用的AD9361工作模式为频分双工(Frequency Division Duplex,FDD)、双收双发(2R2T)、LVDS。发送(或接收)的时序关系如图3所示,双数据速率(Double Data Rate,DDR)实现数据传输,I、Q两路的数据格式按IMSB、QMSB、ILSB、QLSB循环,通过帧控制信号(TX_FRAME)的高低电平来区分两个通道的I、Q数据。AD9467采用8位LVDS总线传输数据,它的16位采样数据分成偶数位和奇数位两组,分别在时钟的上升沿和下降沿输出。AD9142采用16位LVDS总线传输,FPGA向AD9142提供数据传输时钟,在芯片的字格式传输模式下,时钟的上升沿和下降沿分别传输I、Q两路数据。

图3 AD9361发送时序

2.3 PS与PL交互接口设计

PS与PL端的数据交互通过片内的AXI总线实现,它共有AXI4、AXI4-Lite和AXI4-Stream三种形式:AXI4主要面向高性能地址映射通信的需求;AXI4-Lite为轻量级的地址映射单次传输接口;AXI4_Stream面向高速数据流传输,允许无限制的数据突发传输。PL部分各模块封装成的IP Core都严格按照AXI总线协议挂载在AXI总线上,由于基带数据流吞吐量较大,实时性要求较高,所以采用AXI4-Stream总线形式,物理接口采用AXI_HP。模块中的参数配置数据量小,无实时性要求,所以采用AXI4-Lite总线形式,接口采用AXI_GP接口来实现。

3 系统测试

为了验证本平台的通信可靠性,采用调频(Frequency Modulation,FM)波形和正交相移键控(Quadrature Phase Shift Keying,QPSK)波形对其进行性能测试。该测试仅针对模数和数模转换器后的射频信号进行测试,不包括射频前端模块。

3.1 灵敏度测试

硬件平台的接收灵敏度检验通过FM波形测试实现。为了测试不同频段的接收灵敏度,采用综合测试仪发出不同频率的射频信号。首先,通过综合测试仪将一固定频率的具有标准FM调制(1 kHz标准音频信号,达到5.6±0.5 kHz频偏)的射频信号加至硬件平台射频输入口;然后,通过调节输入被测设备的射频信号功率,使综合测试仪显示的信纳比不低于12 dB,保证解调后的信号质量不失真;最后,记录信纳比不低于12 dB的最小射频信号发射功率,即为数字部分的灵敏度。

图4展示了通过射频直接采样技术实现的低频段信号接收灵敏度的测试结果,图4(a)为60 MHz射频信号的接收灵敏度测试界面,图4(b)展示1~70 MHz低频段射频信号的灵敏度变化曲线。从图4(b)可以看出,对于频率在9 MHz以上的射频信号,其接收灵敏度稳定在-79 dBm左右;当频率低于9 MHz时,灵敏度开始急剧下降,3 MHz射频信号的接收灵敏度为-68 dBm,1 MHz射频信号的接收灵敏度为-57 dBm。实验表明,该平台对9~70 MHz射频信号有很强的接收能力;通过对信道模块增益的设计,也可较好接收2~9 MHz的信号。灵敏度测试验证了射频直接采样技术实现低频段信号接收的可靠性。

(a)60 MHz FM波形接收灵敏度测试界面

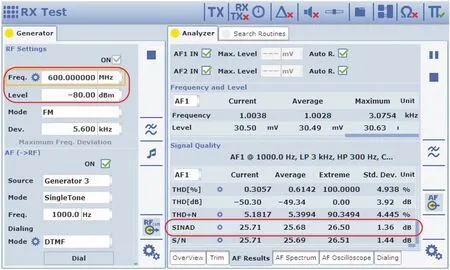

图5为基于AD9361的零中频采样技术实现的中高频段信号接收灵敏度的测试界面。由于AD9361芯片自身可以设置0~76 dB的增益,因此中高频段信号的接收灵敏度都非常好,在此只提取了600 MHz的测试结果举例说明。从图5可以看出,当工作频率为600 MHz,射频信号功率调为-80 dBm,AD9361给定增益为16 dB时,综合测试仪测得的信纳比为25.71 dB,说明在此增益下的接收灵敏度要高于-80 dBm;通过调节AD9361的增益还可进一步提高灵敏度。因此,基于AD9361的零中频采样技术对中高频段信号的接收性能优异。

图5 600 MHz FM波形接收灵敏度

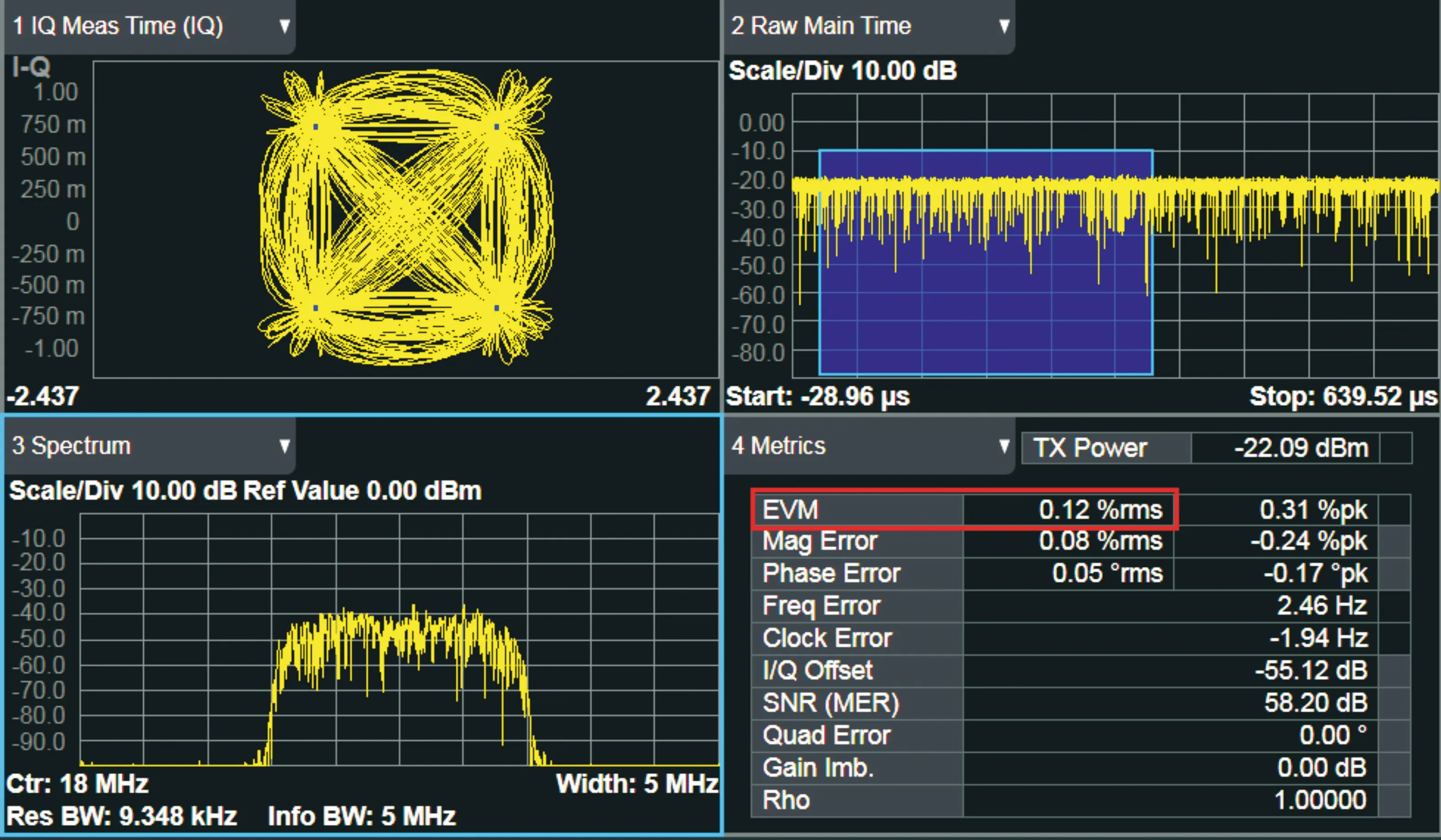

3.2 误差向量幅度测试

硬件平台对不同频率信号的发射质量通过误差向量幅度(Error Vector Magnitude,EVM)来衡量。EVM能全面衡量调制信号的幅度误差和相位误差,以百分比的形式表示,EVM越小,星座图中的点越集中,表示星座图上实际接收信号点与参考信号点的偏离程度越小,信号质量越好。EVM的值通过QPSK波形测试获取:首先将平台发射的信号通过射频线缆接入矢量信号分析仪(Vector Signal Analyzer,VSA),然后对VSA中信号的带宽、频率、符号速率等相关参数进行设置,VSA便可以测量并计算出不同带宽下不同频率信号的EVM值。

图6(a)~(c)为18 MHz中心频率下带宽分别为2 MHz、4 MHz和10 MHz的QPSK波形测试的频谱和星座图,可以看出,18 MHz中心频率下2 MHz、4MHz和10 MHz带宽的星座图中的点都很集中,EVM值分别为0.12%、0.28%和1.81%,具有优越的通信性能。图7进一步展示了系统不同带宽下系统各频点的EVM值。由于本平台的目标应用对象要求通信频段为30 MHz~2.5 GHz,系统的数模转换芯片匹配电路以及射频开关等模拟部分均按该频段的要求进行设计,故本实验中QPSK波形测试仅对2.5 GHz以下的频段进行。从图7可以看出,2 MHz带宽下,12 MHz以上频段信号EVM值都小于2%;4 MHz带宽下,14 MHz以上频段信号EVM值都小于2%;10 MHz带宽下,18 MHz以上频段信号EVM值都小于2.5%。本平台在18 MHz~2.5 GHz频段内对10 MHz带宽以下的信号具有优异的发射性能。

(a)18 MHz中心频率、2 MHz带宽的QPSK波形测试结果

图7 不同频率不同带宽的EVM曲线

4 结 论

本平台在采用基于零中频采样技术的AD9361实现70 MHz~6 GHz频段信号收发的基础上,进一步通过射频直接采样技术实现70 MHz以下频段信号的收发,在不增加射频前端部分设计复杂度的基础上扩展了传统平台的通信频段。通过将较高采样率的模数/数模转换芯片和高集成度的片上系统器件集成在一块印制板上,大大减小了该平台的体积。通过采用FM波形和QPSK波形对不同频段的性能进行测试,验证了本平台在整个宽频段都具有优异的通信性能。采用该平台的通信设备在兼容低频段的通信设备时,射频模拟电路中无需采用模拟混频电路,降低了射频模拟电路的设计复杂度和调试难度,同时十分契合当下小型化、低功耗、高度集成化的软件无线电平台设计目标。