高性能直接式频率合成器的小型化设计

2022-07-22席安安薛子鹏

常 进 席安安 薛子鹏 王 娜

(西安电子工程研究所 西安 710100)

0 引言

微波频率源是微波电路中的关键部件,尤其在雷达、干扰对抗、微波成像等应用场景下,其性能指标尤为苛刻。宽频带、细步进、捷变频、低相位噪声、低杂散和小型化已经成为频率综合器的发展趋势。

目前直接式频率合成器主要应用基于DDS技术作为中频频标,并采用开关倍频组件混频实现射频频率,其中频率源中大量使用LC、腔体滤波器、隔离器等大体积器件。虽实现高杂散及低相噪指标,但具有较大体积,在该方案基础上不易进行小型化设计。另一种方案是采用PLL技术,实现微波频标信号,再通过开关、分、倍频技术实现宽带信号源。由于采用PLL技术,因此信号跳频时间长,难以应用在高速扫频雷达中。

另外,考虑到一些特殊应用场景,需要频率合成器具有小型化、轻量化的特点,这就需要我们进行一些特殊的设计。在国外,美国NI公司研制的PXle-5654系列模拟信号源,工作频率覆盖250kHz~20GHz,采用3U模块架构,体积61mm×130 mm×214mm。以色列通用微波公司研制的MFS0218频综模块,工作频率覆盖2~18GHz,体积152.4mm×152.4mm×27.9mm。在国内,成都菲斯洛克公司研制的DSY201820捷变频频率源,工作频率覆盖250kHz~20GHz,体积是200mm×150mm×30mm。以上这些成果在小型化和超宽带上已经具备了一定的优势,但是在某些指标如相位噪声、杂散、跳频时间各有不足。

基于以上应用需求,本文提出一种基于级联混频的频率合成方法,在现有器件水平下,经过合适选型,结合MCM工艺进行直接式频综的小型化设计。该频率合成器具有宽带、细步进、捷变频、低相位噪声、低杂散和小型化的特点。文章第一部分给出了设计方法,第二部分给出了详细指标分析,第三部分给出了主要指标测试结果。

1 设计原理

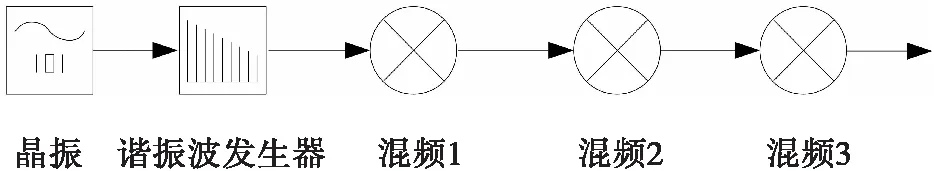

本设计中采用的直接式频率合成技术,除传统开关滤波之外,额外引入了级联混频的方法,用于拓宽频率范围。所谓级联混频就是采用多级混频,来进行带宽搬移,以此来实现倍于基础频带的带宽。本文将结合设计实例来进行详细说明,工作原理如图1所示。

图1 频率综合器设计原理图

本系统中,晶振频率为100MHz,相位噪声-155dBc/Hz@1kHz。通过谐波发生器产生高次谐波。这里谐波发生器采用阶跃恢复二极管,具有频谱效率高的特点。谐波发生器产生丰富的高次谐波,利用多工网络对谐波进行功分和滤波等,提取所需要的频率。其中包含DDS的参考时钟、大步进的频标信号和用于级联混频的中频频标。

DDS采用GM4912,参考时钟是3200MHz,产生300~400MHz的任意步进的中频信号。大步进的频标信号采用开关滤波网络进行滤波。这里摒弃传统的LC或腔体滤波器,采用新型FBAR滤波器(薄膜体声波滤波器),一般需要至少2级。得到高纯频谱的频标信号3200MHz~3600MHz。通过将DDS频率和频标信号进行混频,可以得到3500~4000MHz的基础频率,带宽500MHz。

然后再将该信号与500MHz频标信号进行混频,取混频的和频和差频可以将基础频率向上、向下分别拓宽500MHz。再将该信号与500MHz进行一次混频就可以进一步将频率向上、向下拓宽500MHz。最后通过开关将三路信号进行合并输出,就可以实现总带宽2.5GHz,频率覆盖2.5~5GHz的输出频率了。

本文应用梳谱频率产生、多工频率分选技术,提高频率利用率,应用FBAR滤波器技术实现高集成度开关滤波组件,进而实现大步进微波频标提取。采用DDS实现Hz级频率步进,结合百兆赫兹级的固定步进微波频标信号,使得输出频率具有细步进连续可调特性,从而让产品具有软件可重构功能,实现产品通用化。采用级联混频方案,通过级联混频扩展带宽,在倍频程带宽内不需对DDS产生频率进行倍频,有效改善了输出信号杂散。

2 指标分析

2.1 相位噪声

信号相噪恶化路径如图2所示。

图2 相位噪声恶化

谐波发生器输出信号的相位噪声可由式(1)表示为

()=()+20log+

(1)

()是100MHz恒温晶振相位噪声,可以达到-155dBc/Hz@1kHz,通过谐波发生器之后最大输出频率为3600MHz,相噪恶化20log(),取36。表示混频附加相位噪声恶化值。谐波发生器输出信号与DDS信号进行混频,该DDS信号为GM4912输出信号,300~400MHz,相噪实测约-130dBc/Hz@1kHz,远优于频标信号,因此混频后的相噪主要考虑频标信号,工程损耗小于1dB。后面与500MHz进行的2次混频也是同理。每次混频工程损耗小于1dB。利用式(1)计算最终输出信号相位噪声值为:()≈120dBc/Hz@1kHz。

2.2 杂散抑制

杂散主要来源分别是梳状谱发生器输出信号、混频、倍频谐波分量和本振泄露、开关和功分器信号串扰、电源与射频信号串扰、多层板信号空间及板内串扰。其次来源于DDS中频信号输出杂散。

梳状谱发生器输出信号频谱成分丰富,首先通过低通滤波网络和功分多工网络对有用信号进行分别提取,主要包含0.5GHz,3.2~3.6GHz点频信号。再通过声表波滤波器、FBAR滤波器多级(3级)级联进行点频信号滤波,以确保杂散在-70dBc以下。

采用开关滤波级联(2级)网络对混频和倍频信号进行分段滤波,以确保混频谐波分量和泄露杂散被抑制到-70dBc以下。

DDS输出信号300~400MHz经过开发评估板实测近端杂散优于-75dBc,通过LC或LTCC滤波器实现滤波,将可用信号外杂散和谐波进行滤除,杂散可降低至-70dBc。

开关和功分器信号串扰需考虑开关和功分器信号隔离度,利用衰减器、滤波器、放大器的反向隔离等措施降低开关和功分器通道间的杂散。综上所述,通过以上措施可以将杂散控制在-70dBc以下。

2.3 跳频间隔、跳频时间

跳频时间主要由小步进DDS频率切换时间、大步进开关滤波切换时间和控制信号写入和传输延时构成。DDS频率建立时间在ns级,同时开关切换时间是几十ns,数字信号控制写入和传输时间约几百ns,因此跳频时间可控制到1μs以内。

3 硬件实现与指标测试

模块采用矩形连接器进行电源和控制信号的传输,对外射频接口采用SMA连接器。最终完成模块如图3所示。

图3 频率合成器电路结构

内部集成晶振、时钟分配、通讯、控制、DDS、梳状谱发生器、多工网络,各级开关滤波、合路滤波等电路。将这些功能电路集成设计、同时考虑电磁兼容,极具挑战。本项目采用多层板和MCM实现集成化设计,合理划分功能区,数字电路和模拟射频电路集成到一块多层印制板上,最大化利用空间,并兼顾电磁兼容和导热等设计。

为了提高信号之间的隔离度,减小串扰,提高杂散,需要对电源、结构等采取一定的措施。例如,电源与控制信号的隔离,通过磁珠、高阻线和高频旁路电容进行抑制,防止不同通道之间信号的串扰。采用足够多的分腔、屏蔽胶条等尽可能阻断空间信号串扰,板内也采用地孔、铺地等方式减小信号串扰,并通过内层带状线减小表面波串扰。除通过以上措施外,在设计时也要尽可能考虑细节,以减小信号串扰和杂散的产生,如在分段滤波时,将相邻频带信号顺序打乱隔离,以提高滤波器抑制效率等。

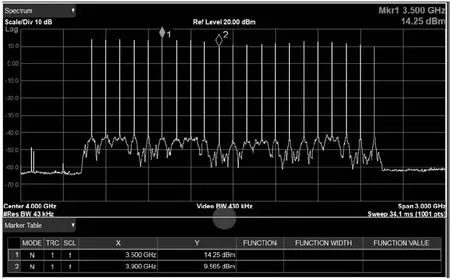

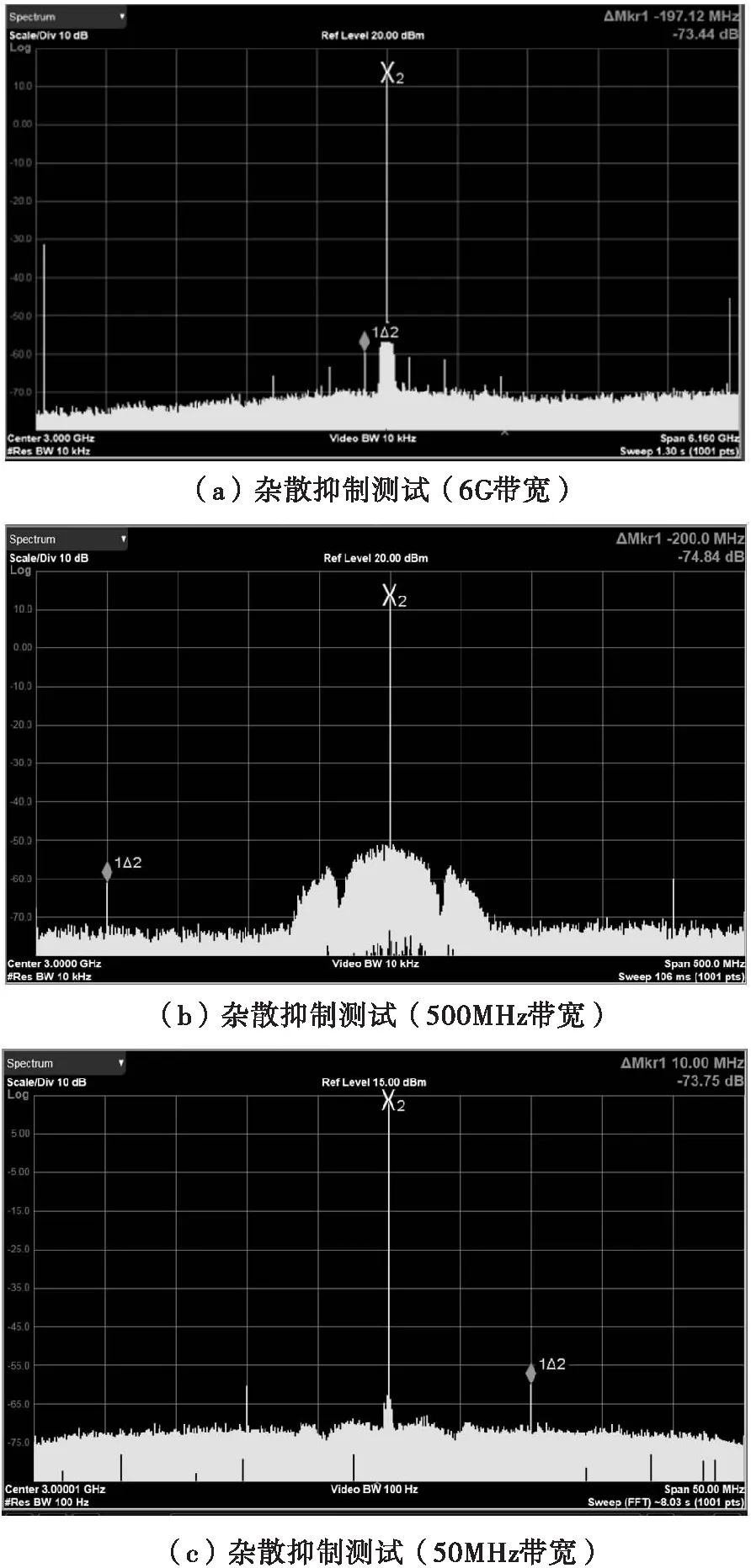

功率和杂散抑制采用是德科技的N9040B频谱分析仪进行测试,相位噪声采用安捷伦的E5052B信号分析仪,测试结果如图4至图6所示。可以看到在带宽输出内,输出功率约12dBm,功率起伏在4dB内。当输出频率为3GHz,杂散在近端、远端均优于-73dBc。当测试频率为4.327GHz时,典型相位噪声为-123 dBc/Hz@1kHz。

图4 功率幅度测试

图5 杂散抑制测试图

图6 相位噪声测试

4 结束语

本设计中频率综合器采用级联混频技术,并实现了小型化的样机。该频率综合器具有宽频带、细步进、低相噪、小型化、捷变频等特点。同时本文所提到的设计方案,可以拓展到其他频段,实现更宽的应用范围。本文给直接式频率合成技术提供了小型化的设计方向,这使得传统的直接式频率合成器可以应用于更广泛的平台上。