一种低杂散低相噪频率源的设计与实现

2022-07-21程建斌钟耀霞

程建斌 ,钟耀霞

(1.中科芯集成电路有限公司,江苏 无锡 214072;2.电子科技大学成都学院,四川 成都 611731)

0 引言

随着微波通信技术的快速发展,对接收机的灵敏度要求越来越高,作为各类接收机的心脏,频率源需要为其提供高性能的本振信号,它的相位噪声指标成为制约接收机性能的关键因素之一。为了改善频率源的相噪,国内外很多公司和科研机构开展了很多这方面的研究,也提出了各种有效的方法。这些方法有的从构成锁相环的相位噪声来源直接分析[1-2],更多的从实现方式来分析,包括新型直接合成[3]、DDS 和锁相环芯片混合技术[4]、自偏置[5]、谐波混频[6]、新型多级自谐波混频[7]和级联式偏置[8]、混频环[9]等。这些方法要么采用直接合成,方案复杂且体积大;要么是针对宽带低相噪系统的,方案实现起来比较复杂,而且价格高,面对一些特殊的应用会造成系统的复杂度提高。基于某些特定应用环境,本文设计了一种可用于频率间隔固定的低相噪频率源,利用最新的低相噪合成器芯片,同时采用谐波发生器产生低相噪的固定射频信号来参与混频,最终降低频率源的反馈分频比的方法来改善相噪。对采用该方法设计的频率源的相噪指标进行了测试,经过对比测试指标和理论指标,证明该设计方法符合要求,可以在满足特定要求的场合使用。

1 工作原理

低相噪频率源的设计指标为:工作频率13.75 GHz~16.25 GHz(不包含15 GHz),步进250 MHz,相噪优于-102 dBc/Hz@1kHz,杂散优于65 dB。

该频率源的特点在于相噪指标比较高同时要求成本不能高,输出频点不多且步进大。结合前面各种优化相噪的技术和新的元器件性能,本文提出了如图1 所示的实现方案。

图1 低相噪本振的原理框图

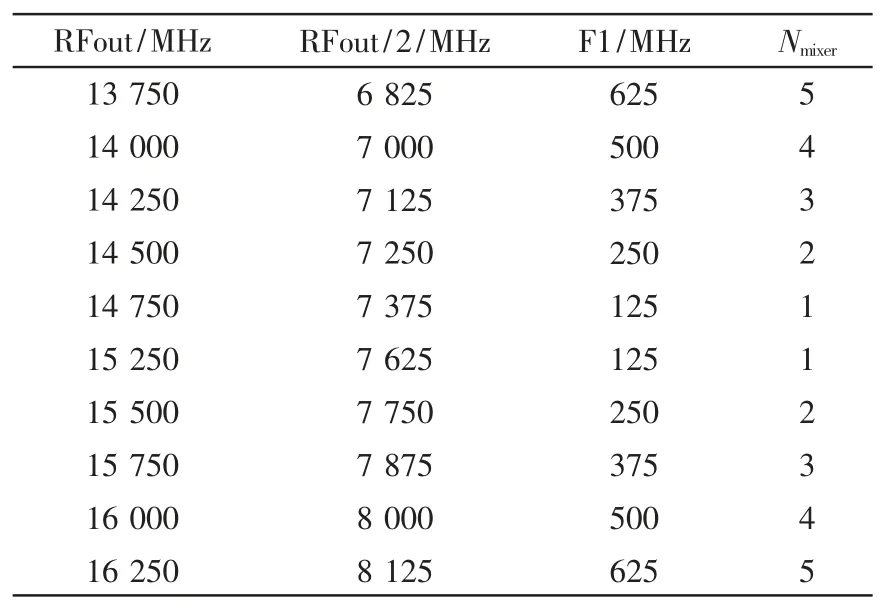

在图1 中,内部100 MHz 经过谐波发生器1 倍频后产生500 MHz 的信号,该信号经过功分器后产生两路信号,其中一路作为鉴相器(PFD)的参考信号,送到PFD 的OSCIN 引脚;第二路信号经过谐波发生器2 倍频后产生7.5 GHz 低相噪信号,该信号和RFout/2 信号经过混频后产生频率为F1 的信号再送入鉴相器的PFDin 引脚。该方案中低相噪的实现主要取决于7.5 GHz 的相噪,因为混频后输出频率不高。从表1 可以看出,最大的分频值是5,相噪会恶化14 dB。由于频率合成器的步进是250 MHz,采用125 MHz 作为鉴相频率,经过混频后的频率都是125 MHz 的整数倍,可以采用整数鉴相,且鉴相杂散远远在环路带宽外,可以得到充分抑制。在这个设计中,采用整数鉴相,鉴相频率为125 MHz,具体的频率规划见表1。

表1 输出频率规划表

表1 中RFout 为输出频率,RFout/2 为频率综合器芯片反馈输出的频率;F1 为混频后的输出频率,为7 500 MHz和RFout/2 的混频下边带值;Nmixer值为分频值,等于F1 除以125。对于15 GHz 这个点,因为混频后F1 的频率为0,故该点不适合。

从表1 可以看出,输出频率规划满足需求。

1.1 关键器件分析

为了实现低成本和降低模块体积,需要选择合适的鉴相器芯片。作为实现内置混频方案的鉴相器,需要具备以下3 个特性:首先,芯片内部需要集成VCO,且输出频率范围能够覆盖需要的频率范围,这样就不需要外部VCO;其次,能够同时输出多通道,这样可以一路作为输出,另外一路作为反馈,这样可以减少外部的功分器;最后,芯片需要有外部鉴相输入功能,可以支持外部混频信号输入,否则反馈信号在锁相环芯片内部就直接反馈输入到鉴相器了,无法进行混频来降低反馈频率。

目前性能指标最高的几款鉴相器的特性对比见表2。从表2 可以看出,在目前可以使用的器件中,只有LMX-2820 才能满足这个要求。图2 为LMX2820 内部的原理框图。

图2 LMX2820 功能框图

表2 鉴相器性能对比表

1.2 关键技术分析

为了实现需要的低相噪的指标要求,采用了谐波发生器来产生低相噪的内置混频本振信号,同时利用内置混频技术来降低反馈分频值。

1.2.1 谐波发生器技术

低相噪频率源中采用了两次谐波倍频技术,第一次是将100 MHz 的参考信号倍频到500 MHz,用来作为鉴相器的参考和第二次倍频的输入;第二次是将500 MHz的输入信号倍频到7.5 GHz 信号。进行谐波发生器设计时,主要需要考虑的问题为倍频的附加相噪和输出信号对不需要谐波的滤波效果。倍频器对相噪的恶化为20lgN,其中N 为倍频次数。

参考源采用的是高性能的100 MHz 恒温晶振,相噪优于-160 dBc/Hz@1kHz,经过75 倍频后相噪恶化38 dB,7.5 GHz 的相噪为-122 dBc/Hz@1kHz,考虑到实际的附加相噪贡献,7.5 GHz 信号的相噪为-120 dBc/Hz@1kHz。

在进行谐波发生器设计时,需要将输入功率放大到满足阶跃二级管的输入功率要求,同时要求该放大器的相噪指标低[10]。

1.2.2 内置混频技术

为了降低这个锁相环反馈分频值N,采用了混频的方式。从图1 可以看出,F1=|RFout/2-7 500|MHz,鉴相频率为125 MHz,混频后的N 值见表1。从表1 可以看出,混频后的最大N 值为5。如果不采用混频技术,输出频率比较高,采用目前最高端的器件,采用单环方案来产生16 250 MHz 的信号,输出的相噪指标能理论最高能达到-98 dBc/Hz@1kHz,不能满足实际需求。本设计的混频配置方式见图3,以最高输出频率16 250 MHz 来说明混频技术的实现。从图2 可以看出,LMX2820 内部的鉴相器部分支持两种外部输入,分别为RFin 和PFDin,这两种外部输入就是混频后的信号输入端口。对于LMX2820,使用混频方式来改善相噪的配置关键,它有两种模式,当混频后分频次数小于12 时,需要采用PFD引脚的混频;如果混频后分频次数大于12,需要采用RFIN 引脚的混频方式。在图3 中,因为LMX2820 的基频信号频率范围为5.65 GHz~11.3 GHz,输出信号都是内部振荡器二倍频(RFout)后输出,另一支路是基频信号(RFout/2)输出后和7.5 GHz 低相噪信号进行混频,混频后的信号经过低通滤波器后送入LXM2820 的PFDin 引脚,内部经过N 分频器后进入鉴相器(PFD)作为鉴相频率信号,和OSCin 引脚送入的信号经过R 分频器(R Divider)后的信号进行比较,输出的信号和外部环路滤波器相连,产生调谐电压送内部的压控振荡器。

图3 内置混频技术原理框图

2 主要指标分析

2.1 相噪指标分析

对于使用合成器芯片来实现的频率源,相噪按照式(1)~式(3)来综合评估。

其中,PNPLL_Flat为鉴相器的归一化相噪,值为-236 dBc/Hz;PNPLL_1/f为鉴相器的闪烁噪声归一化噪底,值为-134 dBc/Hz;FPD是鉴相频率,为125 MHz;FVCO为输出频率,在这里指混频后的反馈频率;PLLFlat为鉴相器自身对频率源的相噪贡献;PLLflicker(offset)为鉴相器闪烁噪声对频率源的相噪贡献,这里offset 值为1 kHz。在这里按最高输出频率16.25 GHz 进行评估,如果不采用混频技术,FVCO为16.25 GHz;采用混频技术后,FVCO为625 MHz,但此时的625 MHz 的相噪是由混频采用的7.5 GHz 信号决定的。各个部分的相噪贡献见表3。

表3 信号相噪分布表

2.2 杂散指标分析

频率源的主要杂散有鉴相杂散、7.5 GHz 的泄露杂散和输出信号的亚谐波杂散。频率源采用整数鉴相,鉴相频率125 MHz 偏离环路带宽很远,通过环路滤波器很容易将其移至到75 dBc 以上,7.5 GHz 杂散和亚谐波杂散离输出频率较远,主要通过输出端的定制带通滤波器来保证。

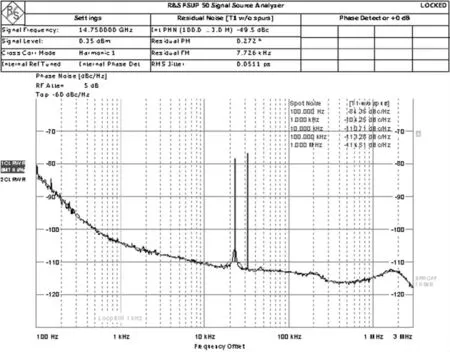

3 测试验证

根据上述原理,研制了该低相噪本振源。在内部100 MHz 恒温晶振相噪指标为-160 dBc/Hz@1kHz 的条件下测试最低频率13.75 GHz、中间频率14.75 GHz 和最高输出频率16.25 GHz 的信号,其频谱图和相噪图分别如图4~图9 所示。从图可以看出,在整个输出频率范围上,最高相噪为-104.21 dBc/Hz,杂散优于-70 dBc。

图4 13.75 GHz 信号频谱图

4 结论

图5 14.75 GHz 信号频谱图

图6 16.25 GHz 信号频谱图

本文采用的混频式频率源实现的步进为250 MHz的低相噪频率合成器,利用了谐波发生器和最新的鉴相器芯片来实现指标的同时降低复杂度,在体积和成本方面优势显著,但它对使用条件有限制,在满足条件的情况下使用非常具有性价比。同时,随着工艺的发展,可以采用MCM 技术将该频率源进行小型化设计[11],满足更多场景的需求。

图7 13.75 GHz 信号相噪图

图8 14.75 GHz 信号相噪图