FinFET工艺器件总剂量和单粒子效应研究进展

2022-07-13魏轶聃刘国柱魏敬和

陶 伟, 魏轶聃, 刘国柱, 魏敬和

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

0 引 言

自从1960年金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)发明以来,超大规模集成电路的特征尺寸越来越小,体硅MOS器件随之出现了一系列问题,尤其在有效栅长低于22 nm时,由于栅极对电子的控制减弱,传统平面型MOSFET器件表现出明显的短沟道效应,导致晶体管器件性能降低和功耗增大,愈发难以满足高集成和低成本的需求[1-2]。针对电路控制、电流泄漏和功耗提升等多方面问题,胡正明教授等人分别设计了体硅FinFET器件(Fin Field-Effect Transistor,FinFET)和SOI FinFET器件,它们的沟道区域被栅极包裹呈鳍状,使栅极对沟道中电子控制增强,从而降低了泄漏电流,抑制短沟道效应[3-4]。2011年Intel公司推出了商业化、闸门呈鱼鳍状的22 nm FinFET器件。近年来,工艺节点也随工艺技术提升逐渐减小到2019年的10 nm,同时在体硅FinFET器件和SOI FinFET器件的基础上衍生出了多种性能更高、功耗更低的结构,如环型栅FinFET器件、π型栅FinFET器件和Ω型栅FinFET器件等[5-7]。

随着空间探索范围增大和人类空间活动增多,工作于空间环境中的半导体器件,其工作状态、可靠性和寿命会受到多种宇宙射线及粒子辐射的影响,严重时甚至会导致航天器失效和损毁[8-10]。根据离子对半导体器件造成的损伤类型划分,半导体器件的损伤效应主要有两种:总电离剂量效应与位移损伤效应。其中,总电离剂量效应主要来自于高能光子、质子、重离子和电子;位移损伤效应主要来自于高能质子、中子和重离子。

对于MOSFET,尤其是作为高集成、低功耗、小尺寸航空应用的FinFET器件,当带电粒子、γ射线和X射线进入FinFET器件鳍部氧化物内部,会与其原子核外电子发生作用,产生电子-空穴对。在电场作用下,未复合电子通过正电极逃离氧化层;未复合空穴则被氧化物中缺陷捕获,形成带正电的氧化物陷阱电荷,或在界面处形成界面态[11]。相比于平面型MOSFET,由于栅结构的改变,纳米量级FinFET器件的辐射损伤机理会发生显著变化,因此一直是学术界和工业界重点关注的热点问题[12-13]。

综上所述,揭示FinFET器件辐射损伤机理,提出合理抗辐射加固方案,不仅有利于为新一代半导体器件的抗辐射加固奠定理论和技术基础,还有助于推进先进工艺在空间中应用。本文简要综述了FinFET器件工艺技术,重点介绍了总剂量效应和单粒子效应对FinFET器件的影响。

1 FinFET工艺简介

辐射所致的电子-空穴对迁移、电荷俘获和界面态形成均与半导体材料和界面缺陷紧密相关,而材料及界面的缺陷形成过程与FinFET工艺相关联,所以FinFET工艺能够极大地影响FinFET器件抗辐射性能,下面对FinFET器件工作原理和工艺技术进行简要介绍。

1.1 FinFET器件工作原理

随着器件栅极尺寸不断缩小,其与电子通道间接触面积也逐渐减小,导致栅极对沟道中电子的控制减弱,短沟道效应显著增加,因此平面型场效应晶体管在22 nm以下工艺节点的截止电流急剧增大。FinFET器件通过在绝缘衬底上构造高而薄的鳍结构,增大栅极围绕沟道面积,加强栅极对沟道中电子控制,可克服平面型器件的短沟道效应,减少泄漏电流,其工作原理如图1所示。

图1 工作原理图

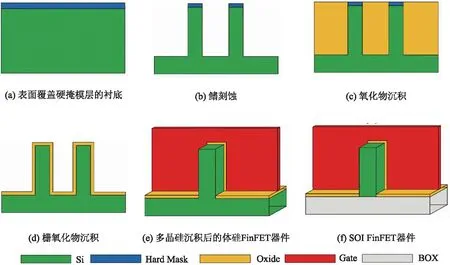

1.2 FinFET工艺

空间辐射过程会在半导体材料及界面造成电离和位移损伤,通过改进工艺参数或改变器件结构能够有效降低器件的敏感性,实现半导体器件的抗辐射加固,因此,本部分先对FinFET工艺进行简要介绍。FinFET工艺主要流程包括鳍刻蚀、氧化物沉积、氧化物化学机械抛光、氧化物刻蚀、栅氧化层沉积、多晶硅沉积等步骤,如图2所示。一方面,通过鳍刻蚀能够有效调节鳍宽、鳍长和鳍间距,实现总电离剂量抗辐射加固;另一方面,在FinFET工艺过程中通过离子注入增大沟道中掺杂浓度,抑制反型层形成,减小总剂量效应导致的泄漏电流。目前,FinFET工艺器件节点已经缩小到5 nm,并向3 nm发展,通过工艺改进在提升器件性能的同时,增强器件的抗辐射性能是FinFET器件研究的重点。

图2 FinFET工艺加工流程

2 FinFET器件的总电离剂量效应

从FinFET器件工作原理可以看出,与平面型场效应晶体管相似,FinFET器件的开关状态是通过氧化物进行控制,且FinFET器件栅极三面均由氧化物构成,所以总电离剂量辐射过程产生的氧化物电荷会对FinFET器件性能产生显著影响,本部分从工艺参数和材料对FinFET器件的抗辐射性能进行了详细分析。

2.1 工艺参数对FinFET器件总剂量效应影响

工艺参数会直接影响FinFET器件的性能及抗辐射性能,所以本部分从工艺参数中的沟道掺杂浓度、基体掺杂浓度和鳍尺寸对FinFET器件总电离剂量效应进行分析。

(1)掺杂浓度对FinFET器件总剂量效应影响

总电离剂量辐射效应会使沟道中形成反型,其反型难易程度与沟道中元素掺杂浓度紧密相关,所以通过改变沟道掺杂浓度的方式有望改善FinFET器件的抗辐射性能。文献[14]通过Co60辐照实验研究发现,因为辐照导致氧化物中俘获电荷数量逐渐增多,所以器件阈值电压漂移量随辐照剂量增大而增大,而且受到器件偏压和沟道中掺杂元素浓度的影响,在10 M(rad)辐照剂量下,不同器件偏压下的阈值电压漂移量基本相同。虽然不同掺杂浓度下的阈值电压差异明显,但这是由于掺杂浓度增大改变了初始阈值电压,所以通过比较辐照前后阈值电压变化量的百分比,发现不同沟道掺杂浓度下的百分比变化量基本相同,如图3所示。

图3 不同沟道掺杂浓度下,辐照前后FinFET器件电性能变化[14]

总电离剂量效应会使沟道阻止区域中的寄生晶体管开启,而且寄生晶体管的开启与沟道阻止区的掺杂浓度紧密相关,所以沟道阻止区掺杂浓度对FinFET器件总电离剂量效应有着显著影响。对于体硅FinFET器件,当其栅氧化层厚度很小时,空穴能够从氧化物中快速脱离,所以此时的总电离剂量效应主要由浅沟槽隔离(Shallow-trench Isolation,STI)中的氧化物导致。文献[15]通过Sprocess仿真研究,发现STI区域俘获的空穴在开态下主要分布在STI区域顶部,通过增大沟道阻止区的掺杂浓度,使寄生晶体管反型层难以形成,进而降低FinFET器件电离总剂量效应,如图4所示。

图4 沟道阻止区掺杂浓度对关态泄漏电流的影响[15]

对于SOI FinFET器件,其受电离辐照引起的俘获电荷可位于硅和二氧化硅界面、STI侧壁和埋氧层界面。文献[16]通过提高基体掺杂浓度,有效阻止了漏电通道形成,所以当辐照感生电荷密度为1012cm-2时,其总电离剂量效应仍不明显。随着辐照剂量进一步增大,氧化物中感生电荷密度逐渐增大,当感生电荷密度增大到1013cm-2时,器件的总电离剂量效应开始显现,如图5所示。

图5 辐照前后漏电流[16]

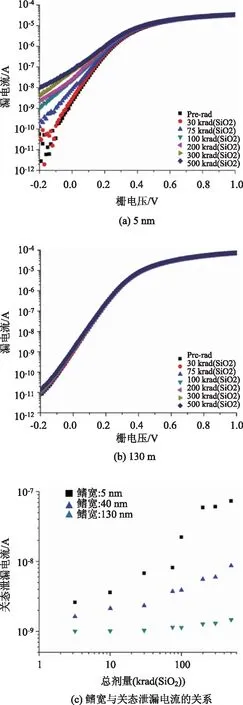

(2)鳍尺寸对总剂量效应影响

三维器件中鳍的各侧面尺寸相近,使器件中电场间存在耦合作用,所以鳍工艺尺寸的变化会对器件性能产生显著影响。文献[17]通过研究体硅FinFET器件在X射线下的行为变化,发现当鳍宽减小时,STI中由辐照引起的电荷更靠近于沟道中部,对势垒高度影响也更显著,因此通过增大鳍片宽度,可有效增强FinFET器件抗总电离剂量效应的能力,如图6所示。针对FinFET器件关态漏电流大的问题,文献[18]设计一种BOI FinFET(Body-On-Insulator FinFET)结构,该结构以FinFET器件结构为基础,然后在栅下方与STI交界处添加一层氧化物。因为沟道下方辐照诱导的泄漏电流被抑制,所以相比于未加固FinFET器件,BOI FinFET器件的关态漏电流随着鳍宽减小未出现显著增大。

对于SOI FinFET器件,文献[19]通过X射线实验研究,发现栅极侧壁会影响鳍和埋氧层间势垒,当鳍宽减小时,栅极侧壁对势垒作用增强,使辐照所致的俘获空穴对器件影响降低;同时,采用将栅极侧壁延伸至埋氧层中的方法,能够有效减少沟道下方的电荷俘获。与文献[19]研究结论相似,文献[20]也发现窄鳍FinFET总电离剂量效应更弱,当鳍宽增大时,由于埋氧层中电荷分布不均匀,所以亚阈值摆幅会发生更明显的退化,使得宽鳍在辐照作用下的开关速率显著降低。同时,文献[21]发现当鳍宽减小时,FinFET器件漏端电流逐渐减小,同时,低频噪声结果显示SOI FinFET器件的氧化物陷阱密度随鳍宽减小而增大,宽鳍中氧化物陷阱多位于硅和二氧化硅界面[15, 21]。

图6 不同鳍宽下辐照前后性能对比[17]

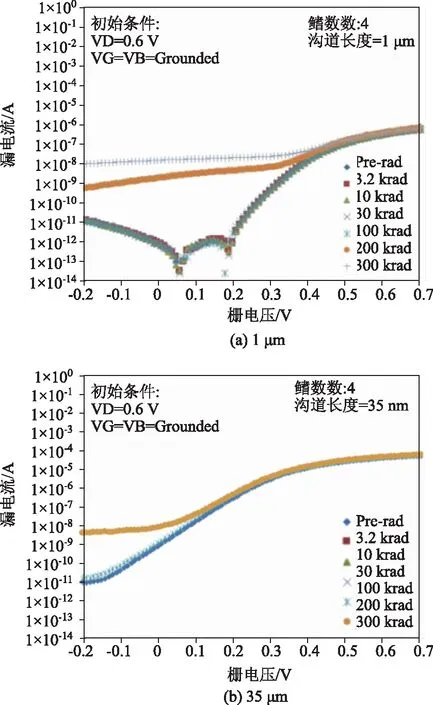

对于体硅FinFET器件,文献[22]发现当辐照剂量达到300 krad(SiO2)时,关态泄漏电流和阈值电压漂移量均随沟道长度的增大而减小,如图7所示[17, 22]。因为与短沟道相比,当俘获电荷浓度相同时,长沟道SOI FinFET器件的寄生晶体管强度较弱,所以背沟道寄生晶体管漏电流随沟道长度增加而减弱[17]。总体上,体硅FinFET器件和SOI FinFET器件的电性能退化均随沟道长度的减小而增强。

图7 相同辐照剂量下,沟道长度对体硅FinFET器件漏电流的影响[22]

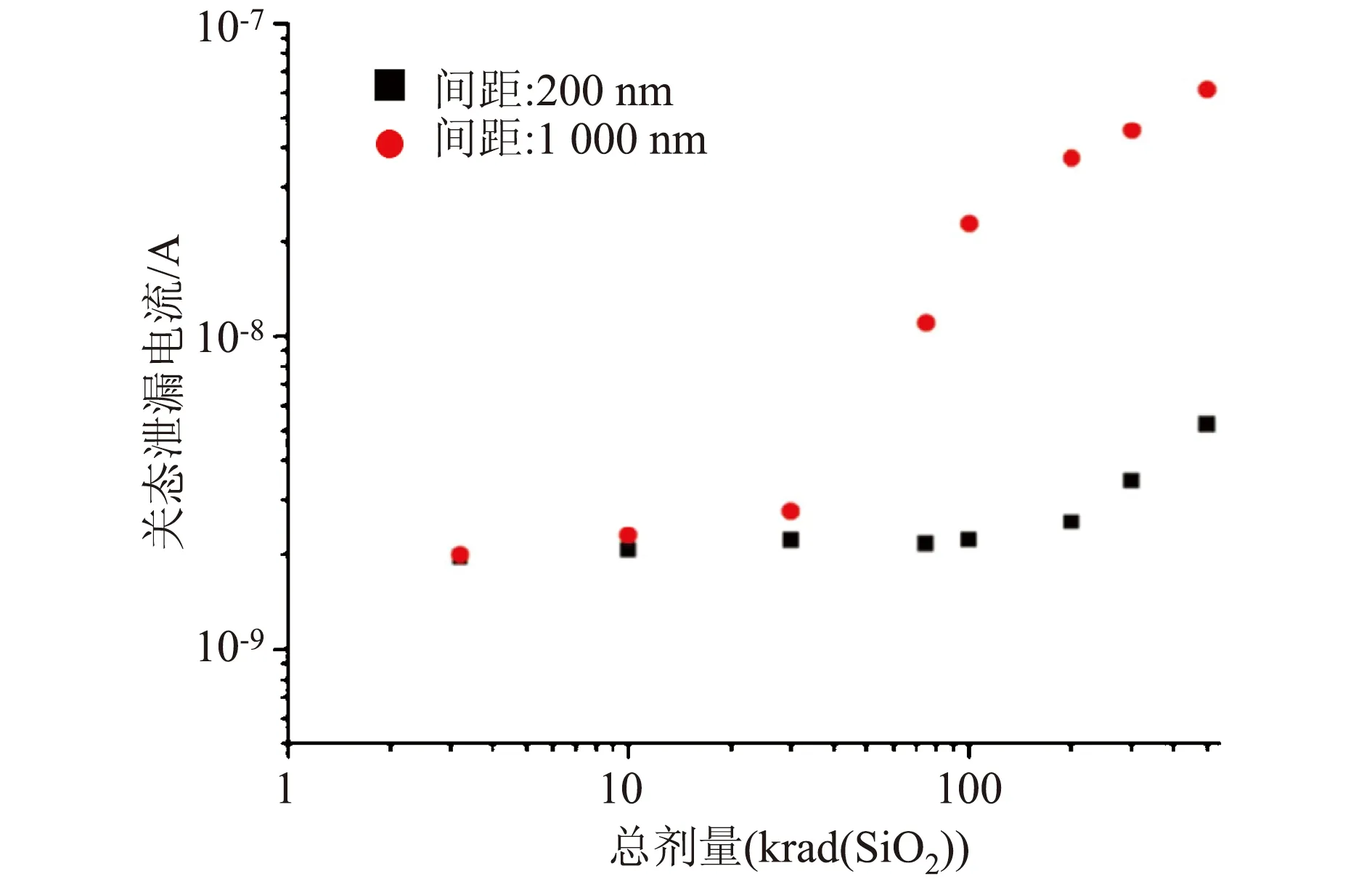

因为FinFET器件尺寸很小,所以不同鳍间距也会对其抗辐照性能产生显著影响。文献[17]研究了不同鳍间距下体硅FinFET器件电性能,发现因为STI中氧化物陷阱电荷数量与STI厚度成比例,鳍间STI中的电场会将电荷扫向寄生通道界面,所以鳍间距增大不仅使得STI中的陷阱电荷增多,还会导致寄生晶体管效应增强,总剂量效应随鳍间距增大而增大,如图8所示。对于SOI FinFET器件,因为埋氧中俘获电荷对器件电性能影响更明显,所以STI中俘获电荷不是性能退化的主要因素。

图8 不同辐照剂量下,鳍间距对体硅FinFET器件泄漏电流的影响[17]

2.2 新型FinFET器件总剂量效应

(1)栅介质对FinFET器件总剂量效应影响

为避免小尺寸器件的栅介质漏电,常采用高k介质材料作为栅避免电子隧穿,达到降低泄漏电流和增强可靠性的目的。文献[23]采用50 kV X射线辐照以HfO2为栅极的体硅FinFET器件,当辐照剂量小于58 krad(SiO2)时,阈值电压漂移量显著增大,而随着辐照剂量进一步增加,阈值电压增长速率变慢,如图9所示。当鳍数目大于2时,FinFET器件阈值电压漂移量随鳍数目变化基本相同,但当鳍数目为2时,其阈值电压漂移量显著增大。

图9 不同材料作为栅的阈值电压漂移量[23-25]

文献[24]构造以SiO2和HfO2为栅的体硅FinFET器件和SOI FinFET器件,随着X射线辐照剂量增大,因为STI中俘获电荷影响,所以体硅FinFET器件的阈值电压向负向移动,如图9所示;SOI FinFET器件因为受埋氧俘获电荷等因素影响,所以当辐照剂量小于500 krad(SiO2),阈值电压也向负向移动,而随剂量进一步增大,栅氧化层/Si和Si/氧化物埋层(BOX)负电性界面态间发生耦合,且SiO2中辐照产生的电子在正偏压下传输到HfO2中,所以Vth正向移动。

文献[25]通过TCAD仿真研究以Al2O3为栅极的SOI FinFET器件,发现当γ源的辐照剂量从100 krad增大到1 Mrad过程中,器件的阈值电压漂移量明显增大,如图9所示。而且与HfO2相比,以Al2O3作为栅极的FinFET器件阈值电压漂移更小。

(2)体材料对FinFET器件总剂量效应影响

除了栅极氧化物外,学者们也对半导体材料进行了广泛探索。文献[26]在Si(100)衬底上制备了Ge FinFET器件,其鳍和沟道分别为Ge和Si0.3Ge0.7,栅极为SiO2和HfO2,如图10所示。辐照前后Ge FinFET器件性能均优于平面型Ge MOS器件,随着X射线辐照剂量增大,器件跨导退化小于5%,阈值电压漂移小于40 mV,如图10(c)所示。与体硅nMOS FinFET器件相比,因为Ge FinFET器件鳍底部拐角处的STI厚度更小、寄生结构影响更低、底部N型掺杂的扩散,所以P型Ge FinFET器件的抗总剂量能力更强。

图10 Ge FinFET器件结构图及阈值电压漂移[26]

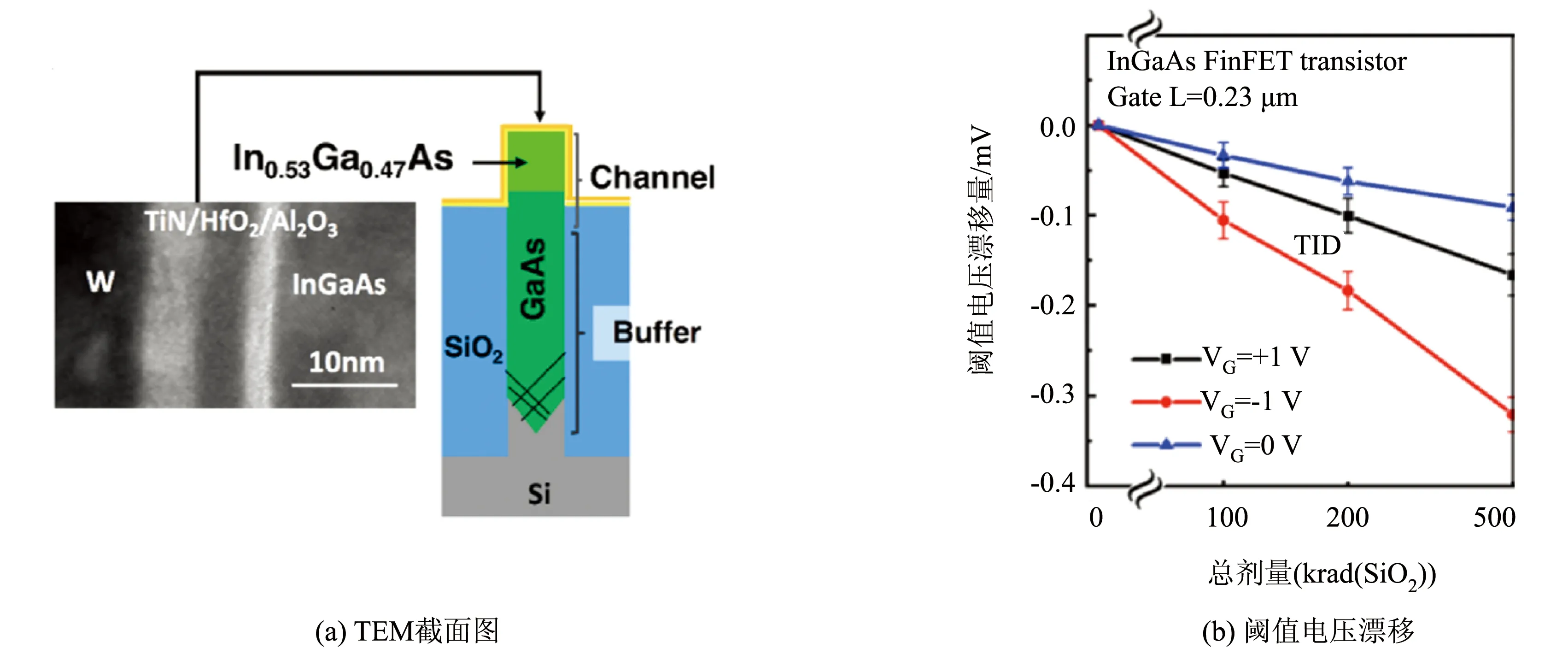

文献[27]通过在Si (100)晶面上生长InGaAs,制备了以HfO2、Al2O3和TiN为栅的InGaAs FinFET器件。X射线入射后的体系中存在大量的电子-空穴对,当它们被界面或氧化物俘获后,会使阈值电压漂移。相比于负偏压下,因为正偏压下HfO2会俘获更多电子,导致正偏压下栅介质中净正电荷更少,所以正偏压下阈值电压漂移量低于负偏压,如图11所示。由于氧化物的静电效应,所以栅极长度短的器件抗辐射性能低于栅极长度长的器件。

图11 InGaAs FinFET器件结构图以及阈值电压漂移[27]

3 FinFET器件的单粒子效应

当高能带电粒子穿过半导体器件时,因其电离作用而在器件内部引入大量的电子-空穴对,当未复合的电子-空穴对被敏感体收集后,会造成非破坏性的软错误或破坏性的硬错误,进而严重影响在轨航天器的稳定性、可靠性和寿命,引发单粒子效应(Single Event Effect,SEE)。核辐射、地球辐射带、银河宇宙线、太阳活动产生的高能带电粒子以及电磁辐射产生的电磁波是单粒子效应的重要成因。单粒子效应主要包括单粒子翻转(Single Event Upset,SEU)、单粒子闩锁(Single Event Latch effects,SEL)、单粒子瞬态(Single Event Transient,SET)、单粒子烧毁(Single Event Burnout,SEB)和单粒子栅穿(Single Event Gate Rupture,SEGR),它们的基本物理机制为电荷收集,主要影响因素包括电荷扩散、漂移和双极放大三种,本部分从LET值和工艺参数对FinFET器件的单粒子效应进行了详细分析。

3.1 不同LET值下FinFET器件的单粒子效应

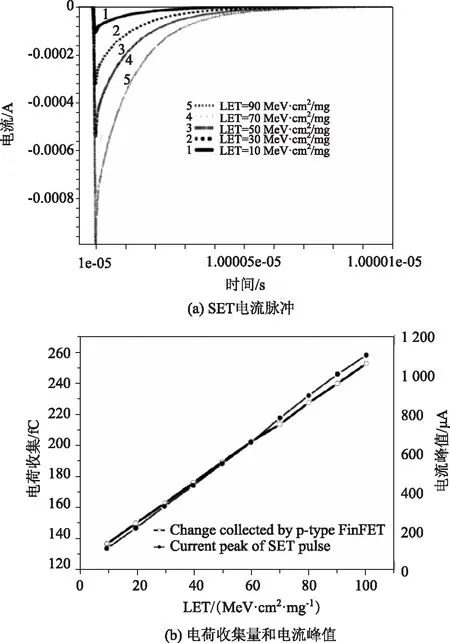

单粒子效应与线性能量传输(Linear Energy Transfer,LET)紧密相关,随着LET值增大,脉冲半峰宽及峰值电流都增大。文献[28]研究发现在LET为90 MeV·cm2/mg时,电荷收集量和电流峰值约是10 MeV·cm2/mg的2倍和10倍,但通过改变工艺参数,如掺杂剂量和掺杂位置等,能够使电荷收集量降低38%,如图12所示。文献[29]通过TCAD模拟研究,发现器件电压与SEU截面相关,当LET值较低时,SEU截面随供给电压减小而显著增大,但是当LET值较高时,SEU截面随供给电压减小而线性增大。

图12 不同LET值下P型FinFET器件的性能变化[28]

除了工艺参数和器件状态,对于P型FinFET器件,文献[30]研究了负偏压温度不稳定性(Negative Bias Temperature Instability, NBTI)与辐射效应间的关系,可见随着时间延长,漏端电流逐渐饱和,随着漏端电荷积累,漏端电流会进一步增大;电路故障时间随入射粒子能量降低而增大,而压降随粒子能量增大而增大,如图13所示。因此,NBTI不仅会增加电路故障时间,导致瞬态错误转化软错误的概率增加,还会降低软错误探测概率。

图13 离子穿过器件后的性能变化[30]

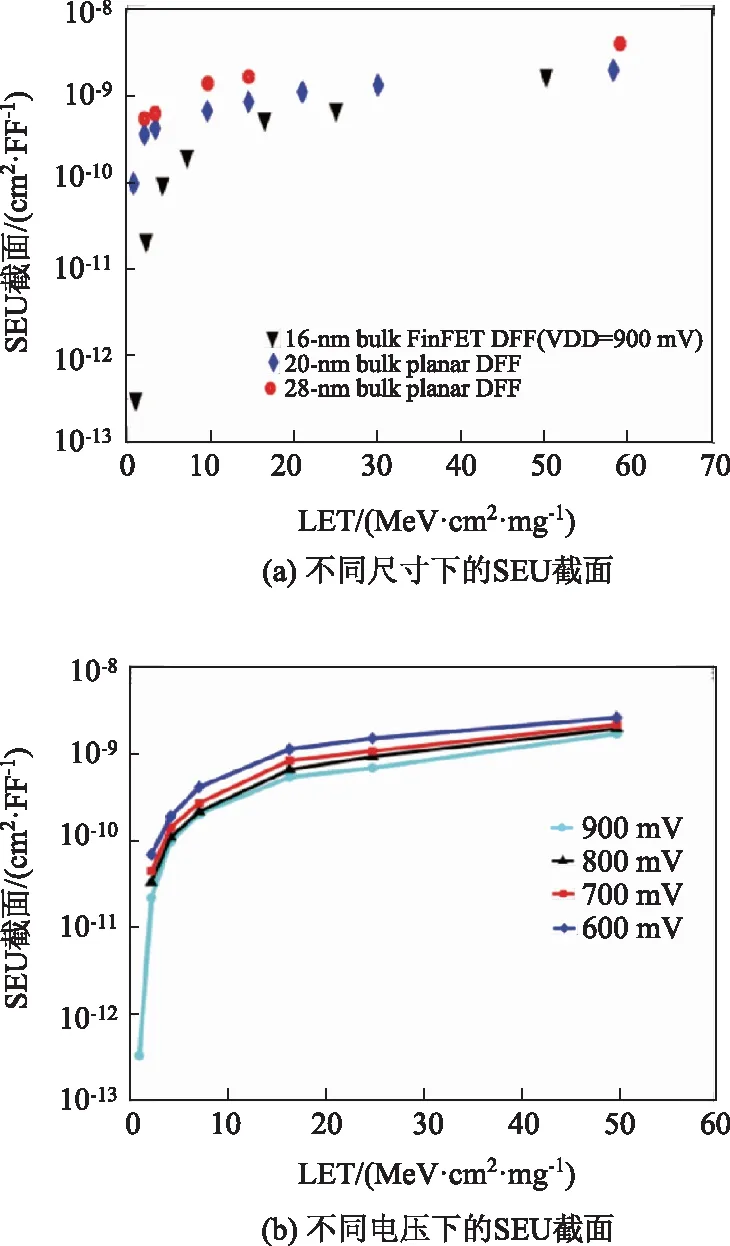

此外,文献[31]通过模拟研究发现,SEU截面和LET的能量紧密相关,对于LET能量较低的重离子,只有当重离子直接穿过漏极才会造成SEU,离子穿过16nm FinFET器件漏极的概率比平面型器件低,所以其SEU截面远小于28 nm;对于LET能量较高的重离子,FinFET器件基体会出现明显的电荷收集,导致不同尺寸下FinFET器件的SEU截面基本相同,如图14所示。因为临界电荷和驱动电流的影响,所以LET能量较低时,SEU截面随供给电压的增大而减小,而LET能量较高时,供给电压对SEU截面的影响较小。

图14 FinFET器件的SEU截面[31]

3.2 工艺参数对FinFET器件单粒子效应影响

工艺参数会影响辐射后产生的电子-空穴对数目及其转移能力,通过调节和优化工艺参数的方式可以达到提升FinFET器件抗单粒子效应的目的,本文从源/漏掺杂浓度、基体掺杂浓度和鳍尺寸三个方面对不同工艺参数下的单粒子效应进行阐述。

(1)掺杂浓度对FinFET器件单粒子效应影响

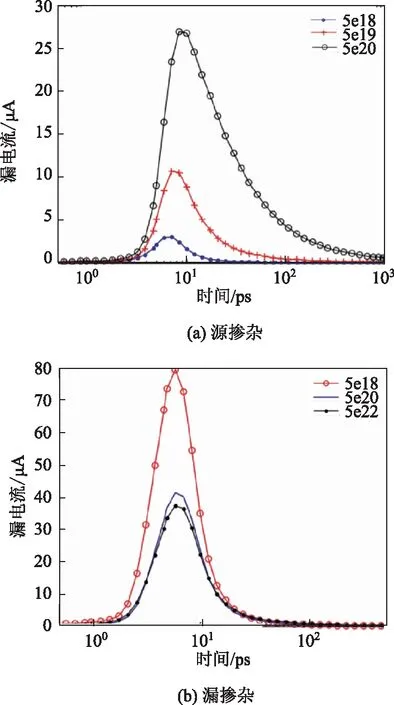

FinFET器件的亚阈值摆幅、关断电流、跨导和阈值电压与源区、漏区和沟道的掺杂浓度紧密相关,所以源区和漏区的掺杂浓度会影响器件性能,进而影响器件的单粒子效应[32-33]。文献[34]采用Sentaurus TCAD进行模拟研究,发现当FinFET器件源端掺杂浓度增加时,SET产生的电流脉冲幅度和宽度也会显著增大;当漏极掺杂浓度增大时,器件漏极电流会随着漏极掺杂浓度增加而减小,达到提升FinFET器件抗单粒子辐照效应的目的,但因为漏极能够中和大量的电子-空穴对,所以脉冲电流宽度变化很小,如图15所示。

图15 掺杂浓度对SET的影响[34]

除了增大漏端掺杂浓度,当衬底掺杂浓度增大时,FinFET器件的最大漏端电流也会降低,且电流变化量大于源和漏掺杂导致的电流变化量。从图16可见,当衬底掺杂浓度下降一个数量级时,离子入射后产生的电流峰值增大了三倍,因此通过提高衬底掺杂浓度能够有效提升器件的抗单粒子辐射性能[34]。

图16 衬底掺杂浓度对SET的影响[34]

(2)鳍尺寸对单粒子效应影响

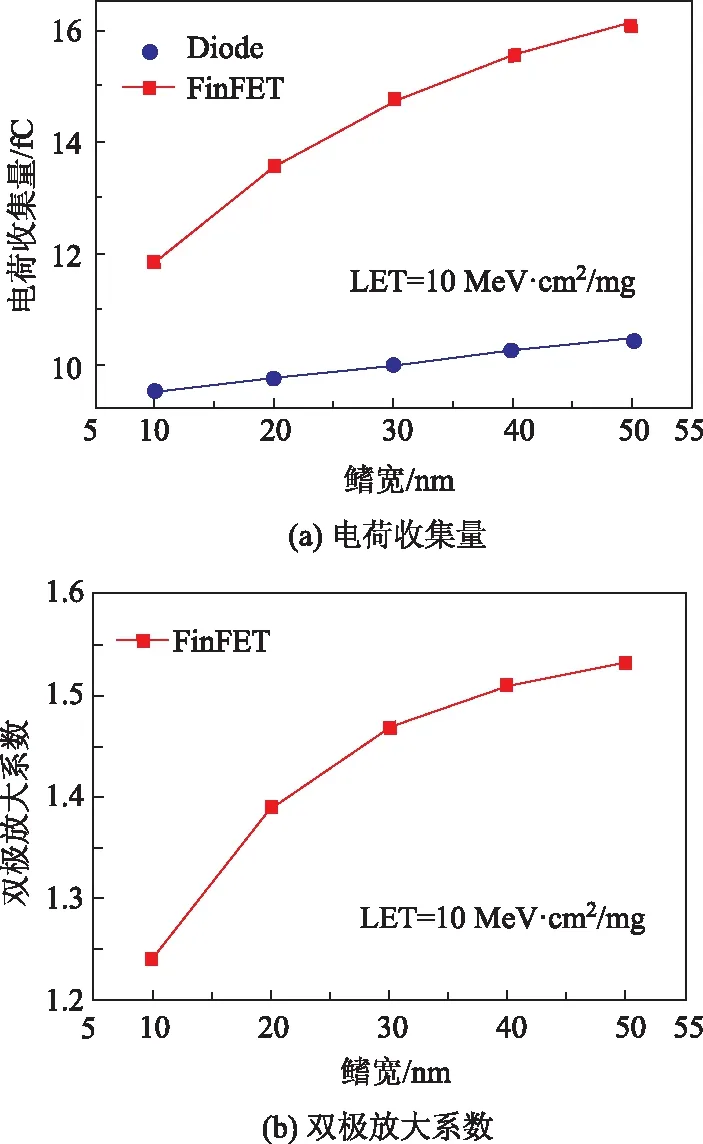

文献[35]通过Sentaurus TCAD仿真,研究了体硅FinFET器件的单粒子效应,发现由源、漏及栅组成的栅双极晶体管,单粒子穿过不会导致源和栅间势垒降低;对于由源、漏及阱组成的阱双极晶体管,单粒子穿过会导致源和漏间势垒高度显著降低,而且从图17可以看出,体硅FinFET器件的SET电荷收集量和放大系数随鳍宽增大而增加,但与鳍高基本无关。

图17 鳍宽对器件性能的影响[35]

对于SOI FinFET器件,文献[36]采用Ca和Kr作为离子辐照源研究了SET,发现LET增大会增大电荷收集量,而且因为窄鳍会对体电势控制增强,所以宽鳍电荷收集能力大于窄鳍;同时栅长减小会使浮体效应增强,进而导致寄生电荷放大作用增强。由于埋氧层会隔离沟道和衬底,因此,漏斗效应和扩散引入的电荷收集可以忽略不计,电荷收集主要来自于源和沟道间PN结和基体沟道电势变化,文献[37]采用Sentaurus TCAD仿真研究SOI FinFET器件,发现当重离子穿过SOI FinFET器件时,鳍长增大会使寄生双极晶体管放大效应降低,而鳍高和鳍宽增大会使寄生晶体管放大效应增强,而且SOI FinFET器件漏极耗尽区的双极放大效应对重离子辐照最为敏感,当入射位置在FinFET器件的漏极区域时,SET瞬态电流达到最大。

文献[38]通过TCAD模拟仿真,发现体硅FinFET器件的电荷收集量和SET脉冲宽度随鳍宽增加而增加,而SOI FinFET器件的电荷收集量和SET脉冲宽度先增大后饱和,前者的电荷收集量和SET脉冲宽度均高于后者,且二者差距随鳍宽的增大而变得更加显著。同时,还发现体硅FinFET器件和SOI FinFET器件发生SEU的LET阈值均随鳍宽增加而减小,相同工艺节点下SOI FinFET器件比体硅FinFET器件的SEU LET阈值大,而且SOI FinFET器件变化速率更快[38-39]。

对于LET值低的重离子,文献[40]通过Sentaurus TCAD仿真,发现当SOI FinFET器件鳍宽固定,SET产生的电荷收集量和临界电荷量均随鳍高增加而增加,但电荷收集量变化率高于临界电荷量,所以LET值低的重离子也会导致位翻转[35, 40]。另一方面,随着鳍高增加,离子入射会产生更多的电子-空穴对,不仅造成SOI FinFET器件漏极电荷收集量增多,还使双极放大效应增大,导致SEU所需的能量降低[41]。同时,随着鳍高增加,虽然SEU LET阈值降低,导致SOI FinFET器件软错误增加,但是在不增加面积的条件下,由其构成的SRAM单元静态噪声容限增大[42]。对于LET值高的重离子,文献[35]发现双极放大系数从1.38增加到1.41,表明鳍高对体硅FinFET器件的双极放大效应影响有限,但由于体硅FinFET器件敏感体增大,所以电荷收集量随鳍片高度增大而增加,如图18所示。

图18 鳍高对器件性能的影响[35]

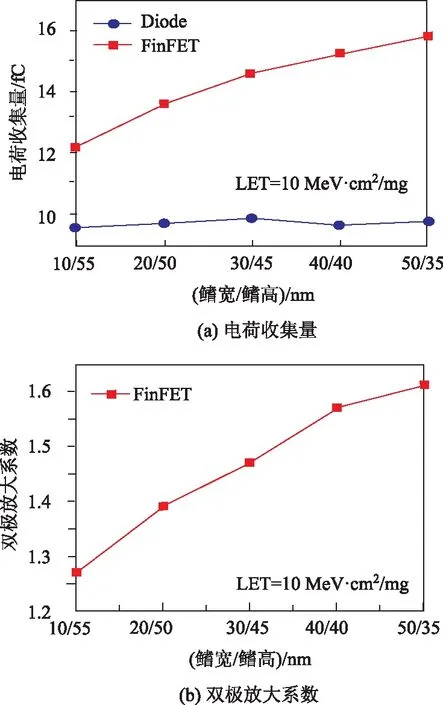

当同时考虑鳍宽和鳍高的变化时,因为鳍宽对双极放大系数和电荷收集量影响大于鳍高,所以在鳍宽增大和鳍高减小的条件下,文献[35]发现体硅FinFET器件的SET电荷收集量和双极放大系数增加,如图19所示。

图19 鳍宽高比对器件性能的影响[35]

4 结 语

作为后摩尔时代技术标志,FinFET器件已经在Intel处理器中得到广泛的应用,但如何实现体硅FinFET器件和SOI FinFET器件的优势融合,达到提高抗辐射性能的目的,一直是FinFET器件发展的难点。本文从FinFET器件的掺杂浓度、结构尺寸和材料种类等多个角度,对FinFET器件的总剂量电离效应和单粒子效应进行了分析,可以归纳为以下四点。

1)通过提高沟道和基体掺杂浓度,减小总剂量电离效应;2)对于体硅FinFET器件和SOI FinFET器件,可分别采用增加和降低鳍宽的方式降低总剂量电离效应;3)采用减小源端和增大漏端掺杂浓度的方式,降低FinFET器件的单粒子效应;4)通过减小FinFET器件鳍宽度,使FinFET器件电荷收集量降低,进而降低其单粒子效应。

除了本文综述的掺杂浓度、尺寸和材料的抗辐射加固方法,还可以从以下三点进行FinFET器件的抗辐射加固,1)改变栅极氧化物生长工艺,采用低温氧化结合掺杂方式制备薄栅氧化层;2)针对SOI FinFET器件,采用源区浅结结构,消除电离辐照导致的背沟道漏电;3)对于由新材料组成的FinFET器件,通过改进工艺降低界面间的失配和缺陷。

目前,FinFET器件抗辐射性能仍是研究的重点和难点,如何改进器件结构和工艺方法,使器件常规性能提升的同时,还能够满足其抗辐射性能的需求,对我国面向航空航天FinFET器件发展具有重要意义。