基于FPGA的IEEE 802.16e标准LDPC编码器设计

2022-07-12李朋涛齐飞林何德华

李朋涛,齐飞林,何德华,李 健

基于FPGA的IEEE 802.16e标准LDPC编码器设计

李朋涛,齐飞林,何德华,李 健

(中国电子科技集团公司第二十研究所,西安 710068)

针对通信过程中突发信道造成的集中错码现象,并且兼顾编码器的时效性要求,设计了一种IEEE 802.16e标准下码长576,码率1/2的LDPC码硬件编码器,通过Verilog语言进行描述,采用并行结构设计和模型矩阵元素预存的方式降低了资源占用量,提高了工作速度,通过仿真、综合与实现结果验证了方案的有效性。

通信;LDPC编码;IEEE 802.16e;Verilog描述

0 引言

通信的目的是将消息及时、可靠、高效地传递给目标。随着现代社会的不断发展,短视频、语音和视频通话得到极大普及,人们对数字化通信系统的可靠性有了更高的要求。如何在发射功率有限,带宽窄,系统复杂度低以及成本尽可能小的情况下设计出满足要求的通信系统就显得尤为迫切。

通常通信系统中消除和降低误码率的有效手段就是信道编码,常用的信道编码技术有汉明码、RS(Reed-Solomon)码、卷积码(Convolutional Code,Turbo)和低密度奇偶校验码(Low Density Parity Check,LDPC)等。Gallager教授在1962年发明了LDPC码,并给出了硬判决译码算法[1];受限于当时的计算和存储能力,人们没有发现LDPC码的优越性。只有Tanner继续研究并发明了Tanner图,其对LDPC码的译码过程进行了直观表示[2];直到1996年,Mackay详细地阐述了LDPC码的理论和实际性能,推广了Gallager的概率迭代译码算法,提出了置信传播译码算法[3]。

随着LDPC码的不断发展,IEEE 802.16e标准将其列为可选编码方案。而后,围绕IEEE 802.16e标准的LDPC编译码器的硬件设计逐渐成为研究热点,本文主要完成码长576,码率1/2的LDPC码编码器设计,提高了通信系统的可靠性。

1 LDPC码在IEEE 802.16e标准中的定义

2 快速迭代编码算法

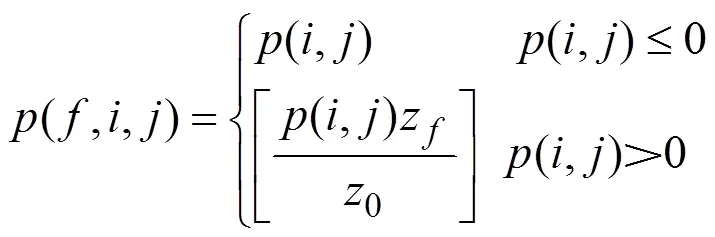

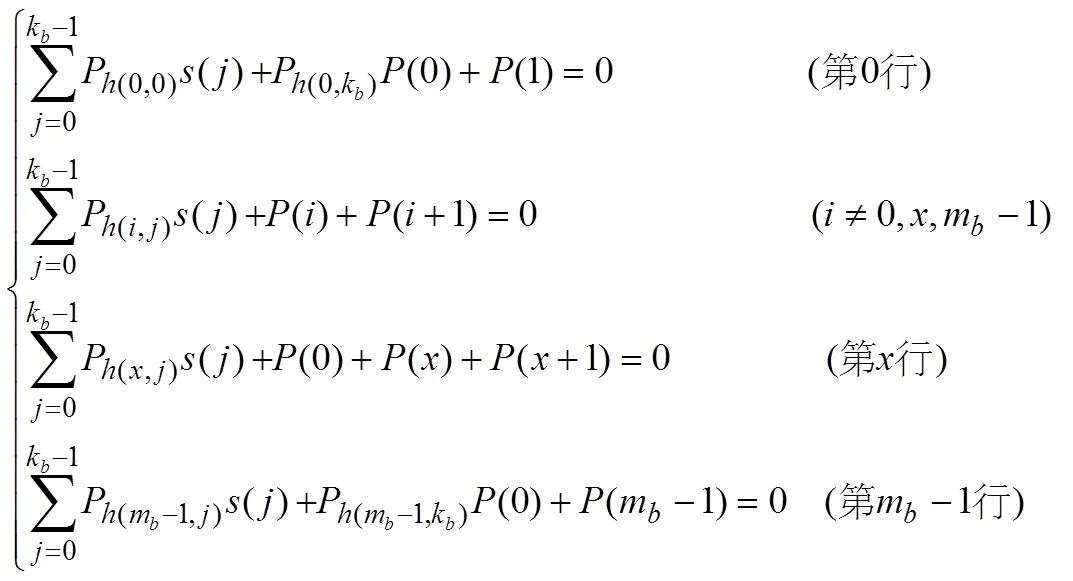

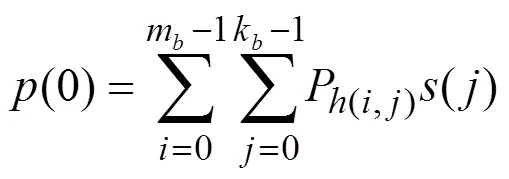

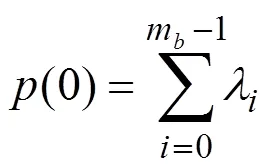

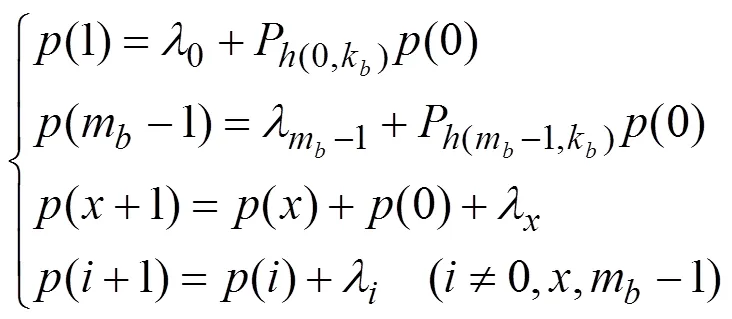

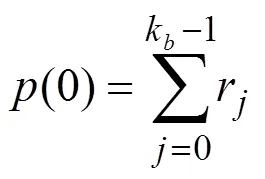

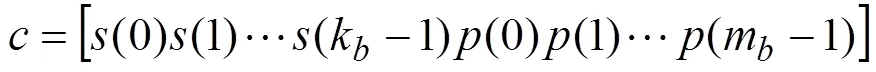

根据IEEE 802.16e提供的基本模型矩阵为校验矩阵模型,本方案采用快速迭代编码算法,其实现过程如下:

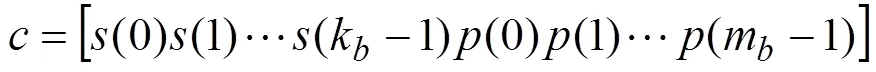

设信息码和校验码组成的码字为:

3 硬件实现

式(8)与快速迭代算法推导式(6)的区别在于,推导式中先进行列加,然后进行行加,而式(8)是先进行行加,再进行列加。

从系统稳定性和资源占用率方面考虑,本方案设计专用编码器,采用FPGA中的ROM IP核对标准中码长576,码率1/2的基本模型矩阵元素进行存储。

3.1 编码器结构设计

结构由串转并模块、核心算法处理模块、并转串模块以及控制模块组成。由于信息块校验处理后送给编码器的是串行数据,因此需要转为并行数据,核心算法模块实现快速迭代算法,编码完成后的并行数据需要重新转为串行,整个过程的顺利执行需要控制模块进行时序控制。

本文设计的编码器模块结构图如图2所示。

的编码过程。

此结构的关键点在基校验矩阵存储ROM模块、乘法移位模块和校验码生成模块的设计实现,下面说明本文的模块设计。

3.2 编码器模块设计

3.2.1 ROM存储模块设计

本方案采用码长576,码率1/2的编码方式,其基本模型矩阵的第一部分为12×12的矩阵,并且最大元素为95,考虑整个编码系统的稳定性及方便实现,ROM存储模块采用12个深度12,位宽8的ROM,其构成示意图如图3所示。

3.2.2 乘法移位模块

当采用循环移位时,需要根据不同的基本模型矩阵元素进行不同次数的循环移位,但是考虑到编码器的低延迟要求,并且在高数据率的情况下,需要采用更高的时钟来完成循环移位操作,时钟过高时不利于时序收敛,整个编码器的可靠性会降低。对不同基本模型矩阵元素采用并行独立的移位结构可以降低时钟频率要求,但是缺点是增加硬件资源开销,因此适合硬件资源充足下的设计。本方案采用并行独立移位结构的设计,通过牺牲硬件资源来降低系统工作时钟频率要求,增加设计的稳定性。

3.2.3 校验码生成模块设计

4 Matlab及FPGA仿真和综合结果分析

表1 综合后不同编码器资源占用量对比

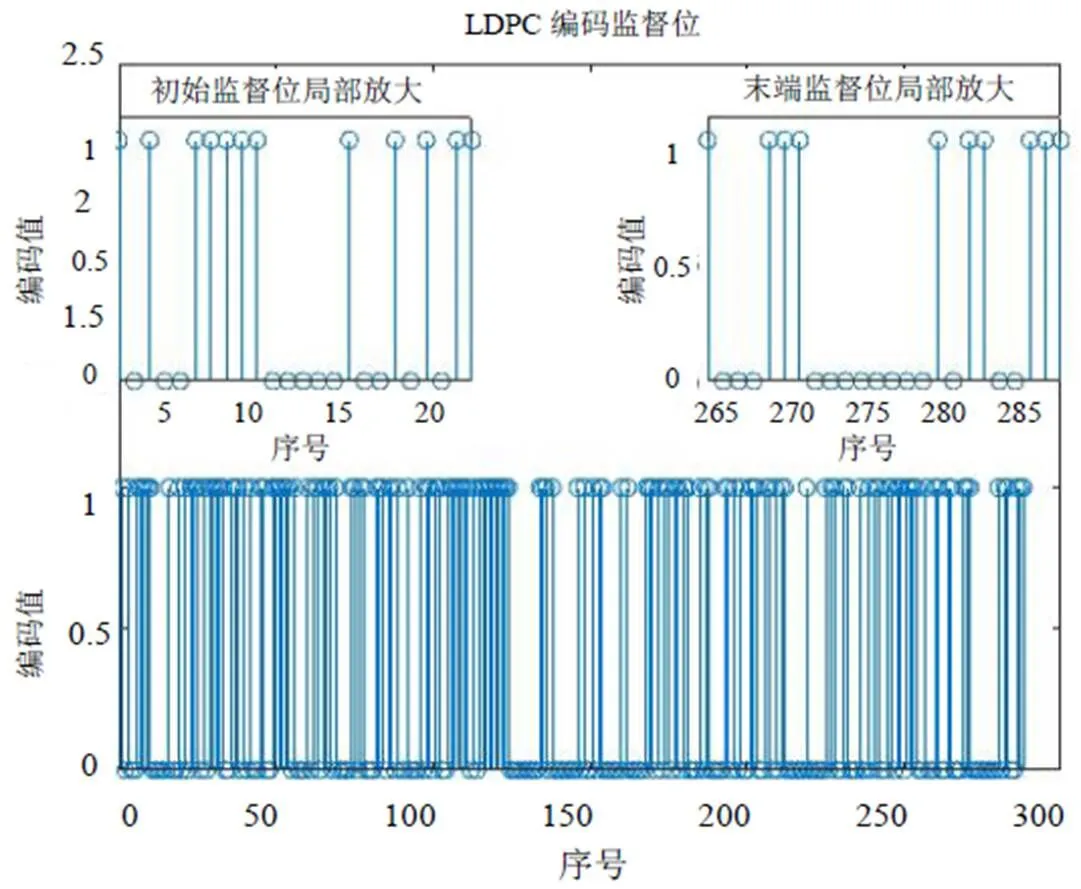

经编码后,长度576,码率1/2的编码器对长度288的数据块编码后输出监督位的Matlab仿真结果如图5所示,其中横坐标为码元序号,纵坐标为码值。监督位长度288,通过局部放大图可以观察到监督码初始16位和末端16位码值。

图5 LDPC编码器监督位Matlab仿真结果

5 结语

本文分析了IEEE 802.16e标准下LDPC码的编码算法,并采用了适合高速率可并行的快速迭代算法,根据算法各部分的功能特点合理设计模块,通过设置相同模块的不同结构进行了编码器性能对比,选取了适合方案要求的高性能LDPC编码器。通过Matlab与Vivado仿真结果对比可以验证编码器的有效性,与其他编码方案对比,本方案资源占有量较少,工作速率高,因此是满足要求的高效编码器。

[1] R.G.Gallager. Low Density Parity Cheek Codes[J]. IRE Transactions on Information Theory, 1962(8): 21-28.

[2] R.M.Tanner. A Recursive Approach to Low Complexity Codes[J]. IEEE Transaction on Information Theory, 1981(27): 533-547.

[3] D.J.C.Mackay, R.M.Neal. Near Shannon Limit Performance of Low Density Parity Check Codes[J]. Electronics Letters, 1997, 33(6): 455-457.

[4] 甘振华. IEEE 802.16e标准LDPC码编译码器设计与FPGA实现[D]. 上海:上海师范大学,2012.

[5] 郭黎利,陈洪雨. 基于FPGA的IEEE 802.16e的LDPC编译码方法[J]. 计算机应用,2017(36):49-53.

IEEE 802.16e Standard LDPC Encoder Design Based on FPGA

LI Pengtao, QI Feilin, HE Dehua, LI Jian

Aiming at the phenomenon of concentrated error code caused by burst channel in communication process, and considering the timeliness of encode, a LDPC code hardware encoder with length of 576 and bit rate of 1/2 in IEEE 802.16e standard is designed, which is described by Verilog, adopts parallel structure design and element prestorage to reduce the resource consumption, and increased working rate, the efficiency of the scheme is verified by simulation and synthesis and implementation results.

Communication; LDPC Encode; IEEE 802.16e; Veriog Describe

TN929.1

A

1674-7976-(2022)-03-212-07

2022-03-07。

李朋涛(1992.05—),陕西西安人,硕士研究生,主要研究方向为通信信号处理,数字逻辑设计。