基于CPRI 协议的多通道通信设备硬件实现方案

2022-07-11何君燕

何君燕

(中国电子科技集团公司第七研究所 广东省广州市 510310)

1 通信系统架构

现代通信系统朝着宽频带、大容量、远距离、多用户、高保密性、高效率、高可靠、高灵活性的数字化、智能化和综合化方向发展。随着通信系统的不断发展,通信系统的传输能力越来越高,通信设备内部的信息处理速率也越来越快,因此对通信设备内部软件、硬件的高速传输性能提出了更高的要求。

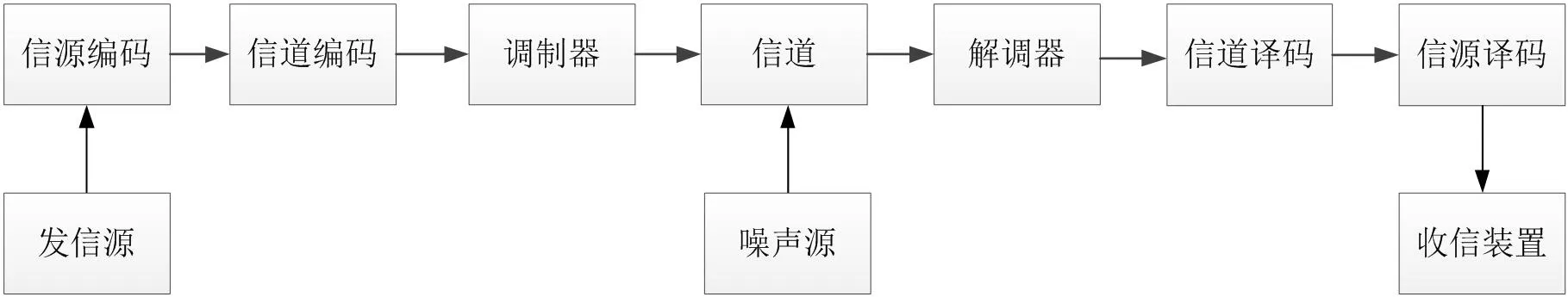

通信系统的传统架构如图1 所示。传统的通信设备的调制解调器与信道接口均采用模拟射频连接器进行互连。

图1:通信系统的传统架构图

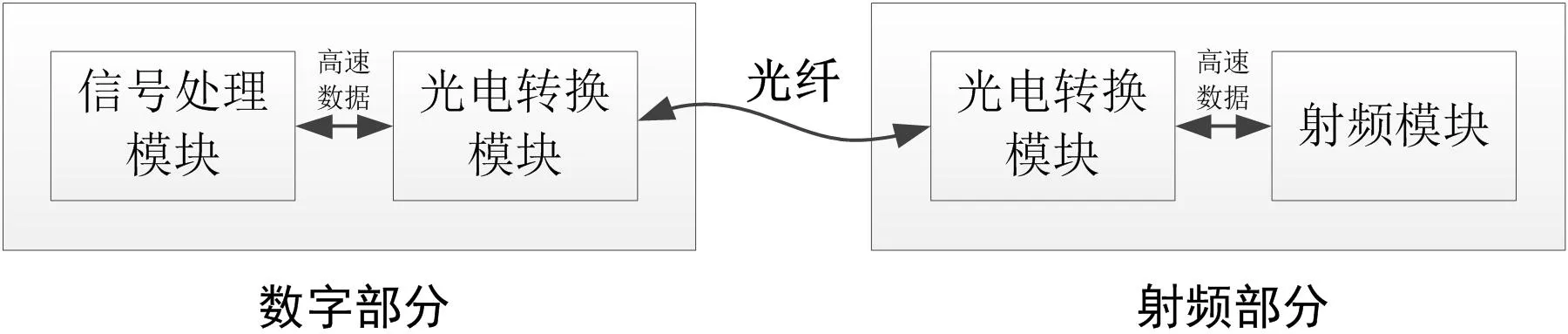

为了实现大容量远距离的传输需求,通信系统通常采用光纤作为传输媒介,将原通信系统内部的调制解调与信道的接口进行数字化处理,调制器在进行发送处理时,将调制后的数据变换为适合光纤传输的光信号,解调器在进行接收处理时,将光信号变换为待解调的数据;射频端根据收发控制实现光信号和电信号的相互转换;由于光纤在远距离传输时的损耗较小,对通信系统的传输性能基本没有影响,因此采用光纤传输技术的通信设备得到越来越广泛的应用,其原理框图如图2 所示。

图2:采用光纤传输的通信系统原理框图

随着通信设备的应用场景越来越广泛,为实现更大容量、更远通信距离的传输需求,设备形态由单通道向双通道甚至多通道方向发展,而随着高性能的微处理器的性能不断提升,核心处理板卡也朝着高集成化的方向发展,如何实现高集成化处理板卡对多信道通信设备的统一传输控制成了一个难点问题。

针对多信道通信设备常用的传输控制方式是针对每一个通道采用独立的光纤控制链路,和每一个通道需使用一组独立的光电转换模块,并且需要单独的一路光纤,设备内部和设备间的连接线缆数量较多,设备互连的可靠性也不高,同时也缺少较好的扩展能力。这种多信道通信设备控制方式如图3 所示。

图3:传统的多信道通信设备架构

2 常用高速数据传输接口

随着高速总线技术的不断发展,通用的基带射频接口协议逐渐引起各通信设备厂家的重视,目前主要采用两种开放式接口标准:无线设备和无线设备控制部分分离的CPRI 接口(Common Public Radio Interface)标准和基带处理、射频、网络传输和控制层面都分离的OBSAI(Open Base Station Architecture Initiative)标准。CPRI 协议的实现较OBSAI相对简单,已广泛应用到各类通信设备中,近年来发布的大部分高性能微处理器中也支持CPRI 接口,因此可采用CPRI接口作为多信道通信设备的控制接口,将多个无线信道的控制和业务数据通过CPRI 接口汇聚到统一的高速接口上,经过光电转换和光纤传输后,在无线信道端进行数据的还原,从而达到减少光电转换模块和内外部互连线缆的目的,进一步降低设备的复杂度,提高设备的可靠性。采用CPRI 接口的多信道通信设备架构如图4 所示。

图4:采用CPRI 接口的多信道通信设备架构

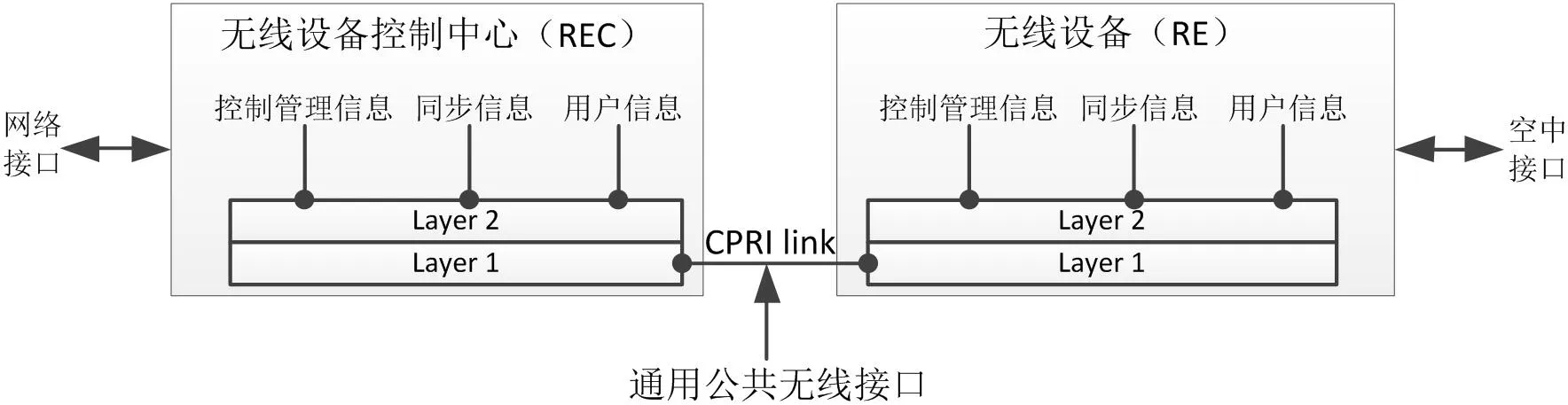

CPRI 是业界通用的无线通信设备数字部分和射频部分之间标准通信接口,其协议架构和帧结构可用于实现无线通信设备的数据部分(简称REC)和射频部分(简称RE)的同步信息、控制管理信息和用户信息交互,这三种信息采用时分复用的方式实现接口传输。CPRI 协议的基本结构图如图5 所示。

图5:CPRI 接口基本结构框图

CPRI 协议标准中定义了两个协议层和三个数据面。Layer1主要实现通信中编解码、光口/电口的规格、帧的格式、传输速率、传输的距离等内容的规定,是协议层中的物理层。Layer1 的数字信号可以采用双绞线或者电缆使用电信号的形态进行传输,也选择光纤实现远距离传输。对于线路的传输速率可以从以下三种中选择:614.4Mbit/s,1228.8Mbit/s 和2457.6Mbit/s,这里的速率指的是光纤种串行信号的速率。在Layer1 层上完成了8B/10B 的数字编码,从而得以保证经过编码后的有效数据中有足够的高电平和低电平进行变换翻转,在对端的接收处理过程则可从有效数据中提取出所需要的同步字节。Layer2 层即是MAC 层,该层主要明确了媒体访问控制、数据检错、数据保护功能等。MAC 层还规定了一个帧结构,用于实现同步,该帧结构具有两种,分别为基本帧以及超帧,其中每一个基本帧划分为16 个时隙,使用的帧频率为3.84MHz 的;每个基本帧中的每个时隙的大小根据传输线路中的需要传输的比特率的大小来分别定义为1B、2B 和4B。一般定义第一个时隙使用为控制时隙,传输控制和管理数据;另外15 个时隙为用户数据时隙即I/Q 数据时隙,主要实现I/Q 数据流的成帧传输。超帧则由256 个基本帧组成,256 个基本帧的控制时隙共同构成超帧的控制结构。同时定义了快速C/M 通道和慢速C/M 通道。用于传送控制和管理类的数据,用来维护传输链路。

标准中的三个数据面一般包括同步面(Synchronization Plane)、用户面(User Plane)和控制与维护面(C&M Plane),与承载的数据信息保持一致。同步面承载的是与同步和定时相关的数据、用户面承载的是有效的用户数据,即IQ 数据,主要是基站和终端之间交互的有效的用户数据。控制与维护面承载 Layer1 及以上的高层相关的操作维护信息。

3 多信道通信设备硬件实现方案

常用的CPRI 硬件实施方案有以下几种:

(1)采用PMC7830 或PMC7832 芯片。这一类芯片把完整的CPRI 协议封装到一块芯片中,只留出接口供用户使用,操作方便,但可扩展性不强。

(2) 以FPGA 与SCAN25100 为主, 用FPGA 实现CPRI 的成帧、解帧及数据接口设计,SCAN25100 完成8B/10B 编解码和高速串并转换。此种实现方案的特点在于链路层的帧协议修改方便,而物理层由专用芯片完成,使用简单性能稳定。

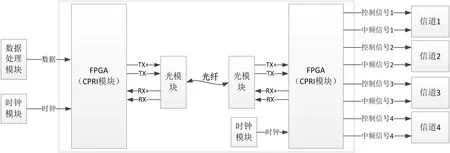

(3)采用自带ROCKERT IO 的FPGA,通过单芯片即可实现数据接口、CPRI 协议和传输控制,能有效降低成本,增加系统可靠性。综合考虑制造成本、设备体积、系统可靠性、可扩展性和移植性,本设计采用第三种方案,多信道通信设备的CPRI 接口控制部分包括以下几个模块:时钟模块、FPGA 模块和光模块等,如图6 所示。

图6:CPRI 接口的硬件原理框图

本设计中FPGA 选用Xilinx Spartan-6 系列XC6SLX25T芯片,该芯片内置高速GTP 串行收发器,最高速率达3.2Gb/s,并且采用低内核电压供电,功耗低、可靠性高,完全满足CPRI 协议线速率设计需求,具有良好的可靠性。

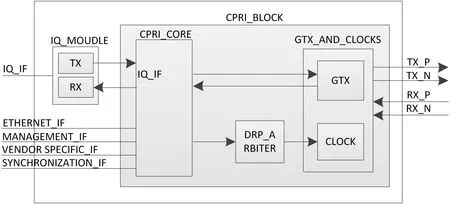

Xilinx 公司在2013 年已经发布了基于CPRI 协议V5.0版本的IP 核,目前Coregen 中对应IP 核版本为CPRI V6.1。使用Xilinx 公司的Coregen 工具可生成相应IP 核,该IP 核分为Master 和Slaver 两种模式。其Master 模式应用在REC 端,Slaver 模式应用在与REC 相连接的RE 端,这样就构成了一个CPRI链接。通常情况下CPRI核与GTX(Gbit收发器)相连接,IP 核中实现CPRI 协议的链路层,封帧好的数据通过GTX 的8B/10B 编码,转换成串行数据通过光纤传输。其设计框图如图7 所示。

图7:FPGA 内部CPRI 接口设计框图

时钟电路选用Silicon Labs 公司的SI5324C-C-GM 芯片,该芯片是精密时钟倍频器/抖动衰减器,用于抖动性能小于1ps 的应用,具有两时钟输入(2KHz-710MHz)和两路时钟输出(2KHz-346MHz),回路带宽4-525Hz,满足ITUTG.8251 抖动指标,适用于光纤传输系统、数据交换、无线基站等应用。使用CPRI 接口模块传输数据时,REC 和RE之间用光纤连接,两边时钟源相互独立,不同时钟在频率上有偏差,此时REC 和RE 的时钟源不能达到同频同相。使两边时钟源达到同频同向是硬件电路设计中一个至关重要的模块。在使用Xilinx 公司的CPRI IP 核时,它为Master 和Slave 模式,分别用在REC 和RE 中。由于REC 是主控,因此RE 的时钟源要跟随REC 的时钟源,从而使两边的时钟源达到同频同向的目的。时钟电路设计框图如图8 所示。

图8:时钟电路设计框图

光模块选用HBP533G-S5DT 单芯双向一体光模块,单纤双向是指双方向的数据信号采用不同的波长在同一根光纤中传送,可以节省一半的纤芯资源。目前主流光模块厂商均已能提供单纤双向的CPRI 光模块。

通过对多通道通信设备数字部分与射频部分的接口电路进行器件选型和原理设计,设备的集成化程度更高、成本也可以得到有效控制,同时由于采用了扩展性强的Soc 芯片,整个系统的可靠性、可扩展性和可移植性都有了很大的提升,可显著增强设备的传输性能。

4 结束语

通过采用基于CPRI 协议的高速数据接口硬件方案,可有效解决传统多通道通信设备控制复杂,可靠性低等问题。目前,高性能集成电路的处理能力越来越强,多通道通信设备的传输控制实现将更加便捷,能满足通信系统往更大容量、更远通信距离的发展需求。