基于FPGA 的快速引导数字信道化接收机设计

2022-07-11毛凯文刘云学

毛凯文 刘云学

(烟台大学物理与电子信息学院 山东省烟台市 264005)

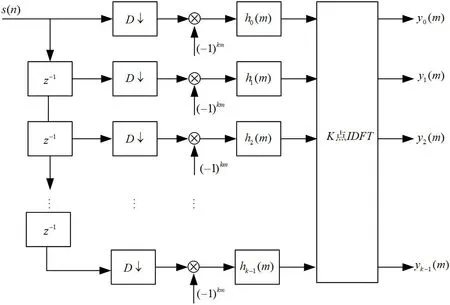

随着科学技术的迅猛发展,电子对抗在如今的信息化战场中有着至关重要的作用,电子战环境中各种信号所占用的频率范围更广,输入密集。因此,在这种高密集的信号环境下,电子战接收机需要有很强的适应能力,同时需要对接收到的大量信息进行实时处理。传统的信道化技术和接收机技术是基于模拟器件搭建,这种基于模拟器件搭建的接收机器件和资源消耗较大,特别是当信道数目增加的时候,器件和资源消耗就会大幅增加,对接收机的性能影响很大。随着数字信号处理技术的发展,用数字化的方式来实现信道化技术具有重要的意义。

某宽带电子对抗设备,将整个频率范围划分为多个频段,这就需要一个快速检测与引导模块尽快检测到信号的出现并切换到对应频段,完成进一步的处理。检测与引导模块首先将宽带信号进行分频,然后利用高速ADC 将分频后的模拟信号变成数字信号,进一步进行数字化处理完成信号检测与快速引导功能。

针对设备需求,本文基于数字下变频的数字信道化结构推导出信道化高效结构。本次设计采用了基于多相滤波的无盲区高效数字信道化接收机结构,将2.5GHz 采样率的信号均匀划分成16 个子信道,每个子信道瞬时工作带宽为156.25MHz。这样就可以对每个子信道进行高效处理,同时对瞬时带宽内的信号进行全概率接收,具有多信号并行处理的能力。通过FPGA 进行了数字信道化接收机的设计和综合,由于系统运行时钟频率较高,在完成数字信道化接收机的基础上还需要实现快速频率引导和电子对抗,这样就需要仔细设计信号处理环节,在保证性能的同时尽可能采用精简的运算,尽可能减少系统时延以降低测频时间。本FPGA 还需要完成别的功能,需要尽可能少消耗FPGA 资源,特别是乘法器资源。本次设计采用Xilinx 公司的XC7K410T-FFG900 芯片完成了2.5GHz 采样率16 子通道数字信道化接收机。

1 数字信道化原理与结构推导

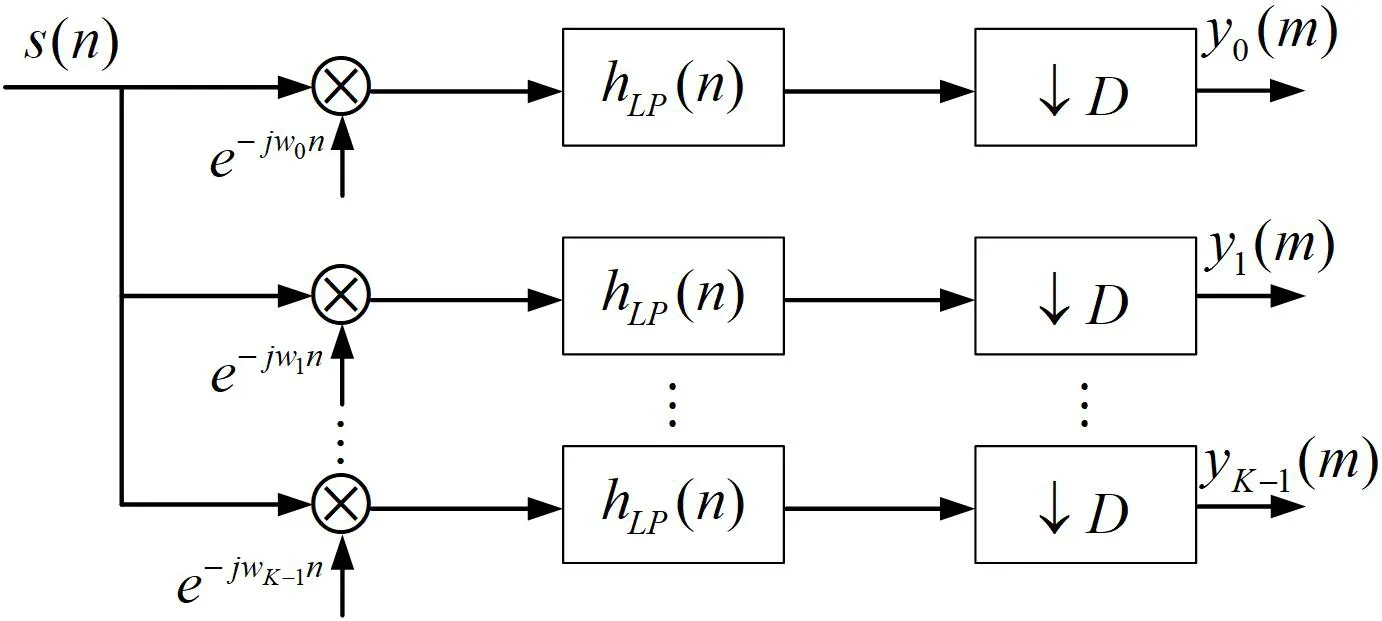

数字信道化可以看为,用滤波器组实现的多通道数字正交下变频。输入信号首先通过数字乘法器进行下变频,将感兴趣的频段移至基带,并通过低通滤波器滤掉不需要的信号。其原理如图1 所示。数字信道化的核心思想是把一个带宽较宽的信道划分为多个带宽相对较窄的子信道,并利用抽取器在输出端得到低速率子信道,这样就便于后续信号处理。

图1: 基于数字下变频的数字信道化结构

假设图1 中h(n)为FIR 低通滤波器的冲击响应,阶数为N 阶,K 为信道个数,D 为抽取倍数,在信道化结构中信道个数K与抽取倍数D满足K=F*D(F>0)。s(n)为输入信号,w(k=0,1,…,K-1)为各个信道的中心频率,则图1 结构中的第k 个子信道的输出为:

2 FPGA的实现

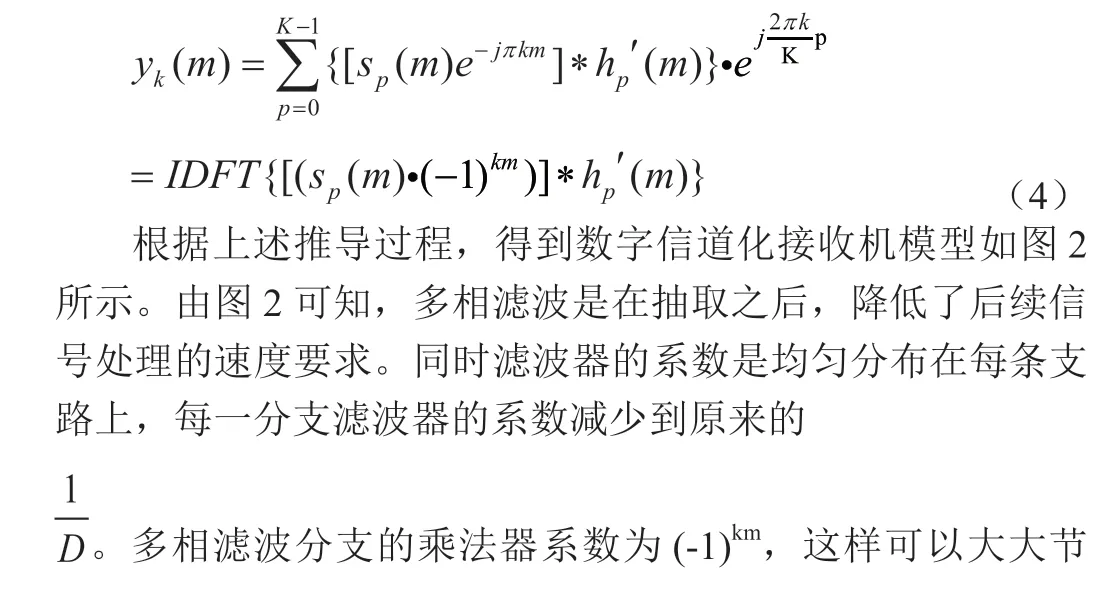

FPGA 实现主要包括数字信道化过程和后续信号处理两部分。由图2 可知数字信道化主要包括数据抽取、多相滤波、并行傅里叶变换。后续信号处理主要是根据信道化结果进行测频。

图2: 数字信道化接收机高效结构

2.1 数据抽取

模拟信号只有变成数字信号才能被其它器件处理,高速ADC 芯片采用TI 公司生产的ADC083000,可将信号数字化为8 位分辨率,实际有效位为7bit,采样率高达3.4GSPS。FPGA 接收AD 采集的8 路信号,每一路频率为312.5MHz,即系统运行时钟频率也为312.5MHz。

2.2 多相分支滤波器

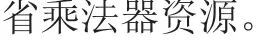

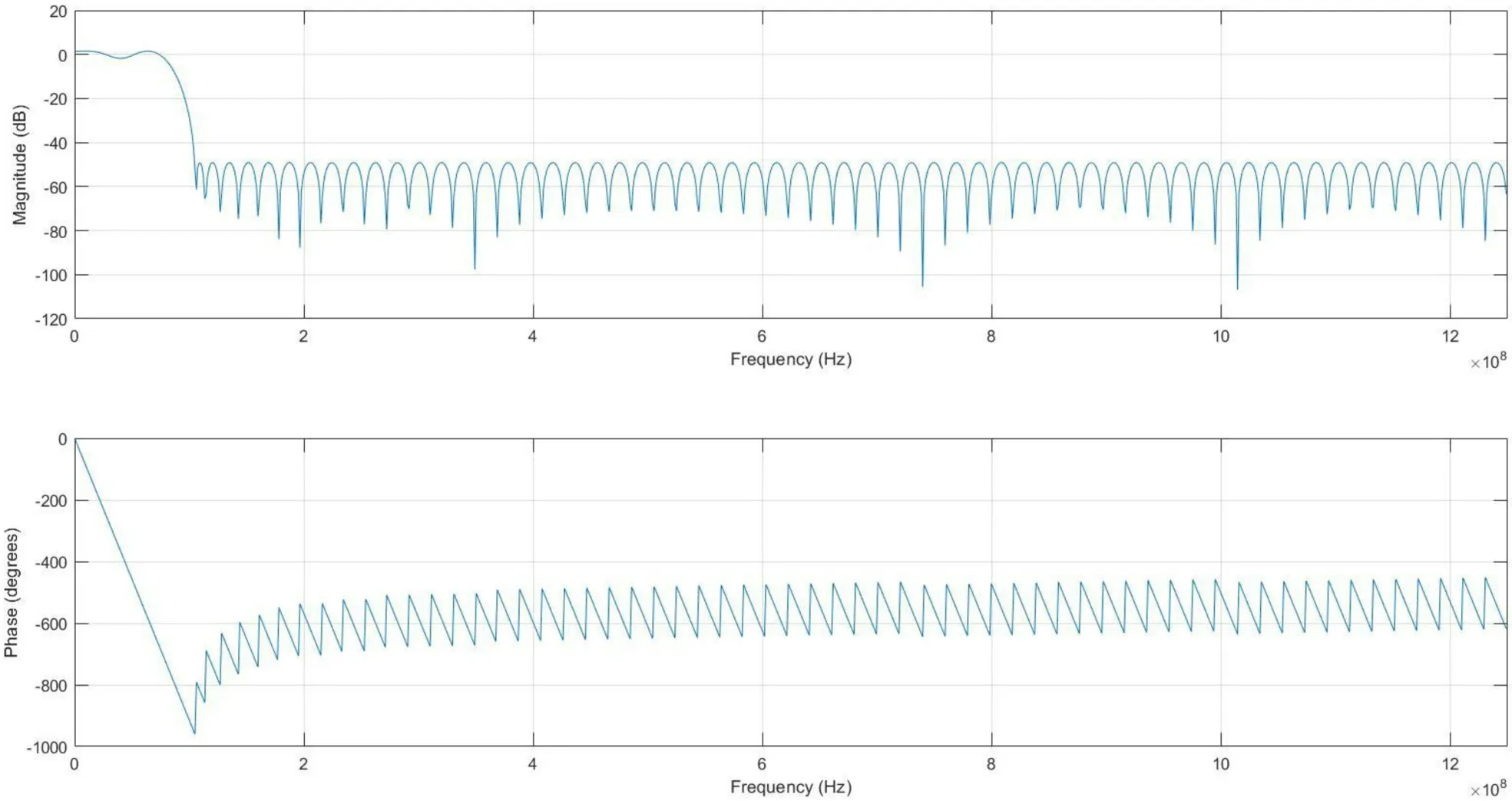

数字滤波器是由数字乘法器、加法器和延时单元组成的一种算法和装置。常规信道化设计中FIR 低通滤波器设计指标为:通带波纹为1dB,阻带衰减为50dB,满足上述要求的FIR 滤波器阶次为256 阶。这样延时很大,又消耗了较多的乘法器资源。本文提到的系统中射频信号SNR 较高,就有可能通过调整数字滤波器通带内纹波的大小,在这种情况下测频的精度还能够满足的话,就能够降低滤波器的阶次。本设计增加了通带内的纹波,将通带平坦度增大为到3dB,阻带衰减保持50dB 不变,本次设计采样频率为2.5GHz,每一子信道的带宽为156.25MHz,通带截止频率为78.125MHz,阻带截止频率为104.6875MHz,最终滤波器阶数降低到128 阶。因此就大大降低了测频延时,也能响应减少乘法器数量,该滤波器的幅频响应如图3 所示。

图3: 滤波器频响图

多相分支滤波器的本质就是按照相位把原型数字滤波器的系数均匀划分成多个不同相位的组,构成多个分相,并且在每个分相上进行滤波的过程。本次设计的滤波器阶数为128 阶,信道数为16,则每一相分支滤波器的系数为8,在硬件上可以通过乘法累加器实现,这样大幅度减少滤波器阶次既可大大减少乘法器的使用量,又可大幅度降低了延时。

2.3 并行傅里叶变换

输入信号经过抽取和多相滤波之后,需要进行IDFT 运算才能得到最后的信道化结果,而在实际中,更为广泛的是采用快速傅里叶变换。快速傅里叶变换可以大大减少运算量,提高系统处理能力。FPGA 的并行操作和流水线结构,与快速傅里叶并行迭代的算法过程可以完美的结合。信号通过滤波器后输出为16 点实数,16 点FFT 可以用Radix-2 或者Radix-4 结构来实现,通过Vivado 综合得到使用不同结构实现FFT 时整体DSP 资源消耗如表1 所示。

从 表1 可 知,用Radix-4 代 替Radix-2 实 现FFT 整 体DSP 资源消耗明显减少,故选择Radix-4 来实现FFT。

表1: DSP 资源消耗对比

2.4 测频模块

测频模块位于信道化的后面,本系统的射频输入信号的信噪比较高,输入信号信噪比在15dB 左右,而经过16 级信道化后信号的信噪比得到了进一步的增强。测频常用方法主要有Rife 算法、M-Rife 算法、瞬时相位法和Kay 算法等方法。经过仿真验证,Kay 算法的测频精度远优于设计指标125KHz(射频信号分频后),另外其精度也优于瞬时相位测频法;虽然在很多情况下Kay 算法的测频精度比Rife 和M-Rife 要差,但是其时延低于前者,且精度又能满足要求,因此本设计采用了Kay 算法来进行瞬时测频。

信道化后输出信号的IQ 分量,对每个信道采用CORDIC 算法计算每个信道信号的瞬时相位,然后采用Kay算法测频。Kay 算法是一种加权差分算法,Kay 算法测频一般步骤为:

3 板级测试

图4: 测试流程图

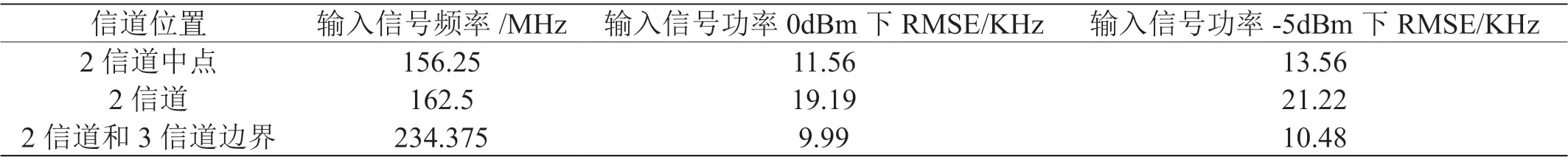

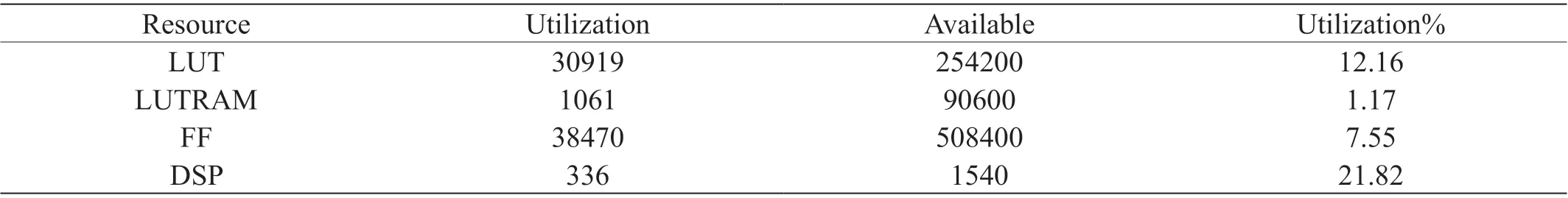

由图5 可知,输入信号频率为162.5MHz 位于第2 信道,随机选取测频稳定输出值,如图5 中某一时刻测频输出值为1026,代入式(11)得实际频率为162.479MHz(保留三位小数),信道化接收机重要的测频功能验证成功,接着把逻辑分析仪抓取的数据保存并导入MATLAB 中分析。对其测频值求RMSE,RMSE 反应接收机测频精度。表2 为输入射频信号功率为0dBm 和-5dBm 情况下频点为156.25MHz、162.5MHz、234.375MHz 测频分析结果;表3 为整个系统部分资源消耗占比,系统运行最高时钟频率为312.5MHz。

表2: 输入信号功率0dBm 和-5dBm 下测频分析结果

表3: 整个系统部分资源消耗占比

图5: 输入信号频率162.5MHz 测频结果

由表2 可知本文提出的信道化高效在信道中点和边界敏感点都能进行较精确的测频,远远优于测频精度指标125KHz。由表3 可知,整个系统DSP 资源消耗仅占21.82%左右,FPGA 还剩下较多的逻辑资源,可以用来扩展其它功能。

4 结论

综上所述,本文结合工程实际,完成了2.5GHz 采样率16 子通道数字信道化接收机快速频率引导模块的FPGA 实现。采用基于多相滤波的高效数字信道化接收机模型,从时延、乘法器资源消耗及测频精度出发,仔细设计并优化了各个信号处理环节,提高系统的整体工作性能。Vivado 综合后的整体DSP 资源消耗仅占21.82%,这样大大节省了乘法器资源有利于功能扩展,同时尽可能降低了时延,该模块测频精度也远远优于测频指标。从板级验证结果知该结构简单、能够实现快速测频、有效降低运算量和逻辑资源等特点,实现了预期的要求。