基于AM335X的信号完整性分析

2022-07-07陈林楷黄中铠

陈林楷 黄中铠

(广东工业大学 广东省广州市 510006)

随着高速数字电路工作频率不断增加,信号升降时间不断缩短,电路集成率不断提高,反射、串扰、振铃、衰减等信号完整性问题日益突出,但这些势必会削弱系统的性能,干扰系统的正常工作。当传输线上的电路中数字信号的延时大于其上升沿一半的时间,或者当数字逻辑电路的频率达到或超过45-50MHz时,则该电路可称为高速电路。AM335X是TI的32位精简指令集计算机处理器,其采用ARM Cortex-A8架构,其内部时钟频率可达1GHz,其芯片接口通信的信号速率可以达400MHz,是一个典型的高速电路系统。本文基于AM335X的系统设计与实现,对系统设计与高速仿真中涉及的信号完整性问题进行了分析与研究,以缩短PCB设计周期,提高研发效率。

1 信号完整性

信号完整性(Signal Intergrety,SI)是指高速电路信号线中信号的质量。在规定时间内信号能不失真地从信号源端传送到负载端,则称该信号是完整的。信号完整性差并不是由单一因素造成的,而是由多种因素共同造成的,主要的信号完整性问题包括反射、串扰、损耗等。具体来讲,信号完整性是指信号在互连线上的质量,即信号在电路中对正确的时序和电压作出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅度到达接收器且不损坏接收器的情况下,就表明该电路具有较好的信号完整性。反之,当信号不能响应或者误响应时,就出现了信号完整性问题。

在高速PCB中,当信号沿传输线传播时所受到的瞬态阻抗发生变化,则一部分信号将被反射,另一部分信号发生失真并继续沿传输线传播下去。信号反射是信号完整性最基本问题之一,是单一网络中所有信号质量问题的根源。反射是传输线中的回声,如果源端、负载端和传输线的阻抗不匹配,就会引起信号反射,信号能量不能被完全接收,同时一部分反射回源端。反射会导致接收端信号变弱,信号的失真会使信号质量下降,并导致逻辑电平误判或者元器件的不正确触发,甚至造成器件损坏。根据传输线、驱动器、接收器的特性阻抗,采用一定的阻抗匹配来减少和消除反射,从而使源、负载端反射系数为零来抑制反射。在实际的PCB设计中,可以通过电阻串联端接方式、电阻并联端接方式、RC并联端接(AC并联端接)、戴维南端接或者肖特基二极管终端端接的方法进行传输线阻抗匹配,但在金手指、贴片器件、插接器件的焊盘和传输线的连接处不可避免地会出现线宽的变化,从而导致信号阻抗的不连续性而产生信号反射,此时可以采用添加泪滴的方法使阻抗由突变转为渐变,以减小信号的反射。但总的来说还是要尽可能减少阻抗变化的程度和阻抗不连续点的数量,以便改善信号质量。

当一个信号沿传输线传播时,由于邻近传输线的电磁耦合会产生不希望的电压噪声,这称为串扰。这种串扰是由于两根信号线之间的耦合,即由信号线之间的互感和互容耦合引入的。电容耦合触发耦合电流,电感耦合引起耦合电压。串扰过多会导致信号误触发,导致系统工作异常。如果受害线上也有信号传播时,受害线反过来就变成了攻击线,而攻击线就变成了受害线,此时两条线会互相干扰。串扰有近端串扰以及远端串扰之分。其中近端串扰,缩写为NEXT,是衡量单链路/通道的一个性能参数,测量从攻击传输线耦合到被攻击传输线的传输线近端(源端)信号。远端串扰缩写为FEXT,也在一个通道内测量,远端串扰与NEXT有很多相似之处,但其是在传输线的远端(负载端)测量。一般情况下在布线过程中,当遇到串扰问题时,可以加大线间距,或者将传输线由微带线变为带状线。同层信号之间的串扰无法避免,虽然增加线间距可以改善串扰问题,但是通常印制电路板上的空间有限,线间距受限制无法无限增加。

2 IBIS模型与Hyperlynx仿真软件

信号完整性仿真模型主要有IBIS模型、SPICE模型、VHDL_AMS模型等。IBIS(Input/Output Buffer Information Specification)模型是一种基输入输出缓冲器的电压电流曲线的快速、准确建模的模型。它是一种反映了芯片驱动和接收电气特性的国际标准。具体来说,IBIS模型提供了一个标准的文件格式来记录输入输出接口类型、输出阻抗、上升/下降时间和输入负载等,作为驱动源的参数,用于计算和模拟高频反射,如反射和串扰。工程人员可以使用该模型配合仿真软件以及实际的线路来分析印制电路板上信号的完整性问题。IBIS目的是在于不向用户提供实际电路信息的情况下提供电路的行为方面信息。该模型以文本格式生成,其主要包含了电流与电压(I/V)和电压与时间(V/T)等数据,使用之前需要先检查的内容包括其驱动强度,曲线的单调性、漏电流、内部端接电阻阻值以及上升沿下降沿的斜率等。目前IBIS模型受到半导体制造商的欢迎和支持,现在各大半导体器件制造商和EDA公司都支持IBIS规范,提供适当的IBIS模型和软件仿真工具以便工程开发人员使用。

Mentor Graphics公司的信号完整性分析工具HyperLynx是非常好的信号完整性仿真软件,其包含两个基本工具LineSim和BoardSim,分别用于前仿真(原理级)和后仿真(PCB级)。HyperLynx可以在电路板上实现信号过信号的完整性仿真。通过对仿真结果的分析,可以消除设计风险,建立设计约束规则,提高设计效率,缩短开发周期。

3 AM335X系统仿真与分析

3.1 硬件系统仿真平台搭建

为了验证理论推导的正确性及优化对设计方案的有效性,解决以AM335X为主控的嵌入式硬件平台中所遇到的信号完整性问题,为硬件设计提供一套重复可用的设计规范流程,本文采用具有代表性的硬件产品,系统框图如图1所示。本文源端的模型采用TI提供的AM335X的IBIS模型,而负载端采用Micrion官网提供的MT41J256M16RE的IBIS模型,其接口类型为DDR3,采用“8bit预取”技术,其IO频率可达1600MHz。源端和负载端的芯片均为FBGA封装,管脚位置在芯片的底部。传输线仿真选用DDR3接口的数据线,采用数据线进行仿真所获得的解决方案具有很高的可复用性。其中源端的模型参数具体为Model_263--3-STATE,1.5V,ODT off,slowest,0.67*RExt,IND,10%,SR11_12MA_10PER_1P5,即三态输出,SSTL-15电平标准,关闭ODT,速度调最慢方便观察实验现象,选择0.67*RExt使得源端输出电流可达到12mA,提高驱动端驱动能力,其中RExt为49.9ohm。

图1:AM335X系统框图

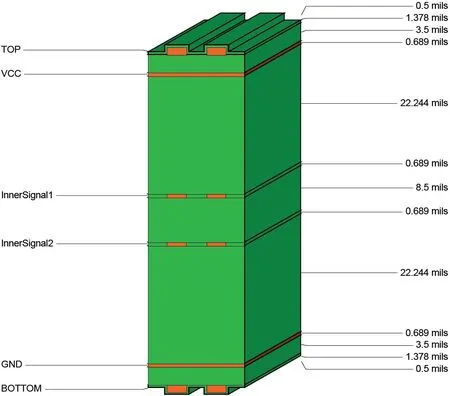

系统包括一片DDR3,电平标准为SSTL-15,主控芯片选用AM335X系列。出于成本考虑,印制电路板的电路板基材采用常用的FR-4,其介电常数为4.05,印制电路板叠层为6层电路板,厚度为1.6mm,内层铜厚0.5oz,外层铜厚1oz,传输线采用的信号线为单端50Ω阻抗匹配的微带线,根据阻抗计算线宽为5.78mil。印制电路板的叠层结构示意图如图2所示。

图2:印制电路板叠层结构示意图

3.2 仿真

由于系统信号量大,对所有信号都进行仿真耗时长,且不现实,因此实验只能对系统中的关键信号进行仿真,然后映射到其他信号上。系统中的关键信号由信号上升时间、工作频率和布线长度等来决定。由此可见,高速信号主要分布在SDRAM DDR3等接口上,特别是时钟网络中的信号,对其他信号既是敏感的受害者,也是攻击者。本文对信号完整性分析中的串扰和反射进行了Line Sim分析。通过反射仿真可以为高速信号选择更合适的终端阻抗匹配电阻阻值,而串扰仿真可以对实际布线进行约束,以尽量减小信号完整性问题。

3.2.1 反射仿真

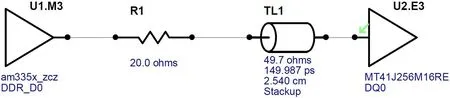

由于该数据线在初始设计时没有终端电阻,仿真时信号过冲、振荡现象比较严重。一般情况下,超调幅度一般应限制在5%以内,否则线噪声和信号反射会造成数据误差或时序紊乱。选取单端数据线DDR_D0作为仿真对象,使用串联电阻实现阻抗匹配的方法,添加串联电阻R1。如图3所示建立反射仿真模型,U1.M3为驱动源,R1为匹配电阻,TL1为特征阻抗50ohm的传输线,U2.E3为接收源,在U2.E3观察反射波形。

图3:反射仿真模型图

激励波形频率设置为100Mhz,传输线线长为1inch。参数扫描设置串联端接电阻R1从0ohm到25ohm,步长

5ohm。

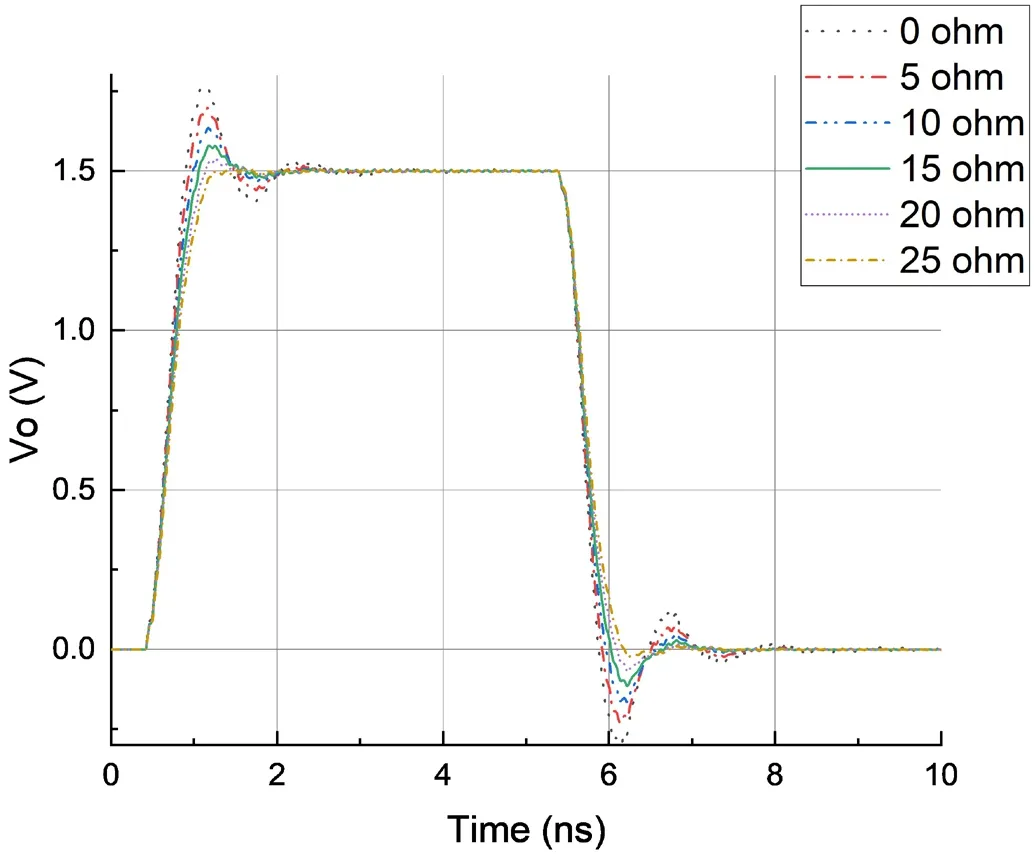

经过良好的串联电阻匹配后超调和振荡现象有较大程度的改善。图4为负载端反射仿真的波形图,在串联端接匹配0ohm到25ohm范围,随着匹配电阻R1由0ohm(无端接匹配)越接近25ohm(良好端接匹配),高速信号受反射影响越小,出现的振铃、过冲现象越少,上升时间越长,其中无端接匹配超调幅度已经超过16%,而25ohm的端接信号超调低于1%。结合实际阻值考虑,最终确定串联匹配电阻为22ohm。为了达到好的匹配效果,串联端接匹配电阻需靠近驱动端,驱动端输出到串联电阻这一段的传输路径最好较短,短到可以忽略这一段传输线的影响,因此在此处布线的过程中也应该注意串联端接匹配电阻的位置。

图4:负载端反射仿真波形图

3.2.2 串扰仿真

串扰受传输线的互容与互感决定,因此其受传输线耦合长度、传输线耦合间距、信号上升时间、介电层厚度、介质层介电常数等因素影响。但由于受传输线耦合长度和传输线耦合间距影响较大,所以着重分析传输线耦合长度和传输线耦合间距对高速信号串扰现象的影响。

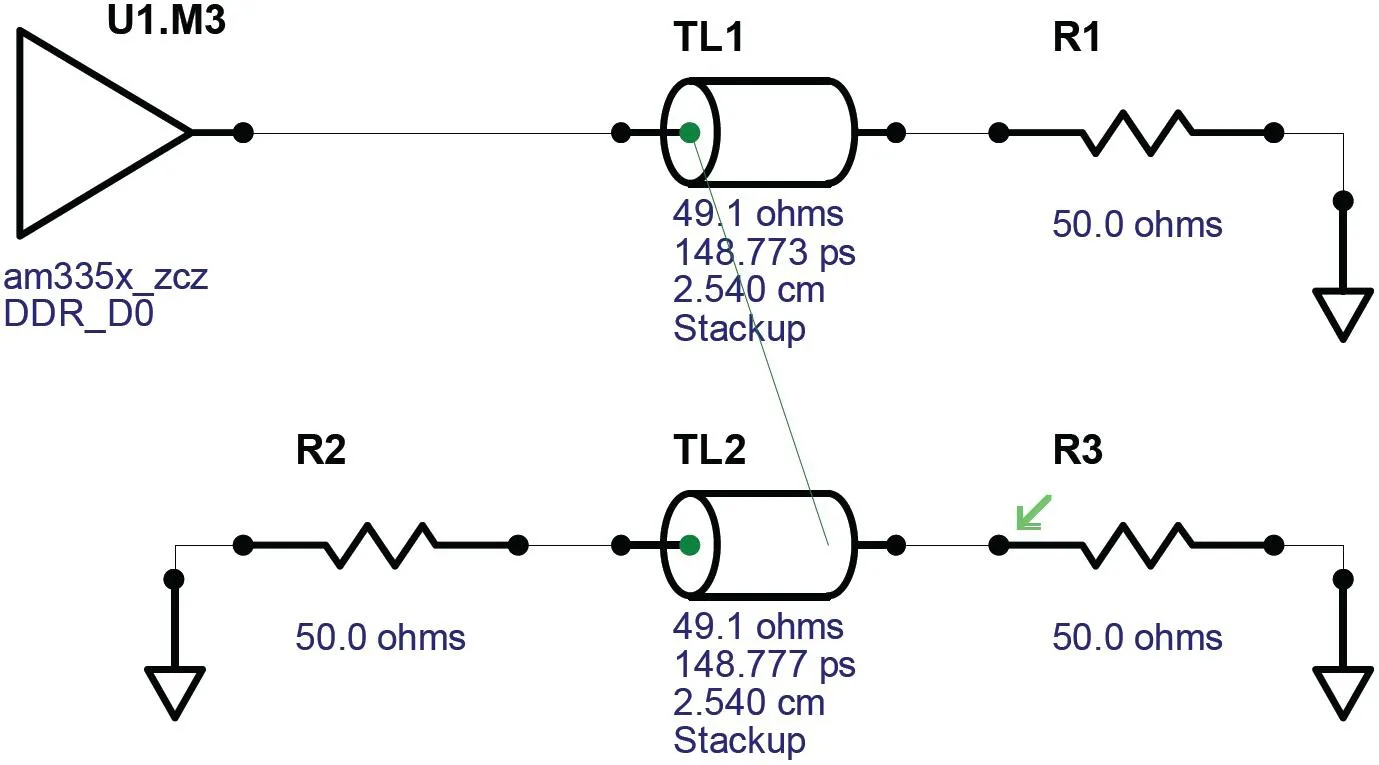

首先对高速信号的串扰进行建模。选取数据线DDR_D0、DDR_D1为实验对象,对DDR_D1进行串扰仿真。将DDR_D0设置为攻击线,DDR_D1设置为被攻击线,由于只考虑攻击线所产生的串扰影响,而对被攻击线本身的信号不做过多关注,攻击线是有源的,被攻击线建模是无源的传输线。建立的电路仿真模型如图5所示:U1.M3为驱动源,R1为匹配电阻,TL1与TL2为特征阻抗50ohm的两耦合传输线,R2为被攻击线上靠近驱动源的电阻,R3为被攻击线上远离驱动源的电阻,在R2观察近端串扰波形,在R3观察远端串扰波形。

图5:串扰仿真模型图

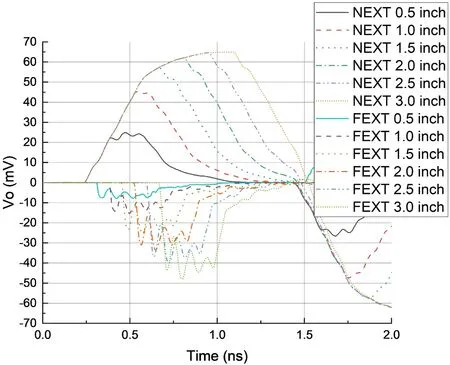

分析传输线耦合长度对高速信号串扰现象的影响。此时双线耦合间距固定为5mil,激励波形频率设置为400Mhz。参数扫描设置为两传输线的耦合长度从0.5inch到3inch,步长0.5inch。实验结果如图6所示,近端串扰波形是正向的干扰,图中由峰值低到峰值高的波形对应传输线耦合长度0.5inch到3inch情况下的,而远端串扰波形为负向的干扰,图由峰值低到峰值高的波形对应传输线耦合长度0.5inch到3inch情况下的远端串扰波形。在上述实验条件下,传输线耦合长度从0.5inch到3inch所对应的近端串扰峰值在20mV到70mV之间,所对应的远端串扰峰值在-10mV到-50mV之间。

图6:不同传输线耦合长度下的近端串扰与远端串扰仿真波形图

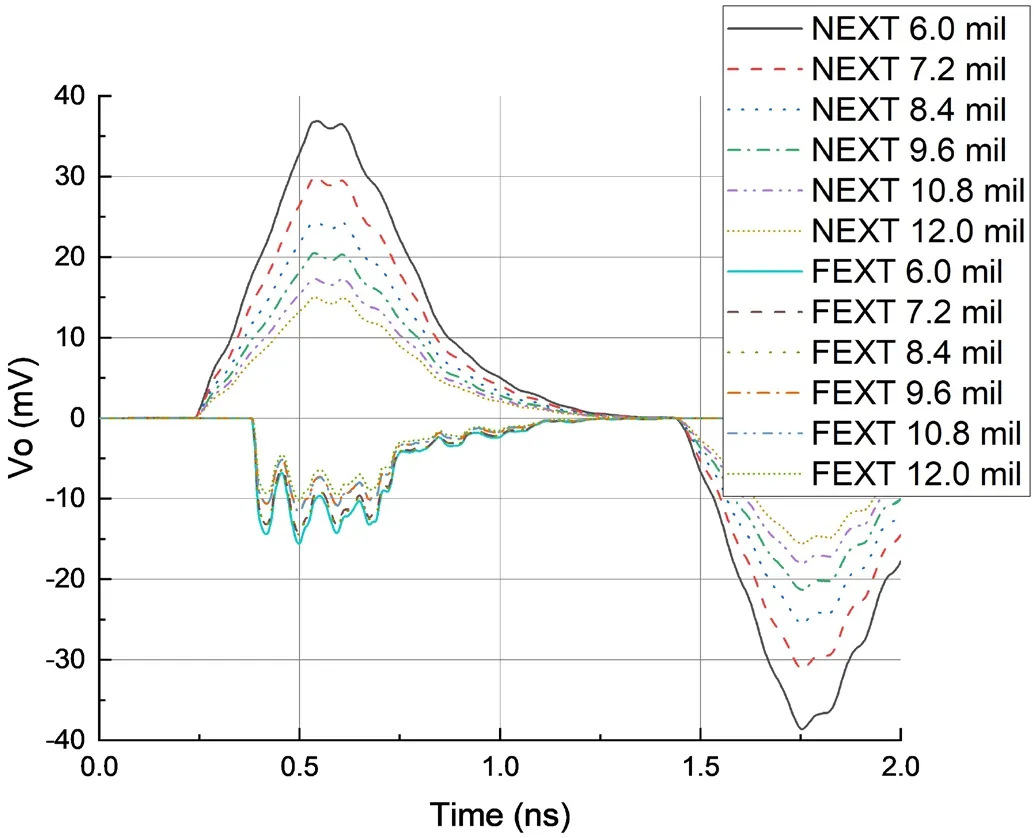

分析传输线耦合间距对高速信号串扰现象的影响。耦合长度固定为1inch,激励波形频率设置为400Mhz。参数扫描设置为两传输线的耦合间距从6mil到12mil,步长1.2mil。实验结果如图7所示,近端串扰波形是正向的干扰,图中由峰值高到峰值低的波形对应传输线耦合间距6mil到12mil情况下的近端串扰波形,而远端串扰波形为负向的干扰,图由峰值高到峰值低的波形对应传输线耦合间距6mil到12mil情况下的远端串扰波形。在上述实验条件下,传输线耦合间距从6mil到12mil所对应的近端串扰峰值在15mV到36mV之间,所对应的远端串扰峰值在-10mV到-15mV之间。

图7:不同传输线耦合间距下的近端串扰与远端串扰仿真波形图

由以上实验结果可以发现,近端串扰峰值和远端串扰峰值与耦合长度呈正相关关系,而与耦合间距呈负相关关系。传输线耦合长度越长,根据传输线理论,其互感越大,导致高速信号线产生的近端串扰和远端串扰越大;传输线耦合间距越大,根据传输线理论,其互容越小,导致高速信号线产生的近端串扰和远端串扰越小,实验结果与传输线理论一致。

同时分析板材(介质层)介电常数对高速信号串扰现象的影响时,参数扫描设置介电层介电常数从2.55到4.05,步长0.3,发现介质层介电常数越小,高速信号线产生的近端串扰和远端串扰越小,但其影响没有耦合长度以及耦合间距明显,不是影响高速信号线产生串扰现象的主要因素。

因此在印制电路板布线过程中,应尽量增大高速信号线之间的布线间距,减小平行布线的长度,同时在成本条件允许的情况下,应尽量选择低介电常数的板材。

4 结论

本文主要针对高速印制电路板中的反射和串扰等信号完整性问题进行研究讨论,基于AM335X处理器,利用Hyperlynx建立了相应的传输线模型进行了反射和串扰仿真分析,通过参数扫描的方法得到理想的参数使信号质量得到明显改善,实验结果表明,仿真分析对高速印制电路板的设计和优化具有一定的指导作用,确保了设计的可预测性和稳定性。