Flash 型FPGA 配置方法研究

2022-05-30庞立鹏蔺旭辉马金龙沈丹丹王晓玲赵桂林

庞立鹏,蔺旭辉,马金龙,曹 靓,沈丹丹,王晓玲,赵桂林

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

现场可编程门阵列(Field Programmable Gate Array,FPGA)芯片具有集成度高、灵活性强、开发成本低、开发周期短等优势,已经成为数字系统应用开发者的必备选择。根据FPGA 内部配置单元进行区分,有SRAM 型、反熔丝型和Flash 型,各类FPGA 都有其优缺点。SRAM 型FPGA 是各大厂商生产的主流FPGA,其配置单元是SRAM 单元,当前规模已突破亿万门级,且随着先进工艺和设计技术的不断突破,其集成规模和应用场景一直在扩大,但其掉电后配置信息丢失,需要配备外部存储器来存储配置数据。反熔丝型FPGA 的配置单元是反熔丝单元,是一次可编程器件(OTP),即当反熔丝单元被高压编程后,形成的稳定导电细丝将内部各种逻辑资源进行连接,具有高可靠性,适用于航天等抗辐射复杂环境[1],但对应用开发者而言成本很高。而Flash 型FPGA 解决了SRAM 型和反熔丝型FPGA 的不足,同时满足非易失性和高可靠性等特点,通过单粒子加固试验和电离总剂量验证,满足空间抗单粒子要求[2-4],已应用于航天航空工程和车载电子等诸多领域,且随着对新型非易失存储器件工艺的不断研究,其规模和性能都越来越优越。

Flash 型FPGA 内部的核心可配置单元为非易失性Flash 单元,基于Flash 架构的FPGA 可实现多次擦除、编程和校验。Flash 单元的特性决定了Flash 型FPGA 的重要特性,即掉电非易失性,当FPGA 完成编程后,配置数据就成为其结构的一个固有部分,系统上电时不需要外部的配置存储芯片加载配置数据,具有上电启动速度快、保密安全性高和低功耗等优势,目前市场上的Flash 型FPGA 供应厂商有Microsemi公司(原ACTEL)公司[5],国内相关单位尚处于研究状态。本文通过对Flash 型FPGA 配置架构和Flash 单元特性的研究,设计了应用于30 万门Flash 型FPGA 的配置电路,并且对整体配置模块和整体电路功能进行了仿真和分析。

2 可配置单元模块设计

FPGA 器件内部的核心模块是可配置逻辑单元模块,对FPGA 编程的过程就是通过配置电路对可配置逻辑模块进行配置,实现各种逻辑功能。Flash 型FPGA 内核可配置的单元模块包括Flash 单元阵列和可配置逻辑模块Tile 阵列。

2.1 整体可配置架构设计

Flash 型FPGA 配置电路由JTAG 控制电路、各功能模块控制电路、多组计数器电路模块、模拟编程高压产生电路、字线译码电路、位线译码电路,上电启动电路等模块构成。JTAG 控制电路包括了TAP 状态机、指令寄存器、指令译码电路、数据寄存器控制电路、多组计数器模块等[6]。图1 是一款30 万门Flash 型FPGA 整体配置架构图,配置控制模块由模拟电路和数字电路两大部分组成。模拟电路包括电启动电路、带隙基准、偏置电路和高低压产生电路等模块,作用是给Flash 单元在编程、擦除和校验阶段提供不同的电源电压和偏置电压。

图1 Flash 型FPGA 整体配置架构图

2.2 JTAG 控制电路设计

Flash 型FPGA 电路中的JTAG 接口电路兼容IEEE 1149.1 标准。用户可以通过JTAG 接口对FPGA中的Flash 单元进行编程,实现配置码流加载。另外可以借助JTAG 接口进行芯片内部信号抓取,方便程序分析,辅助应用开发。JTAG 电路边界扫描测试需要的管脚及功能描述如表1 所示[7]。

表1 对比边界扫描I/O 管脚功能

JTAG 接口电路主要作用是配置控制电路,通过指令寄存器和多条数据寄存器来传输数据,实现擦除、编程、校验和测试的功能。30 万门Flash 型FPGA指令寄存器为8 位寄存器IR<0:7>,设计指令集来控制电路各工作模式。多组不同长度的数据寄存器DR可以实现USERCODE、IDCODE、字线通道选择、字线选择、位线通道选择、位线选择、校验、多种计数器控制、BSR 等数据链功能。整体配置架构如图1 所示,可通过输入不同的指令来选择对应的寄存器链功能。

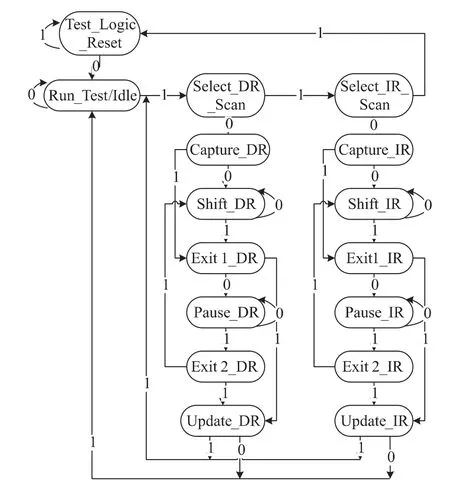

JTAG 控制电路核心模块TAP 控制器是一个16种状态的状态机,TAP 状态机流程图如图2 所示,4 个TAP 引脚控制数据如何被扫描进各寄存器。在TCK上升沿采样到的TMS 值决定了状态机的翻转。TAP状态机在工作中有2 个主要顺序,一个是把指令移入到指令寄存器中,另一个是把数据移入到数据寄存器中。

图2 TAP 状态机流程图

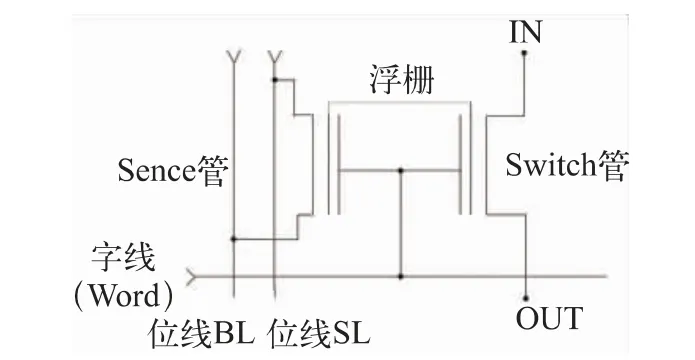

2.3 Flash 单元设计

Flash 型FPGA 最基本的可编程配置单元是Flash单元[8],它具有占用硅片面积小、低阻抗和非易失等特点。Flash 单元原理如图3 所示,Flash 单元由一对共浮栅的Sense-Switch 结构的Flash 晶体管构成,一个是Sense 编程管,负责电路的擦除、编程、校验等操作,一个是Switch 开关管,负责配置FPGA 器件内部连线的开断。编程管和开关管共享浮栅结构,通过控制编程管的栅(Word 字线)、位线(BL)和源端(SL)的电压,向浮栅注入电荷或者抽取电荷,即通过充放电来决定器件状态进而控制开关管的导通和截止状态[9]。当选中的Flash 被编程后,Switch 开关管开启后源漏两端IN-OUT 导通,FPGA 内部电路可以相互连接,实现各种逻辑功能。

图3 Flash 单元原理

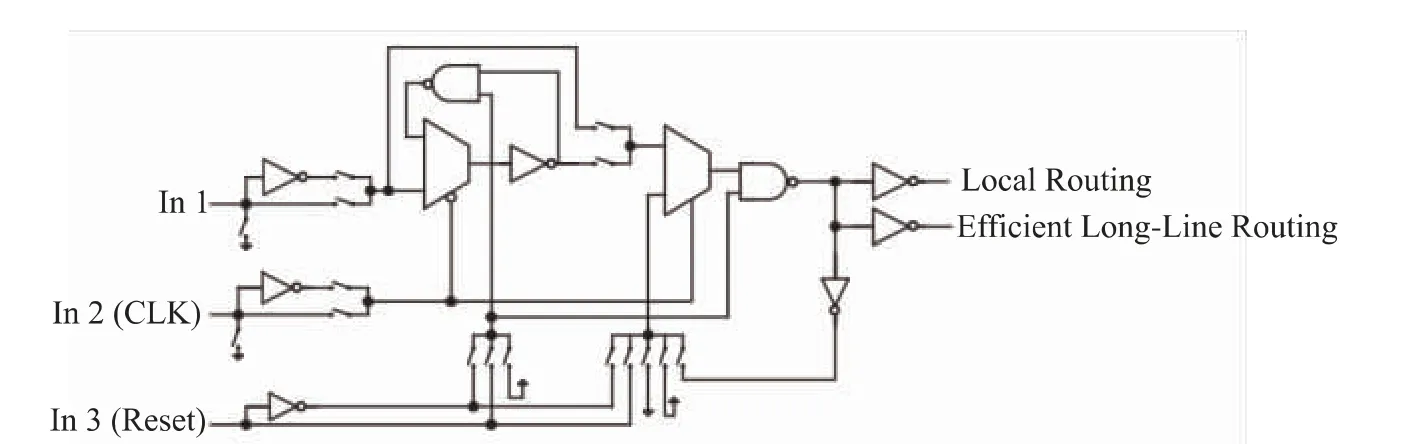

2.4 可配置逻辑模块设计

Flash 型FPGA 内核可配置模块由Flash 单元存储阵列和可配置逻辑单元构成。图4 为Flash 型FPGA内核可编程逻辑单元Tile(片),通过编程特定位置的Flash 单元,可以配置成组合逻辑和时序逻辑电路。可以被配置成可配置逻辑资源Tile 中包含3 个输入信号(每一个输入也可以通过编程路径上的Flash 单元配置成反向输入)和2 个输出信号,除了3 输入的XOR 功能,Tile 电路可以通过编程特定位置的Flash开关,配置实现任意3 输入1 输出组合逻辑功能。可配置单元Tile 也可以配置实现时序逻辑功能,即一个带有清零或者置位的锁存器或触发器功能,此时In1 为输入信号,In2(CLK)为时钟信号,In3(Reset)为清零或置位信号。Tile 单元有2 个输出,其中一个为OUT_LOCAL,其直接到相邻Tile 单元中,当配置信号跨Spine 使用时,OUT_LONG 可以用于长线的布线通道。FPGA 通过相应的开发软件,通过配置码流来配置内核Tile 等资源,可实现整体逻辑功能。

图4 内核可配置单元Tile

2.5 字线控制模块设计

字线控制模块主要是给Flash 配置单元字线Word 提供相应的电压,包括字线译码电路、高压控制电路、移位寄存器链、串并转换电路和高低压电平转换电路等功能模块。在配置过程中,通过8 位指令寄存器IR<0:7>输入对应的指令集组合和多种数据寄存器DR 来操作字线控制模块工作。30 万门Flash 型FPGA 电路中有89 块水平字线通道,对应有89 位字线通道移位寄存器链及对应的串并转换电路,每一块字线通道中有32 根字线,对应有32 位字线选择移位寄存器链及对应的串并转换电路。

2.6 位线控制模块设计

位线控制模块主要是给Flash 配置单元位线BL端和位线SL 端提供相应电压,包括位线译码电路、高压控制电路、移位寄存器链、串并转换电路和高低压电平转换电路等功能模块。在配置过程中,通过8 位指令寄存器IR<0:7>输入对应的指令集组合和多种数据寄存器DR 来操作位线控制模块工作。30 万门Flash型FPGA 电路中有10 块竖直位线通道,对应有10 块位线通道选择控制寄存器链及串并转换电路。每一块位线通道中包括83 位配置数据,对应有83 位配置数据寄存器链以及对应的串并转换电路。

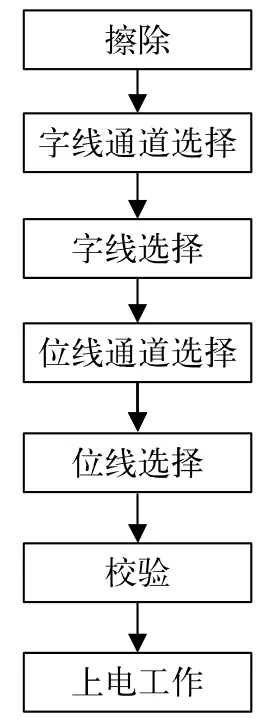

2.7 配置过程

FPGA 在配置过程中,通过JTAG 控制模块和相关指令配置字线和位线相关电路,电源模块通过字线和位线寻址到特定位置的Flash 单元,然后施加特定编程电压进行编程操作[10],Flash 型FPGA 大概的配置流程如图5 所示。

图5 Flash 型FPGA 配置流程

1)擦除:Flash 型FPGA 擦除过程中采用全片擦除模式,通过相应的指令集、字线和位线控制电路,使能擦除相关电路模块,各计数器开始工作,产生擦除阶段所需要的各种电压。在擦除命令控制下,电路中所有的字线和位线被选择,将电路中所有的Flash 单元配置存储信息全部擦除掉。

2)字线(WL)寻址:Flash 型FPGA 在配置过程中对具体的某根字线寻址时,先选择这根字线所在的字线通道,然后再选择字线通道中的字线。所有的字线通道和字线会被逐行遍历到,具体某根字线是否被选中则通过指令集来控制,当被选中时,才能对该字线上相应的Flash 单元进行编程配置,当字线不选中时,直接跳到下一根字线地址进行操作。通过输入字线通道选择指令,对89 位字线通道寄存器链写入1 位“1”,该位数据“1”通过89 位寄存器链一直移位下去,确保当前阶段只选中一块水平字线通道,后期通过字线通道移位指令将每一块字线通道遍历到,直到89 块字线通道被全部遍历完。字线选择过程和字线通道选择机理一样,先选中某块字线通道后,再通过输入字线选择指令,对32 位字线移位寄存器链写入1 位数据“1”,确保当前阶段只选择一根字线来操作,1 位数据“1”通过移位寄存器一直移位下去,直到32 位字线被全部遍历到。

3)位线(BL)配置数据写入:Flash 型FPGA 在编程配置数据写入过程中,在位线数据清零指令、位线通道选择指令,配置数据写入等指令集操作下,先选择具体的某块位线通道,再给83 位移位寄存器链中写入编程配置Bit 码流,通过串并转换电路,最终确定选中某位线BL,输入的每一帧配置码流定义了一根字线(Word)地址线上需要编程的Flash 单元信息。

4)编程:当寻址到字线Word 和位线配置数据写入后,通过对应的指令集来控制电路中的各种计数器模块,控制高低压编程时间,对寻址到的Flash 单元依次进行编程,将配置信息写入到Flash 单元中。

5)校验:当电路中所需位置的Flash 单元被编程完成后,需要对编程后的Flash 单元进行对比校验,判断Flash 编程的位置、数量、阈值电压等是否满足设计和工艺要求,当以上所有步骤没问题时,电路可以上电,实现所配置的整体功能,开启正常工作状态。

3 仿真结果与分析

通过对设计的30 万门Flash 型FPGA 电路搭建整体数字仿真环境, 使用Candence 自带的NC_Verilog 仿真工具进行仿真验证,对其配置过程以及整体配置后的电路功能进行仿真验证。

3.1 配置过程仿真

Flash 型FPGA 在编程配置操作阶段,通过JTAG控制模块将与编程相关的模块连接起来,通过专有指令控制编程时序和逻辑功能,从而实现对Flash 单元的编程。首先配置各计数器状态,接着在相关指令控制下,电路中字线被一根根逐步遍历到。选择一个字线通道,再次将字线通道中的每一根字选择到,Flash单元在编程阶段字线状态是低电平“0”,该状态下表明该条字线被寻址到。

同样的道理,当字线被寻址到后,该字线上所连接的位线数据也会被加载上去,在相关指令下,通过TDI 往83 位位线寄存器链中写入位线配置数据,首先写入位线通道选择指令84,每次只能打开一个位线通道,在位线寄存器控制指令E5 下,再写入一拍编程配置码流数据。在此过程中,最多可以打开10 个位线通道BL_BANK<0:9>,相应的灌入同等节拍的位线Bit数据。图6 截选了部分编程阶段Flash 单元位线仿真波形。在编程时间等待指令下,被选择到的Flash 单元电路处于被编程状态,当Flash 单元完成编程后,Switch 开关管打开工作,起到电路连接的作用。

图6 位线仿真波形

3.2 整体功能仿真

将Flash 型FPGA 通过相应的FPGA 开发软件配置成多种功能,加载配置信息码流激励到整体FPGA芯片逻辑网表中,进行电路TOP 层数字化功能仿真验证,通过寻址到对应的Flash 单元,将配置信息编程到Flash 单元,实现整个功能的配置。

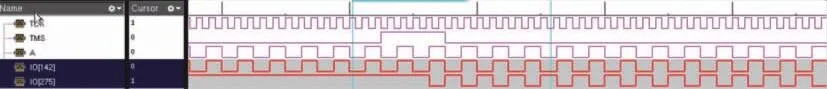

整体功能案例1,配置了1 个输入反相器功能,反相器输入端口为IO<142>,输出端口为IO<275>,反相器功能整体仿真波形如图7 所示,仿真结果显示配置后的反相器功能正常。

图7 反相器功能整体仿真波形

整体功能案例2,配置了4 类功能,有组合逻辑也有时序逻辑,整体电路内核逻辑资源利用率为99%,基本用遍了内核Tile 可配置逻辑资源,整体数字仿真功能都正常,多种配置功能整体仿真波形如图8 所示。

图8 多种配置功能整体仿真波形

功能1:3 输入与门AND3,输入端口为IO<79>、IO<81>、IO<82>,输出端口为IO<143>;

功能2:3 输入或门OR3,输入端口为IO<83>、IO<84>、IO<85>,输出端口为IO<145>;

功能3:2 输入异或门XOR2,输入端口为IO<86>、IO<87>,输出端口为IO<148>;

功能4:4 条2000 级的移位寄存器链,输入端口为IO<6>、IO<28>、IO<255>、IO<253>,4 条链各自对应 的 输 出 端 口 为 IO<280>、IO<118>、IO<123>、IO<198>。

4 结论

基于系统门数为30 万门的Flash 型FPGA 电路,本文从最基础、关键的Flash 配置单元特性开始到整体电路的配置方法和机理、配置电路架构进行研究,研究了Flash 型FPGA 的配置方法、指令集设计、寄存器设计、计数器设计等。经过整体电路配置功能仿真验证,结果表明基于以上配置架构设计的配置电路满足该30 万门Flash 型FPGA 的配置要求。在研究过程中初步掌握了Flash 型FPGA 配置电路整体架构、配置方法和机理,后续可以将研究成果引用到系统门数规模更大的Flash 型FPGA 中进行整体配置仿真验证,更加深层次地验证Flash 型FPGA 配置电路设计合理性,并进行后续设计优化。