基于后端流程的层次化物理设计方法的研究

2022-05-30王洁茹宋庆文

王洁茹,宋庆文

(西安电子科技大学,陕西西安,710000)

0 引言

随着晶体管和集成电路的发明,人们在半导体领域的发明层出不穷,同时也推动了半导体分立器件产业和集成电路产业,以及集成电路产业所应用的各种领域,如航天军事、互联网、移动通信、消费类电子等的迅速发展。集成电路产业的高速发展,对于集成电路产业从业者而言,也面临着一些新的挑战。新兴市场对电子产品的需求越来越多,对电子产品所具备功能的期望也越来越高。这也对集成电路产业提出了新的要求,即如何设计出具备更多功能的高性能芯片。尤其是进入到后摩尔时代,考虑到市场的经济效益,芯片越晚交付,所需要的经济成本就越高,创造的经济效益就越少。因此,这也对芯片设计过程的周期提出了要求。芯片设计可以分为前端设计和后端设计,后端设计在流片之前,因此后端设计的质量好坏、设计周期对于整个工程的是否能按时完成交付,将芯片送往代工厂进行流片都是非常重要的。

本文主要基于一款芯片的前端数据,利用Cadence公司的后端物理设计工具Innovus,用基于flex model模拟模型的层次化物理设计方法对对芯片进行物理设计。并以传统的展平式设计方法作为对比,说明了层次化物理设计方法不仅可以保证时序收敛,且在设计总耗时上与展平式设计方法相比更有优势。

1 展平式和层次化方法的简介

1.1 展平式设计方法的介绍

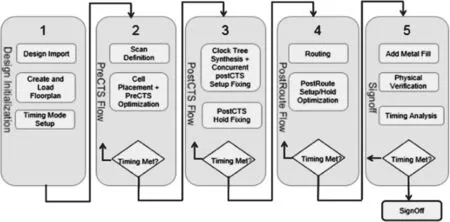

展平式设计方法是一种比较简单的物理设计方法,一般400万门以下的设计都可以用该方法进行实现。具体的展平式设计流程图如图1所示,主要包括以下几个步骤:

图1 展平式物理设计流程图

(1) 数据准备

(2) 布图规划

(3) 布局及布局后优化

(4) 时钟树综合及时钟树综合后优化

(5) 布线及布线后优化

(6) 工程变更

(7) 形式验证

(8) 物理验证

(9) 流片

1.2 层次化设计方法的介绍

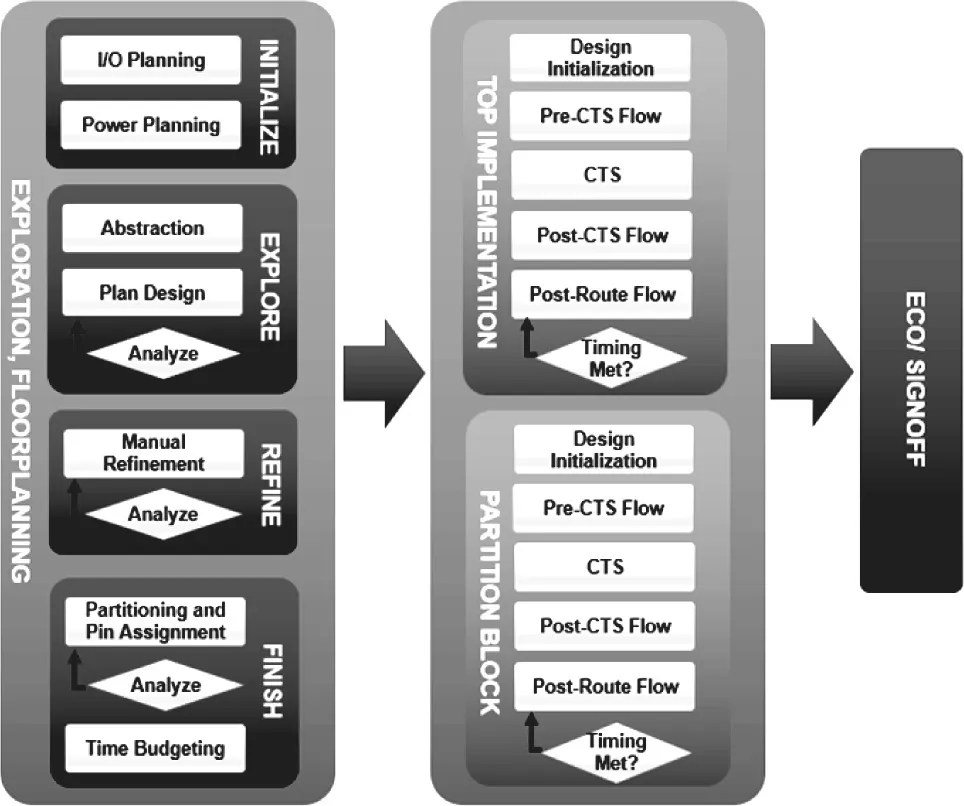

层次化设计方法与展平式设计相比,更适用于规模比较大的芯片。它最大的特点就是首先要对芯片进行整体分析规划,这是为了对芯片进行分割。主要思路是将一个大的设计分成若干个子分割块,每个分割块在完成各自的物理设计时是相互独立的,可以交由不同的设计团队进行物理设计,在时间周期上也是可以并行进行的。但是层次化物理设计中,每一个模块与其他相关大模块和顶层之间的时序约束需要各自独立实现收敛,如果某些模块不能收敛,它会要求在顶层重新做约束分配,直到实现模块和顶层都收敛的结果。具体的层次化设计流程图如图2所示,主要包括以下几个步骤:

图2 层次化物理设计流程图

(1) 整体布图规划

(2) 子模块的指定

(3) 快速布局布线

(4) Partition的接口分配和时序分配

(5) 芯片分割

(6) 子模块和顶层的物理设计

(7) 顶层整合

2 层次化物理设计方法的物理具体实现过程及结果

首先我们需要把数据文件正确读入,才能顺利进行接下来的步骤。在把网表文件、库文件、各种约束文件读入之后,就可以进入芯片规划阶段了。首先我基于该芯片的层次结构对其进行分析:该芯片有379777个子单元,其中包括6个大的模块。在分析该设计结构时,我观察到,对于这6个模块而言,其中有3个模块的子单元数量明显多于其他3个模块。比如u_mp11_1模块包含174653个子单元,占到总子单元数的46%;u_mp11_0模块包含172385个子单元,占到总子单元数的45%;u_scu模块包含19800个子单元,占到总子单元数的5%。其他三个模块的子单元数要远远小于这三个模块。并且,对于整个设计中包含的72个硬核模块(block),也是只存在于这三个模块中的。u_mp11_1、u_mp11_1、u_scu这三个模块分别有28、28、16个block。考虑到三个模块的规模较大,并且对于硬核模块而言,会在设计早期就确定其位置,通常也希望不要被划分到其他模块区域,因此我准备把这三个模块指定成三个分割块(partition),在后面的芯片实现阶段分别去进行物理设计。按照合理的流程进行的话,在确定好partition之后,我需要基于整个芯片做一个快速的布局规划和布线,目的是基于布局规划和布线的结果去给partition分配partition之间的接口(partition pin)以及分配时序预算(timing budget)。虽然这里所做的快速布局布线和实际的布局布线不同,它是一种较为粗略的布局布线,由于不会考虑很多约束条件,因此相对而言速度较快。但是这种布局布线法依然需要将整个设计的完整网表读入,并读取所包含的所有单元的信息。对于本课题的中的芯片,或许对于200多万个逻辑门的规模工具有能力处理,只是体现在处理数据的耗时要久一点。可是目前大多数设计的数量级都在数千多万以上,甚至对于超大规模集成电路的设计,规模更为庞大,那么不仅可能会出现耗时严重的情况,甚至会出现工具的内存也无法很好处理的情况。基于这方面的考虑,我计划引入模拟模型(flex model)。

Flex model是一种使用了基于接口逻辑模式的ART技术设计出的模拟模型。Flex model保留了接口逻辑上的器件,将其他非接口逻辑上的器件用flex filler(模拟填充单元)代替。通过这种抽象建模,网表可以缩减到原来的20倍,从而使得Innovus的运行速度提高20倍。并且不会影响到时序、面积、拥塞等方面的分析的准确性。这种准确性也保证了布图规划的准确性,避免了在后端设计过程中的反复迭代、重新布图规划。

下面是我用脚本来创建flex model的具体过程以及创建好的flex model的信息。可以看到,整个设计的规模被缩减到了原来的12.4%,这对于减少后面的快速布局布线阶段的耗时以及工具对于数据的读取都是有利的。

set_proto_mode -create_partition_as_flexmodel true

set_proto_model -model mp11_1 -type flex_module

set_proto_model -model mp11_0 -type flex_module

get_proto_model -all

create_proto_model -out_dir ./DBS/model_gen.enc

在完成芯片的整体规划与模块的分割之后,就可以进行接下来的步骤了。

图3展示了完成芯片组装后整个顶层的版图。图4展示了完成了顶层的物理设计过程后的时序结果。可以看出使用层次化物理设计可以实现序收敛。

图3 完成芯片组装顶层的版图

图4 完成了顶层的物理设计过程后的时序结果

3 层次化与展平式物理设计方法的数据对比与分析

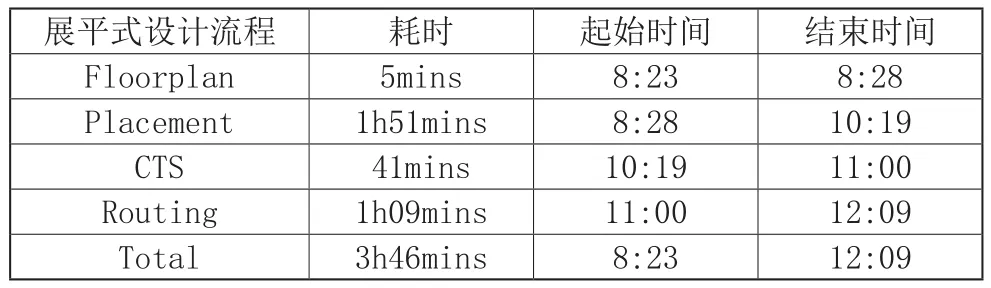

为了更好地体现层次化物理设计在缩短设计周期上的优势,我同样也使用展平式设计方法,基于相同前端数据和Innovus工具对芯片进行物理设计,完成从布图规划到布线及布线后优化的全过程。

表1和表2分别是使用展平式物理设计和层次化物理设计的各个阶段的耗时结果。可以看到:使用展平式物理设计方法的总耗时为3h46mins,使用层次化物理设计的总耗时为3h23mins,和展平式物理设计方法相比取得了10.12%的优势。证明了层次化物理设计在缩短设计耗时上的优势。

表1 使用展平式物理设计的耗时结果

表2 使用层次化物理设计的耗时结果

4 结论

本文首先简单介绍了集成电路的发展和目前集成电路产业的现状以及所面对的挑战,然后结合对芯片的具体的物理实现过程,对基于flex model的层次化物理设计的各个阶段进行了详细的阐述。此外,作为对比,同时采用展平式物理设计方法对芯片进行物理实现。通过对两种物理设计方法设计结果的比较,证明了两种设计方法都能实现最终的时序收敛。在设计总耗时上,使用展平式物理设计方法的总耗时为3h46mins,使用层次化物理设计的总耗时为3h23mins,和展平式物理设计方法相比取得了10.12%的优势。证明了层次化物理设计在缩短设计耗时上的优势。