塑闪阵列探测器读出ASIC 阈值产生与调节电路的设计

2022-05-28敬雅冉蒲天磊赵红赟杨鸣宇孙志坤张家瑞佘乾顺颜俊伟孙志朋王长鑫

敬雅冉,千 奕*,蒲天磊,赵红赟,杨鸣宇,孙志坤,张家瑞,孔 洁,佘乾顺,颜俊伟,孙志朋,王长鑫

(1. 中国科学院近代物理研究所 兰州 730000;2. 中国科学院大学核学院 北京 石景山区 100049)

我国首颗暗物质粒子探测卫星“悟空号”,在电子能谱~0.9 TeV 处测量到了拐折,并在~1.4 TeV处发现了疑似的精细结构迹象,引起了国内外同行的高度关注[1]。然而,受限于探测器的尺寸和结构,“悟空号”的伽马射线探测能力较弱。为了提升伽马射线的探测能力,科学家提出要研制新一代高性能的甚大面积伽马空间望远镜 (very large area gamma-ray space telescope, VLAST)[2]。VLAST 包括4 个子探测器,分别是径迹探测器、量能器、中子探测器和塑料闪烁体阵列探测器(the plastic scintillator array detector, PSD)[3];其中大面积PSD对前端读出电子学提出了多通道、大动态、高计数率的需求;同时由于卫星功耗资源及硬件的限制,还要求前端读出电子学具有紧凑型、低功耗、低噪声及抗辐照等特性。随着半导体探测技术的日趋成熟,高集成度的专用集成电路(application specific integrated circuit, ASIC)芯片技术已被广泛应用于粒子物理与核物理实验的谱仪系统中;在空间探测领域中,这一技术也逐渐成为发展趋势,ASIC 芯片的利用,极大简化了前端电子学的设计,减少了星上功耗开销和硬件支出[4]。因此,需要研制一款多通道ASIC 芯片,用于实现大面积PSD 对核素电荷的处理与测量。

1 ASIC 芯片设计

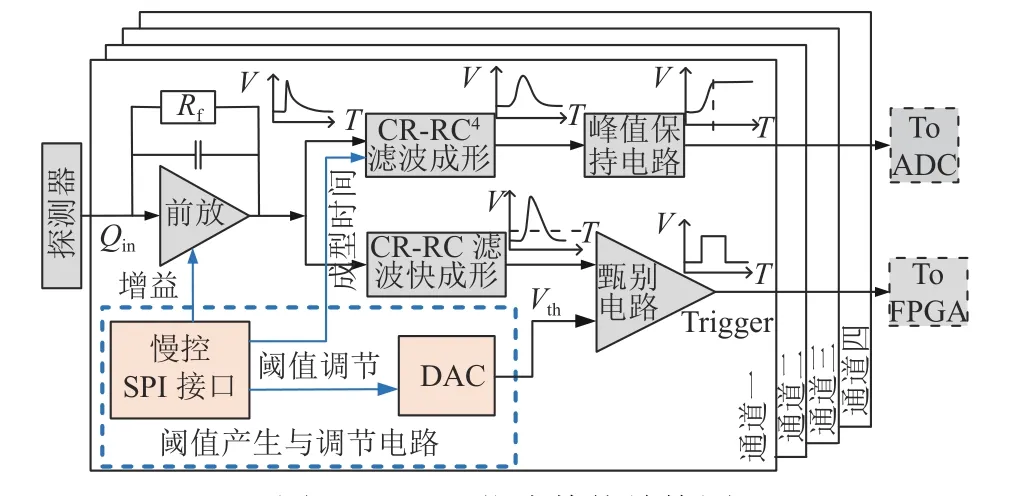

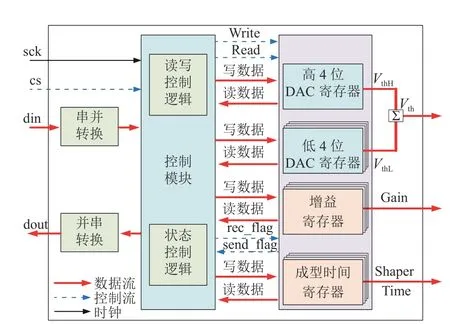

ASIC 芯片的整体结构图如图1 所示,其中每通道包括低噪声前放、CR-RC 滤波成形、峰值保持电路、甄别电路、SPI 慢控接口[5-6],同时该芯片具有自触发模式,每通道输出独立的触发信号,触发阈值由片内数模转换(DAC)模块产生[7]。本文主要设计了ASIC 芯片中阈值产生与调节电路(图1虚框内所示),通过SPI 控制接口,可以为片内的甄别电路提供可调节的触发阈值[6]。在物理实验中,由于不同离子的能量不同,经前放和快成形电路处理后的输出电压也不同,该输出电压进入甄别电路和阈值电压进行比较后输出Trigger 信号。通常,对阈值电压的设置是越低越好,在保证抑制噪声的前提下,让尽可能多的信号过阈。但是,有时为了降低Trigger 率,需要提供较高的阈值电压。本设计中的阈值电压具有较大的调节范围,约15~960 mV,最小调节步进好于4 mV,INL 和DNL 均好于0.2 LSB。

图1 ASIC 芯片整体结构图

2 阈值产生与调节电路的设计

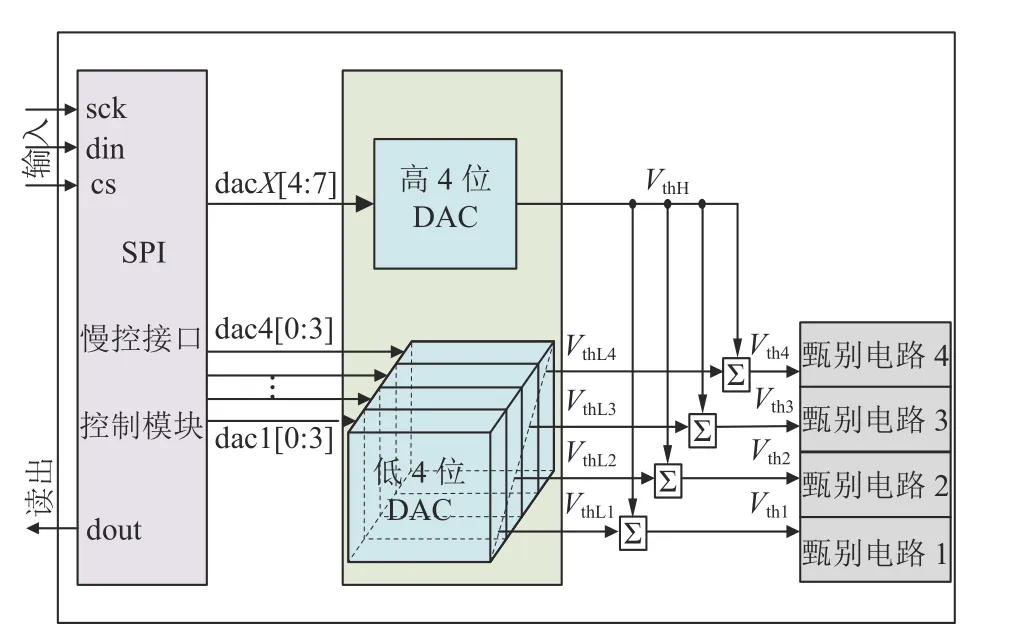

芯片中的触发阈值产生与调节电路利用高4位DAC 与低4 位DAC 结合的方法,实现一个8 位DAC 的阈值调节,其结构如图2 所示。包括DAC 模块和基于SPI 慢控接口的控制模块,外部输入信号通过SPI 慢控接口的din 端口输入,门控信号sck 在使能信号cs 为低时有效,并对相应DAC 寄存器进行读写。通过改变写入寄存器的数据来控制DAC 的输入信号,从而控制DAC 的输出幅值,为甄别电路提供了可调阈值。

图2 阈值产生电路的结构

为了简化芯片内部电路结构,减小版图面积,降低功耗,提出通过组合高、低两个4 位DAC分别进行粗细阈值调节来实现一个8 位DAC 阈值调节的方法。在芯片内所有通道复用一个高4 位DAC,实现阈值的粗调,产生阈值电压VthH,调节范围约为900 mV;每个通道内部包含一个低4 位DAC,实现阈值的细调,产生阈值电压VthL,调节范围约为60 mV;每通道内甄别电路的输入阈值电压Vth=VthH+VthL。通过粗调和细调相结合的方法,实现了大动态范围、高精度的阈值电压调节。

2.1 DAC 模块设计

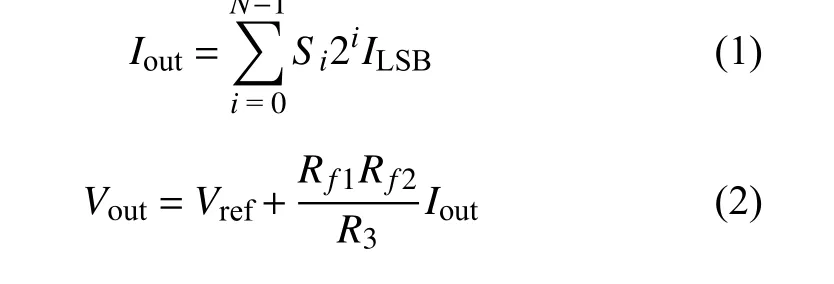

为了在芯片内设计并实现面积小、功耗低、转换速度较快的DAC 模块,对比不同类型DAC 的优缺点[8-10],并对设计要求进行衡量,本文最终选择采用电流按比例缩放型中的二进制加权型电流舵DAC。电流舵DAC 首先利用有源器件MOS 管构成加权电流源,再通过数字输入信号选通相关电流源支路输出;数字输入信号的不同,决定开关阵列电路中每个开关的通断,从而决定每个电流源阵列是否接入电路。随着数字输入信号的变化,流入运算放大器的电流随之变化,其输出端的电压也发生变化,实现数字信号向模拟信号的转变。图3 所示为电流舵DAC 的结构,包括N个二进制电流源:ILSB, 2ILSB, ···, 2(N-1)ILSB,其中,ILSB表示最小权值对应的电流大小。当第i位输入数字信号Si=1 时,受信号Si控制的开关闭合,第i个电流源与运算放大器的输入负端连接,相反,当Si=0时,开关Si断开,对应电流源的输出电流不再流入运算放大器中。所以,流入运算放大器I1 的电流Iout如式(1)所示,DAC 的输出电压Vout如式(2)所示:

图3 二进制加权型电流舵DAC 结构

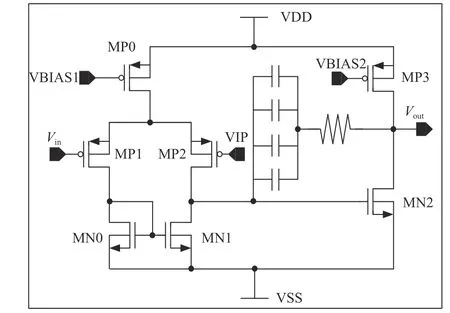

图中,I1 和I2 均为低失调、高增益、低噪声的运算放大器。I1 主要是把加权电流源网络的权电流转化为电压输出,并提高输出的精度。其结构如图4 所示,由两级电路组成。

图4 运算放大器电路结构

第一级为差分放大级,由MP0、MP1、MP2、MN0 和MN1 共5 个晶体管组成,由于PMOS 具有良好的抗辐射能力,MP1 与MP2 差分对使用PMOS 作为输入级,差分对管通过调整栅长与宽长比,能够显著降低失调,由于L的增大,导致单极运算放大器无法满足增益需求。因此,第二级采用了共源级来进一步提高增益,由MP3、MN2 共2 个晶体管组成。I2 为低失调的运算放大器,可对I1 的输出信号进行反向并提高驱动能力。由于DAC 需要驱动较大的容性负载,所以采用大驱动能力的运算放大器能够提高电路的稳定性。

2.2 SPI 慢控接口模块设计

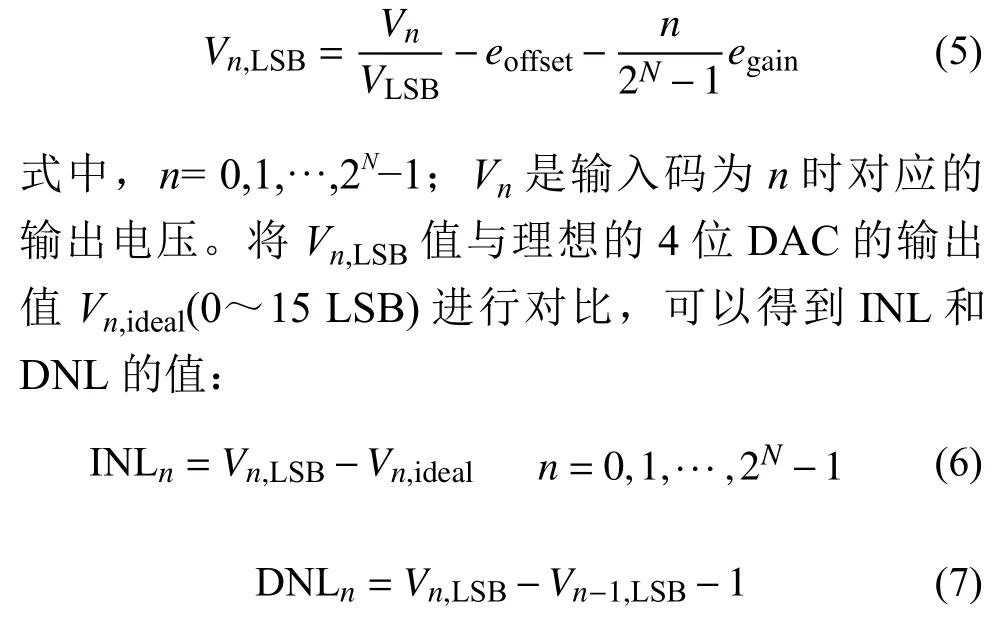

串 行 外 设 接 口 (serial peripheral interface, SPI)是一种高速、同步、全双工的通信总线,连线简单,可以有效节约芯片的输入管脚[11-12]。本文设计的SPI 慢控接口模块的功能包括:控制前放的增益、控制成型时间的档位以及控制DAC 的输入来调节甄别电路的触发阈值。图5 为SPI 慢控接口模块的设计结构框图,数据信号通过数据线din 输入,通过串并转换模块后,进入控制模块。控制模块中的读写控制逻辑对并行数据进行判断,并识别读写控制信号,当控制信号为写信号时,在状态控制逻辑的控制下,进入写数据过程,向各个寄存器中写入数据信号;当控制信号为读信号时,在状态控制逻辑的控制下,进入读数据过程,从相应寄存器中读出并行数据信号,再通过并串转换模块,由dout 数据线输出。外部串行数据在使能信号有效时,通过SPI 慢控接口完成对寄存器的读写,写入寄存器中的数据作为DAC 模块中开关的控制信号。本文中,时钟频率设计为30 MHz,输出可驱动负载电容为6 pF。

图5 SPI 慢控接口结构

3 电路仿真

3.1 DAC 模块仿真结果

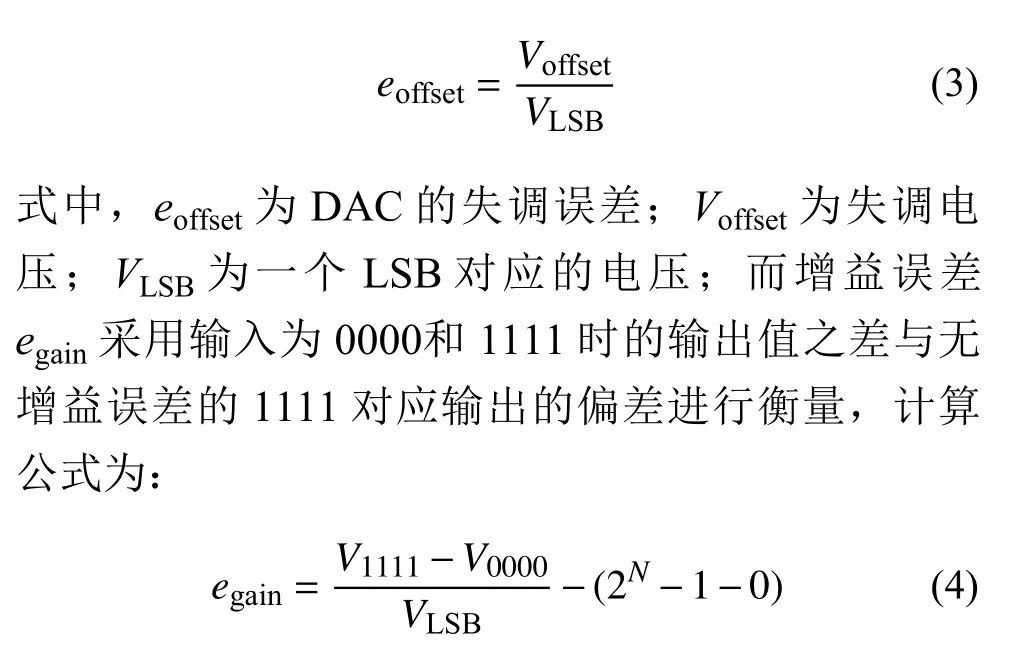

DAC 模块的设计基于3.3 V 电源电压,利用Spectre 软件对阈值粗调的高4 位DAC 和阈值细调的低4 位DAC 进行原理仿真。相比于粗调的DAC,细调DAC 的精度要求更高。常温条件下,对细调的低4 位DAC 进行前仿真和提参后的后仿真,并分别对数据进行处理,计算INL 和DNL 值:

式中,N为DAC 的位数。计算非线性INL 和DNL 时,首先应去除失调误差eoffset和增益误差egain,然后采用LSB 进行归一后,各个输出值Vn,LSB为:

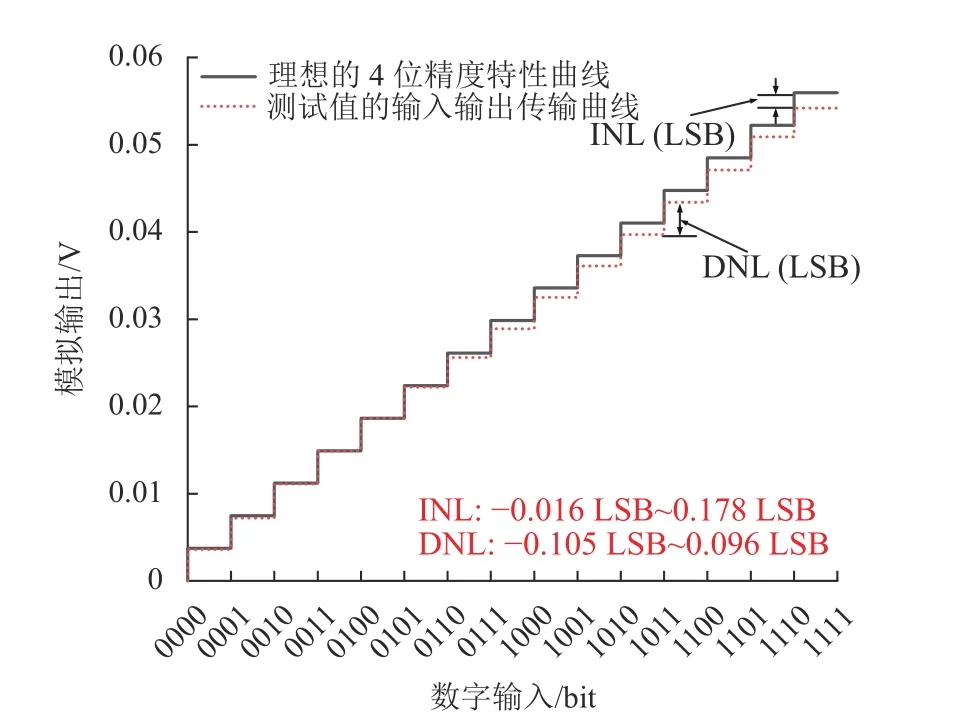

对计算出的数据进行拟合,从而得到DAC 前后仿真的DNL对比图和INL 对比图,如图6 所示。

图6 低4 位DAC 的DNL 和INL 仿真图

从图中可以看出DNL 为−0.016~0.018 LSB,INL 为−0.02~0.011 LSB,线性均小于0.02 LSB,表明设计具有较好的线性。

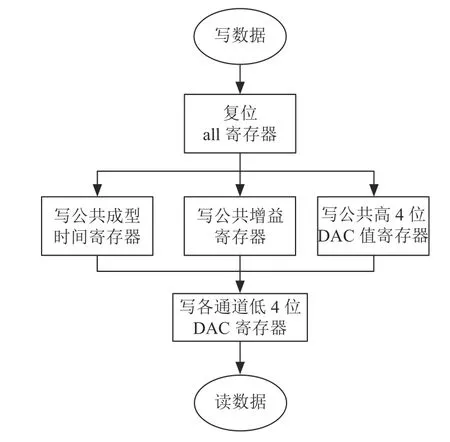

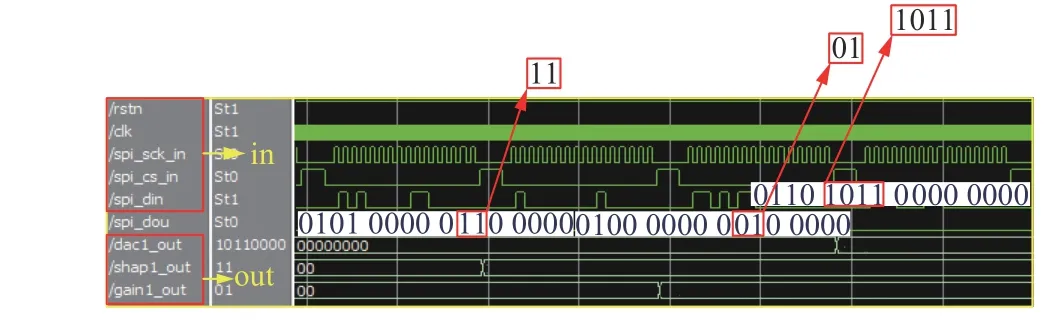

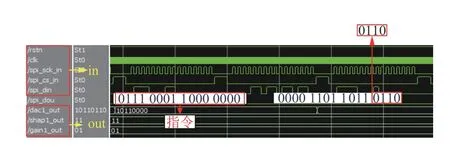

3.2 SPI 慢控接口模块仿真结果

首先利用Modelsim 软件对设计的SPI 接口模块进行RTL 级功能仿真验证。在testbench 文件中,设置基本时钟周期clk 为100 ns,信号时钟周期sck 为1000 ns,整个写数据仿真流程如图7 所示,按照写入复位信号、写入公共成型时间和公共增益信号、写入公共高4 位DAC 值,以及写入各通道低4 位DAC 值依次进行仿真和验证。

图7 写数据仿真流程图

以写数据操作验证为例,写公共部分数据时,高4 位为指令,规定写的寄存器,后面指定位为实际写进寄存器的数据,分别验证了写公共成型时间、写公共增益和写高4 位DAC 数据,仿真图如图8 所示,可以看出相应寄存器中被写入与指令中数据位相同的数据。写各通道低4 位DAC 数据的仿真图如图9 所示,先是16 位的指令,包括指定要写的低4 位DAC 的通道号以及使能位,后是16 位数据位,图中标出来的框图为输入寄存器的数据,同时可以看出低4 位DAC 寄存器中也被写入与框图中一致的数据。即写数据过程满足设计要求。读数据操作验证结果也一致。表明所设计的SPI 慢控接口能够对寄存器进行正确的读写操作。

图8 写公共成型时间、增益及高4 位DAC 数据波形图

图9 写低4 位DAC 数据波形图

功能仿真验证后,利用Synopsys 公司的DC(design compiler)软件,对代码进行综合过程,将RTL 代码映射为与工艺库相关的网表文件;然后利用Cadence 公司的SOC Encounter 软件进行后端的布局布线,对综合产生的门级网表进行布局规划(floor planning)、布局布线(placement& routing),并生成生产用的版图;再对版图进行提参(starrc)、静态时序分析(STA)和形式验证(formality),以便进行后仿真。完成后仿真后,对得到的后仿真结果和前仿真结果进行对比,每个输出信号的延时时间在6 ns 以内,完全符合输出设计要求,也保证了流片结果的可靠性。

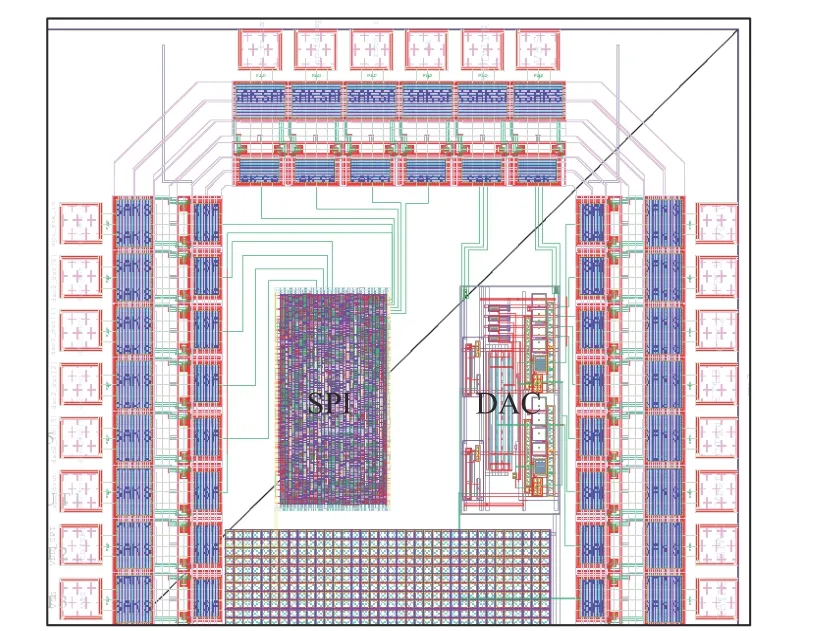

4 版图设计

该芯片采用 global foundries (GF) CMOS 0.18 um工艺,3.3 V 单电源供电。芯片整体版图如图10 所示,尺寸为800 um×1000 um。芯片在foundry 流片后,使用QFN68 进行封装。

图10 整体模块版图

在版图设计过程中,考虑到设计的用途,对版图进行了优化,包括电路中的信号线采用适当的宽度并且走线要尽量短,减小寄生参数;偏置电路的位置要避开电路的敏感器件;在电流源阵列布局时,考虑不同电流源的权重不同,将电流源阵列采用共质心布局来减小失配。

同时,为了防止发生单粒子闩锁,DAC 模块的版图设计时加入了抗辐照考虑,采取以下措施:1)在晶体管周围增加保护环;2)尽量让NMOS 靠近VSS,PMOS 靠近VDD,使NMOS和PMOS 晶体管之间保持足够大的距离;3)在晶体管四周密集排布阱接触孔,减小接触孔与晶体管有源区的距离。

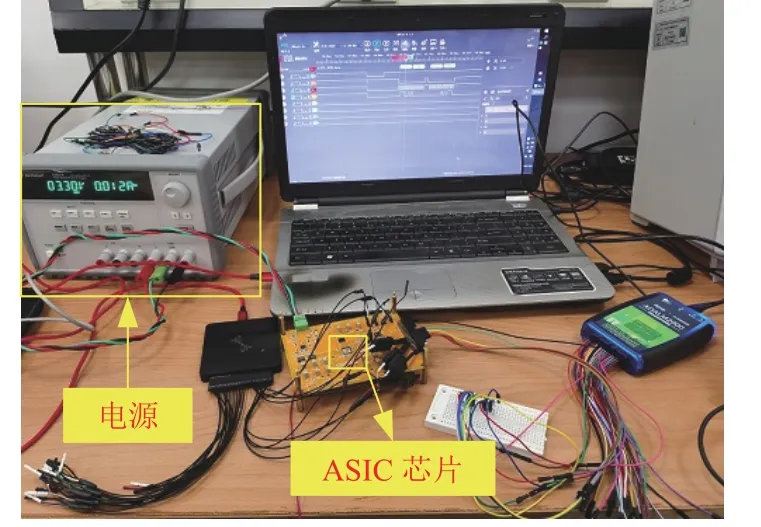

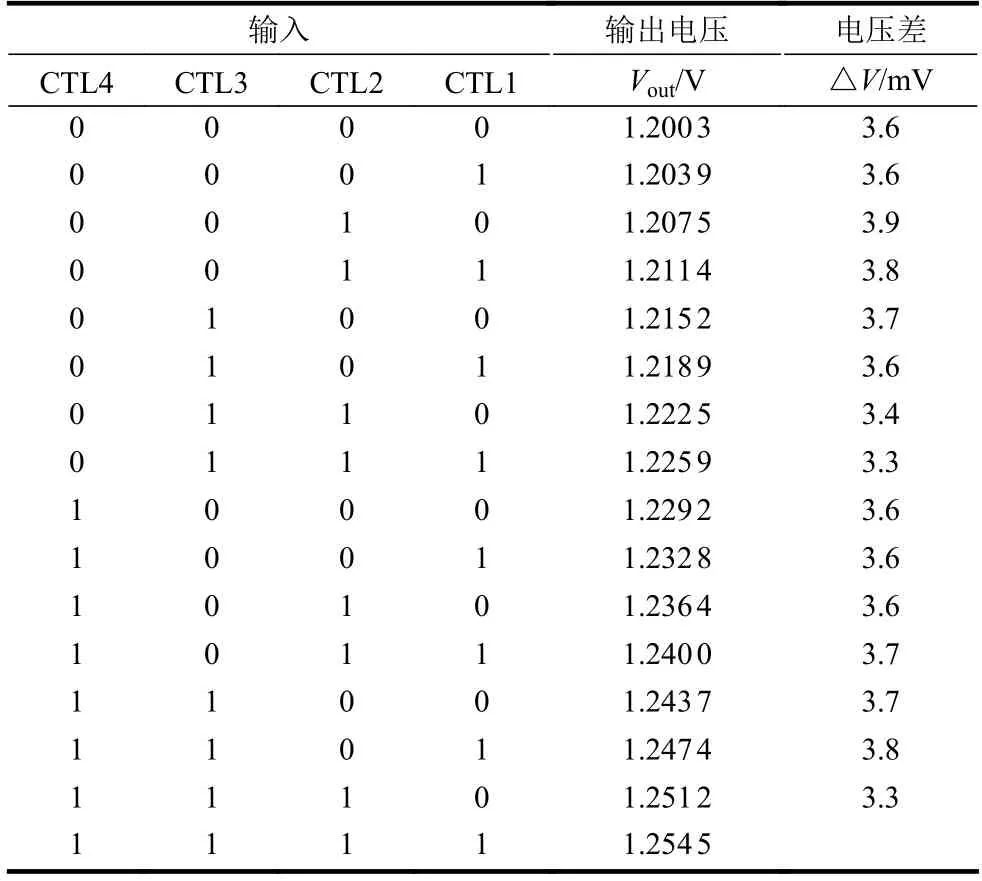

5 电路测试

在实验室进行DAC 的测试,测试现场如图11所示。通过改变DAC 的输入,来改变接入DAC电流源电路输出电流的大小,使DAC 输出电压相对应的改变。表1 为低4 位DAC 的测试数据表,由测试结果可以看出,低4 位DAC 在输入偏置电流为3.73 uA 时,仍可得到合适的输出,且精度误差均小于7%,可见其精度好于4 mV。对用于细调的低4 位DAC 输出数据进行线性处理,得到其DNL为−0.10~0.09 LSB,INL 为−0.01~0.18 LSB,均小于0.2 LSB,符合设计要求。将测试数据的输入输出传输曲线与理想的输入输出传输曲线进行对比,对比图如图12 所示。由测试数据可得此设计噪声低,精度高,动态范围大,各参数均符合设计的要求。因此,本文通过组合两个4 位DAC,分别进行粗细阈值调节,来实现一个8 位DAC 阈值调节的方法是具有可行性的。

图11 测试现场图

图12 低4 位DAC 理想和测试的输入输出传输曲线对比图

表1 低4 位DAC 测试数据表

测试结果表明,本文的设计具有良好的线性,但也仍然存在误差。经过分析,误差产生的原因主要在偏置电路的结构设计上,形成电流源阵列的晶体管需要的偏置电流过小,测试时实现起来较难,会造成一定的误差,可以通过优化和改进偏置电路的结构来设置合适的偏置电流,减小由这一原因带来的误差。

6 结 束 语

本文介绍了可适用于PSD 阵列探测器读出ASIC芯片中的阈值产生单元模块的设计与实现。利用0.18 um CMOS 工艺实现了该单元电路的原理设计、版图设计、前后仿真和最终的芯片流片。并对流片成功的芯片进行了实验室测试,结果表明其DAC 的积分非线性、微分非线性、输出误差、阈值范围、噪声等性能良好。该单元电路能够为读出ASIC 芯片内的甄别电路提供可调节的阈值电压;通过高4 位DAC 结合低4 位DAC,实现粗细阈值的调节,达到较好的调节精度;并且版图面积小,功耗低,易于集成。本文研究为后续VLAST中PSD 前端读出ASIC 芯片的整体设计提供了重要技术保障,也为读出ASIC 芯片中慢控模块的设计积累了相关经验。