一种相控阵雷达多通道同步方法*

2022-05-19祝昇翔何岷贺志毅王嘉欣

祝昇翔,何岷,贺志毅,王嘉欣

(北京遥感设备研究所,北京 100854)

0 引言

相控阵技术自出现以来,凭借其波束快速扫描和灵活捷变,以及空域滤波和定向能力,大大提升了雷达的威力[1]。早期的相控阵雷达采用经典的和、方位、俯仰三通道方式,使用了大量移相器、衰减器、和差器等模拟器件。而多通道相控阵雷达包括多个天线子阵、射频和信号处理通道,更多地使用了数字方式。采用多通道工作方式后,系统自由度大幅度提升。按照软件无线电的思想,将数字处理部分前移,雷达系统能够支持自适应波束形成、空间谱估计、空时自适应信号处理等先进空域处理算法,极大地提升了系统的性能[2-4]。

目前,多家研究机构开展了多通道相控阵雷达的关键技术研究和系统研制[4-6]。文献[5-6]将新型高速模数转换器(analog to digital converter,AD)和数模转换器(digital to analog converter,DA)用于多通道相控阵雷达模拟器和数字化收发组件研制。采用多通道方式并不意味着通道数目的简单叠加,伴随而来的就是单个通道的采样速率和数据传输速率提升后,多个通道之间的一致性难以保证,导致系统性能下降。文献[7-8]研究了大型分布式阵列雷达的时间、频率和相位同步问题。事实上,对所有多通道相控阵雷达来说,同步问题都是必须解决的首要问题。

随着技术的进步,AD 和DA 的采样速率已达到每秒千兆次采样(gigabit samples per-second,GSPS)量级[9-10]。而传统的并行器件存在采样速率受限,占用管脚多等问题,无法满足多通道和小型化的工程需求。为解决这一矛盾,JEDEC(joint electron en⁃gineering council)组织发布了JESD204B 标准[11],采用串行数据链路和共模逻辑电平方式,简化了系统设计,降低了功耗,支持通道间同步功能,传输速率可达12.5 Gbps。目前,厂商推出了大量支持该标准的器件和知识产权。国内多家单位均开展了基于该标准的多通道数据采集板卡和同步技术研究[12-18]。

针对相控阵雷达多个时钟芯片和多个模数转换器均需要同步的难题,本文提出了一种多通道同步方法,以雷达时序信号为基准,实现多个时钟芯片和模数转换器的同步,以满足同步的实际需求。

1 多通道相控阵雷达

1.1 雷达系统

多通道相控阵雷达系统由天线、射频和信号处理等分系统组成,如图1 所示。其中天线按照天线阵面分为多个子阵,每个子阵与对应的射频通道连接。除了变频收发功能外,射频分系统还负责提供时钟。信号处理分系统由多片高速AD 对多通道的子阵数据进行采集,然后进行数字下变频和滤波,通过数字波束形成得到所需要的波束,进行数字脉冲压缩实现匹配滤波,完成目标检测和识别等功能。

图1 多通道相控阵雷达系统Fig.1 Multi-channel phased array radar system

1.2 问题提出

雷达系统通过发射电磁波信号,并接收目标反射的回波,完成最基本的测距功能。

式中:τ为电磁波往返的双程延时;R为雷达与目标的单程距离;c为光速。

雷达发射波形为线性调频信号,其基带形式为

式中:rect()为矩形信号;T为信号脉宽;k为线性调频斜率。

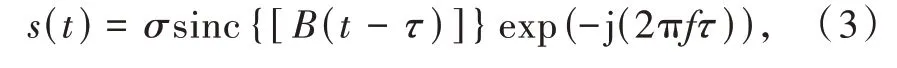

雷达发射的信号被场景中的单个点目标反射后,对收到的回波信号进行数字下变频和脉冲压缩,可得到

式中:σ为目标的散射系数;f为载波频率;sinc()为辛格函数。

雷达系统使用AD 对回波信号进行数据采集,其时序由采样波门和采样时钟决定。当发生采样偏差时,即在时域上产生了Δt的偏差,式(3)变为

此时,脉冲压缩结果发生了Δt的偏差,对应测距结果产生偏差,直接影响后续的目标检测和跟踪环节。特别是对于多通道系统来说,由于多个通道需要进行数字波束形成来实现相参处理,这种偏差的影响更大。

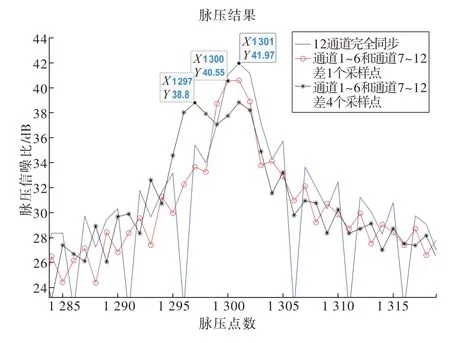

设置线性调频信号带宽为40 MHz,脉宽为26 μs,采样率为100 MHz,使用12 个通道进行仿真,结果如图2 所示。可以看出,当一半通道存在一个采样点的偏差时,数字波束形成的和波束脉压增益下降约1.4 dB。当一半通道存在4 个采样点的偏差时,数字波束形成的和波束脉压增益下降约3.2 dB,而且结果变为了2 个尖峰,严重影响后续的目标检测和测量。

图2 多通道间存在偏差时脉压结果图Fig.2 Pulse compression results with deviations among multiple channels

2 多通道同步

2.1 时钟芯片同步

雷达信号处理分系统由接口板上的现场可编程门阵列(field programmable gate array,FPGA)产生雷达工作时序信号。将该信号作为基准和伴随时钟一起传给数据采集板。数据采集板的时钟芯片对射频分系统中的频率源提供的时钟进行锁相、分频后,输出多路采样时钟、器件时钟以及同步参考信号SYSREF,提供给多片AD 和FPGA,AD以SYSREF 信号为基准进行模数转换,如图3所示。

图3 多通道信号处理框图Fig.3 Multi-channel signal processing

时钟是高速多通道数据采集系统的基准,虽然输入时钟均来自同一个频率源,但是数据采集板的时钟芯片输出的时钟和同步参考信号,与接口板FPGA 输出的基准信号并不能保证每次上电后相位关系一致[19-20]。为了解决该问题,首先采用基于外同步触发信号的同步方法,对单个时钟芯片进行同步。数据采集板的FPGA 根据基准信号的上升沿,在伴随时钟下采样产生同步触发脉冲,并输出给时钟芯片。重新配置其寄存器,使得时钟芯片以同步触发脉冲为基准,重新输出AD 采样时钟和SYSREF 信号等。配置完成之后,时钟芯片输出的所有时钟均以雷达工作时序为基准,完成了单时钟芯片同步,如图4所示。

图4 单时钟芯片同步图Fig.4 Synchronization of single clock chip

由于雷达通道数多,而单个时钟芯片输出时钟数目有限,因此实际当中需要使用多个时钟芯片驱动模数转换器。虽然配置和同步方式完全一致,但是多个时钟芯片所使用的基准信号,伴随时钟以及时钟芯片同步信号对应的印制板走线延时和FPGA内部布线延时各不相同。延时差异导致不同时钟芯片对应的AD 采样结果存在极小的偏差。采用常规方法难以对这类偏差进行测量和补偿。

为了解决多个时钟芯片同步的难题,采用FPGA片内的输出延时单元ODELAY,通过精确的延时调节,实现多个时钟芯片同步信号延时不一致的补偿。具体方法为:使用接口板发射线性调频信号,经过射频通道接收后由数据采集板对收到的信号进行AD采样、下变频、抽取、滤波、脉冲压缩和内插处理,得到脉压峰值点位置。然后以时钟芯片1 对应通道的脉压位置为基准,逐步调节时钟芯片2 对应的时钟芯片同步信号的延时,使得二者最终一致,即可完成多时钟芯片同步,如图5 所示。其中ODELAY 的参考时钟fclk为200 MHz,内部共32 阶,每一阶的延时为1/(2 × 32 ×fclk),约78 ps,根据实际测量结果计算得到延时值,然后写入ODELAY 的配置即可。

图5 多时钟芯片同步框图Fig.5 Synchronization of multiple clock chips

2.2 模数转换器同步

为了满足多通道高速数据采集的需求,选用支持JESD204B 标准子类一的AD 器件,支持传输层的帧填充功能,扰码功能,链路层的8B/10B 编码功能,以及同步字符产生和初始链路对齐功能。该标准定义了链路的确定性延迟,即基于帧的采样数据到达串行发送器的时间与数据从串行接收器输出的时间之差。子类一使用外部参考信号SYSREF 来支持确定性延迟,是器件同步的关键。器件时钟作为系统基准,用于数据采样和捕获SYSREF 信号。确定性延迟的精度取决于SYSREF 和器件时钟之间的关系。当多片AD 需要同步时,为了满足采样窗口的建立和保持时间要求,需要对每一个器件的器件时钟和SYSREF 信号进行走线匹配以保证时序。

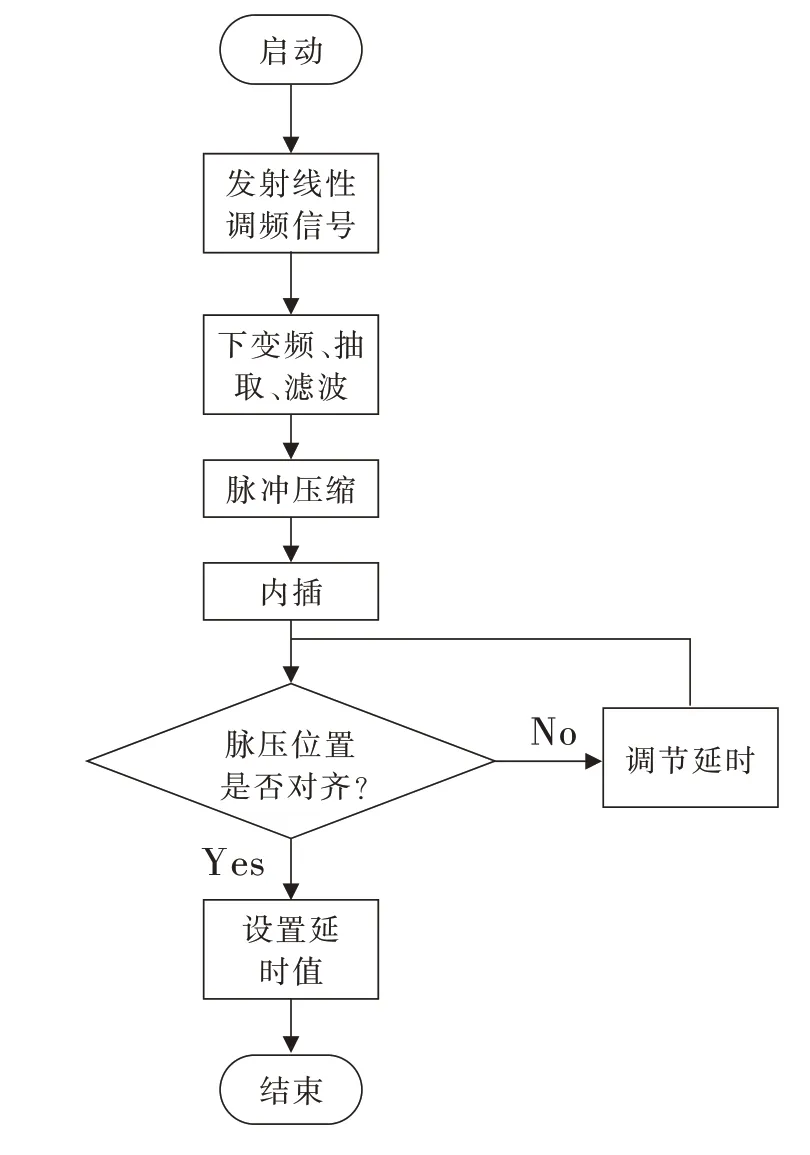

每个AD 通道采用一个JESD204B 控制器进行协议解析和数据格式转换,通过FPGA 实现。根据采样速率,每个控制器内部可设置L个lane(差分信号对)。由于每次上电后各个lane 的数据延时并不相同,导致最后的AD 采样数据延时也各不相同,因此提出一种自适应采样窗口中心调节的AD 多通道同步方法,以实现自校准同步。

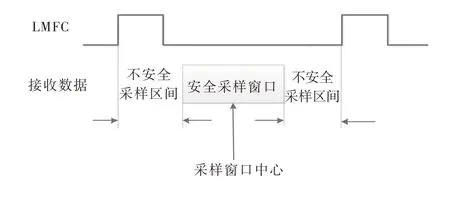

假定帧大小F=2,每个多帧中的帧数K=16,二者的乘积为多帧大小MF=32。根据本地多帧时钟(local multiframe clock,LMFC)的时序要求,采样时刻需要在安全采样窗口内,才能保证可靠采样,如图6 所示。根据此MF值,扣除掉不安全采样区间后,得到安全采样窗口的范围应为8~24。

图6 采样窗口图Fig.6 Sample window

在AD 配置完成后,依次读取L个lane 对应的延时缓冲寄存器,获取每个lane 的延时值,并求它们的最大值。根据该最大值的大小设置移位值,将采样中心统一移到16,即安全采样窗口的中心位置,并写入SYSREF 寄存器,从而调节SYSREF 同步信号时序进行对齐。需要注意的是,移位方向是单向的,因此当延时值大于采样中心位置16 时,需要按照折叠方式设置移位值。最后,对所有AD 通道对应的JESD204B 控制器在同一时刻进行复位,即可完成多个AD 通道的同步,如图7 所示。多通道同步精度为一个采样点,如果AD 采样率为1 GSPS,则可实现的同步精度为1 ns。

图7 多通道AD 同步流程图Fig.7 Synchronization of multi-channel AD

3 测试结果

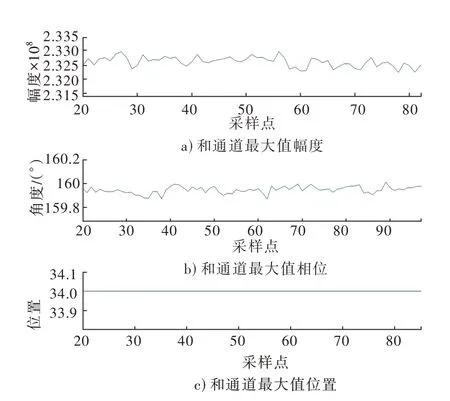

对相控阵雷达多通道同步性能进行测试。上电后用模拟器发射线性调频波形,用数据采集板接收并采集多通道数据。将经过AD 采集、混频、抽取、滤波等处理的数字下变频实时处理数据,存储在数据采集设备后,对数据进行后处理分析,结果如图8,9 所示。图8 为多通道脉压结果的位置,峰值位置均为34。图9 为在多个脉冲重复周期测得的数字波束形成的和波束幅度、相位和脉压位置。可以看出,经过多通道同步处理后,脉压位置、信号幅度和相位都是稳定的。

图8 多通道脉压位置图Fig.8 Pulse compression positions of multiple channels

图9 和波束幅度、相位和脉压位置图Fig.9 Amplitude,phase and position of pulse compression of sum beam

4 结束语

本文针对多通道相控阵雷达面临的同步问题,提出了一种多通道同步方法。首先采用基准时序产生触发脉冲实现单时钟芯片同步,然后对同步信号进行ps 级精确延时补偿实现多时钟芯片同步,采用自适应采样窗口中心调节实现多路AD 的精确采样同步,最终实现了相控阵雷达多个通道的稳定同步。将该方法应用于实际产品,确保了雷达系统的测量性能,具有较高的应用价值。