一种新型异质结双栅隧穿场效应晶体管

2022-05-08江瑞

江 瑞

(上海电力大学 电子与信息工程学院,上海 200090)

摩尔定律指出:集成电路中可容纳的晶体管数目大约每经过18个月便会翻一番[1],CMOS技术的发展也一直遵循摩尔定律,但是MOSFET器件的特征尺寸缩小也越来越接近物理极限。目前,CMOS工艺技术已经朝着7 nm及以下技术节点不断推进,随着特征尺寸微缩进入纳米量级带来了一系列问题。如:短沟道效应,亚阈值摆幅退化以及集成度提高带来的功耗问题[2]。传统的MOSFET基于载流子漂移扩散机制,其亚阈值摆幅(SS)受热载流子效应的影响,在室温下无法低于60 mV/dec[3],而隧穿场效应晶体管(TFET)是基于量子力学带带隧穿原理。这种工作机制不受温度和载流子玻尔兹曼分布的影响,可以突破MOSFET器件亚阈值摆幅的限制,从而大大降低器件的功耗[4-6]。此外,TFET具有极低的关态电流和较大的开关电流比等优点,并且能够与传统CMOS工艺兼容。因此,TFET被认为是最具发展潜力的低功耗器件之一[7]。

当然,TFET器件也面临着许多困境,最主要的便是开态电流较低以及双极性电流的问题[8-9]。TFET的开态电流主要由隧穿电流提供,其隧穿几率主要受到材料的禁带宽带、载流子的有效质量以及隧穿结处电场强度的影响[10]。传统的硅基TFET因其较小的带带隧穿几率,导致开态电流较低,研究表明采用Si/SiGe异质结、pocket结构、高k/金属栅结构及栅源交叠等方式可以有效地增大开态电流[11-12]。2011年,Wei Cao等人提出可以在传统TFET器件中插入一个N型重掺杂pocket结构,与传统TFET相比该结构可以更好地实现源区的突变隧穿结,通过缩短隧穿距离进而提高了带带隧穿几率,获得更高的开态电流。此外研究还发现该pocket结构还可以相应地减少界面陷阱的产生和栅极泄露,降低器件功耗[13];东芝公司在2014年率先研发制备了隧穿场效应晶体管,同年的国际固态器件和材料会议(SSDM)上,东芝公司报道了基于Si与SiGe的TFET器件有关研究。其采用纵式结构结合Si/SiGe异质结技术使TFET开态电流较常规TFET提高了100倍[14-15];2016年,杨兆年提出了一种新型L型栅结构TFET器件(LG-TFET),该器件加入了一个L型N+pocket结构使得水平与垂直方向均发生载流子隧穿,从而增大了隧穿几率,提高了开态电流。研究表明在0.2 V电压下,其最小亚阈值摆幅达到38.5 mV/dec[16]。

本文基于TCAD仿真的方法,提出一种凹槽型pocket结构Si/Ge异质结双栅隧穿场效应晶体管(GP_Si/Ge_DGTFET),并与传统Si/Ge异质结双栅隧穿场效应晶体管(Si/Ge_DGTFET)的性能进行比较。仿真结果表明,其转移特性、开态电流、亚阈值摆幅性能都有明显改善。论文总共分为3个部分,第1部分介绍器件的结构、材料参数、掺杂浓度以及仿真所用到的模型等,第2部分是仿真结果的讨论,第3部分给出结论。

1 器件结构与仿真参数

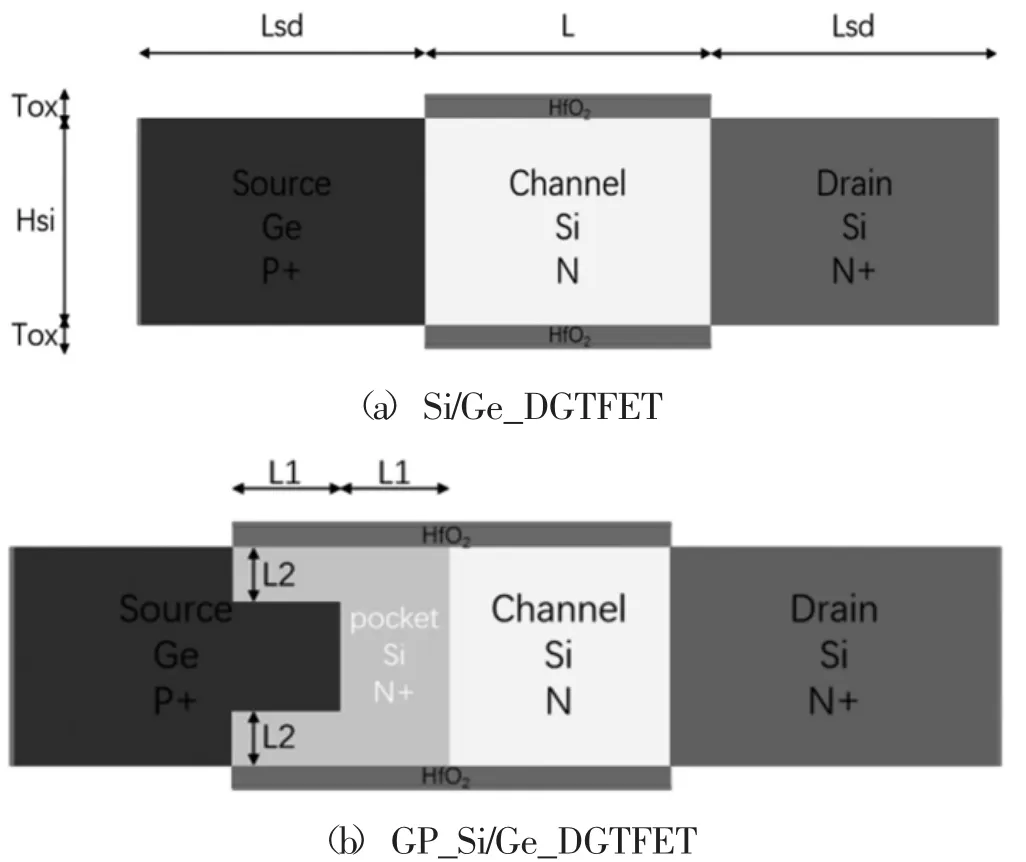

传统Si/Ge异质结双栅隧穿场效应晶体管(Si/Ge_DGTFET)器件结构示意图如图1(a)所示,凹槽型pocket结构Si/Ge异质结双栅隧穿场效应晶体管(GP_Si/Ge_DGTFET)器件结构示意图如图1(b)所示。源区均采用Ge材料,掺杂浓度为1×1020cm-3的P型重掺杂,沟道区和漏区均采用Si材料,掺杂浓度分别为1×1015cm-3的N型轻掺杂和1×1018cm-3的N型重掺杂,以上掺杂过程均为均匀掺杂。对源区进行重掺杂能够减小隧穿宽度,提高隧穿几率,实现陡峭的亚阈值摆幅和高开态电流,相反,漏区轻掺杂可以提高关断状态下漏端的隧穿距离,从而有效抑制泄漏电流。栅氧化层采用介电常数更高的HfO2材料,提高了栅极电压对电流的控制能力,提高器件性能。图1(b)中pocket区掺杂浓度为1×1018cm-3的N型重掺杂。其他具体数据见表1。

图1 器件结构示意图

表1 器件参数

本文是基于Sentaurus TCAD半导体仿真软件完成的,该仿真软件采用自洽方法求解泊松方程和载流子连续性方程。在仿真模型的选择上:由于器件各区域多为重掺杂,高掺杂浓度会在半导体材料能级中引入掺杂杂质能级,从而产生禁带变窄效应,为此仿真时加入了禁带变窄模型;半导体在进行掺杂后,载流子的迁移运动会受到电离杂质散射的作用,从而导致迁移率下降,仿真时加入与掺杂浓度相关的迁移率模型,另外,迁移率也与电场强度相关,在高电场情况下会达到饱和,因此仿真时需加入高电场迁移率模型;由于重掺杂会引入深能级杂质和缺陷,使得间接复合对器件中载流子寿命和器件性能产生较大影响,因此选择SRH复合模型;由于电子和空穴在隧穿路径上非局部的生成,不同位置处电子和空穴生成的速率不同,器件在隧穿路径上各点处的电场也并不相等,因此仿真中选用了非局部带带隧穿模型。

2 仿真结果及讨论

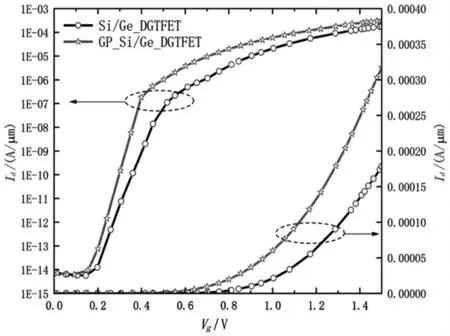

图2是漏源电压Vd=1 V的情况下,传统Si/Ge异质结双栅隧穿场效应晶体管(Si/Ge_DGTFET)与凹槽型pocket结构Si/Ge异质结双栅隧穿场效应晶体管(GP_Si/Ge_DGTFET)转移特性对比图。图中Vg为栅源电压,Id为漏源电流。从转移特性曲线可以看出,对比Si/Ge_DGTFET,GP_Si/Ge_DGTFET在关态电流上没有明显区别,约为10-14A/μm。GP_Si/Ge_DGTFET的开态电流为6.0×10-5A/μm,Si/Ge_DGTFET的开态电流为2.07×10-5A/μm,相比于Si/Ge_DGTFET,约有三倍的增长。开态电流的提升主要归功于pocket结构的引入,它能够与源区形成简并的P+-N+结,为源区和沟道区提供了更小的隧穿带隙,从而提高了带带隧穿几率。

图2 转移特性曲线

亚阈值摆幅(SS)是描述器件栅极对漏电流控制能力的重要参数,定义为转移特性曲线上,亚阈值区域里(上图Id处于1E-14~1E-07段),电流变化一个数量级,所对应的栅源电压的变化量代表了器件的开关转换速度,亚阈值摆幅越小,器件开关转换速度越快。故亚阈值摆幅越小,器件的性能越优异。亚阈值摆幅如式(1)计算:

图3所示柱状图为漏源电压Vd=1 V时,Si/Ge_DGTFET与GP_Si/Ge_DGTFET的亚阈值摆幅随Id的变化情况。从图中可以看出,漏源电流Id每变化一个数量级所对应的亚阈值摆幅GP_Si/Ge_DGTFET均小于Si/Ge_DGTFET,且GP_Si/Ge_DGTFET的平均亚阈值摆幅为35.36 mV/dec,而Si/Ge_DGTFET的平均亚阈值摆幅为47.48 mV/dec,表明GP_Si/Ge_DGTFET的亚阈值特性更好,开关转换速率更快。

图3 SS随Id变化柱状图

3 结论

本文提出了一种凹槽型pocket结构Si/Ge异质结双栅隧穿场效应晶体管(GP_Si/Ge_DGTFET)。该器件在异质结的基础上加入凹槽型pocket结构,源区采用禁带宽度窄,载流子有效质量小的Ge材料可以提高隧穿几率,异质结结构可以实现更为陡峭的隧穿结,pocket结构的引入减小了隧穿势垒和隧穿距离,从而获得了更低的亚阈值摆幅和更大的开态电流。通过仿真,该器件的开态电流为6.0×10-5A/μm,关态电流约为10-14A/μm,平均亚阈值摆幅达到35.36 mV/dec。