基于SiP技术的网络测量探针芯片集成设计*

2022-04-27张春平潘福跃

毛 臻,张春平,潘福跃,顾 林

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

探针是网络测量中的基础和关键部件,在获取网络数据的同时还要进行性能参数分析,执行一种或多种网络测量动作。探针系统主要由探针硬件平台、探针软件平台、探针应用程序三部分组成。早期的国内外探针系统硬件平台主要基于X86架构的商业计算机实现,随着嵌入式硬件系统性能和数据处理能力的不断提高,嵌入式处理器首先在美国CAIDA机构的探针中得到应用,由于成本低、功耗低、部署方便,很快得以大规模普及[1-4]。而随着物联网、大数据、人工智能技术的发展,高带宽、低延迟、广部署对探针系统的要求更加迫切。为了解决各芯片间高速互连信号延迟、数据吞吐率瓶颈等问题,本文设计了一种采用系统级封装(System in Package,SiP)技术的探针系统硬件平台,把现场可编程门阵列(Field Programmable Gate Array,FPGA)集成在网络芯片和CPU之间进行数据预处理,通过高密度基板互连设计使探针系统具备可定制、小体积、低功耗、异构集成等特点,为网络测量探针硬件平台适应新的应用提供了一种解决思路。

2 基于Ark的主动测量架构和原理

主动网络测量技术首先构造出探测报文序列,通过探针发送到被测目标网络中,然后利用被测目标的响应信息,或者利用探测报文传输经过目标网络后携带的信息来测量网络性能[1-3],基于群岛结构(Archipelago Measurement Infra-Structure,Ark)的主动测量架构如图1所示。由于主动测量探针部署位置靠近用户终端,通过主动网络测量技术,可以进行端到端的网络路径性能测量,测量结果能更直接地反映用户的网络体验。另外,采用分布式部署网络探针获取的测量数据有助于管理员获得对于网络整体性能的认识。

图1 基于Ark的主动测量架构

许多大型的网络测量项目由政府或国家机构赞助开发,比如CAIDA就是由美国国土安全部(US Department of Homeland Security,DHS)、国家科学基金会(National Science Foundation,NSF)、国防高级研究计划局(Defense Advanced Research Projects Agency,DARPA)、圣地亚哥超算中心等部门共同支持建立。截至2019年2月,CAIDA在全球有247个活动探测点[4]。CAIDA的网络总体架构也称为群岛测量构架,其核心服务器位于圣地亚哥超级计算机中心。基于该系统的探针从2006年上线以来持续进行改进,内置了域名系统(Domain Name System,DNS)解析分析、网络拓扑分析、Web响应分析、Ping时延分析、路由跟踪(Traceroute)等多个工具[5-8]。目前活动的网络测量项目及探针分析如表1所示。

表1 目前活动的网络测量项目及探针分析

从表1可以看出,大部分主动式网络测量项目的探针都是工具软件加PC端方式,需要台式机或笔记本电脑在Widows、MAC OS或Linux中安装工具软件运行。目前只有RIPE Atlas、CAIDA的Archipelago和Polaris是嵌入式软硬件结合的探针。

3 Ark探针性能分析

完成网络性能参数测量是探针的基本功能[9]。探针需要进行高速率的发送分组或者高速捕获分组并进行统计分析,探针CPU的处理能力、网络接口的吞吐能力决定了探针的主要性能[10-11]。

CAIDA的主动网络探针采用了软硬件开源的树莓派2B,该探针的主控采用BCM2836四核Cortex-A7 900 MHz的片上系统(System on Package,SoC)。整个树莓派2B的尺寸为85 mm×56 mm×17 mm,板上除主控芯片外,还有一颗10/100自适应以太网和USB2.0 PHY二合一芯片以及一颗1 GB内存芯片。树莓派2B能运行全系列ARMGNU/Linux发行版,支持Snappy Ubuntu Core,单线程满载运行情况下功耗小于5 W。

4 国产化网络探针设计

本设计中的国产化网络测量探针芯片集成了CAIDA探针系统除电源芯片外的大部分芯片。采用SiP技术的探针芯片,从探针系统基本要求和关键技术出发,从架构实现、国产化器件选型、SiP实现、性能指标分析和软件配套等几个方面进行详细设计。

4.1 探针需求和关键技术

在分布式网络测量过程中,由于探针分布在不同的地区,探针之间时钟不同步会引起测量误差,时钟同步能保证如端到端时延性能等指标测量的准确性[12]。针对Web服务器性能进行的测量,需要探针能够产生高速分组数据流。TCP/IP协议负载分析测量需要进行校验和的计算、数据搬移和TCP/IP协议处理[10]。除以上指标外,网络接口吞吐能力和CPU的处理能力也是探针设计的关键指标。由于需要监控网络性能和网络运行健康状态,需要探针能够在高速捕获网络数据分组的同时,同步进行一些统计分析。在探针设计时加入高性能FPGA芯片,利用FPGA可配置、并行计算的特点,完成网卡分组数据的预处理,包括分组捕获、解包、过滤、归类等。经过FPGA预处理后的数据再通过PCIe或芯片内部总线(如ZYNQ系列的AXI总线)高速传输给CPU,这样的处理架构降低了CPU的处理负担,大大提高了探针的网络接口吞吐量和系统性能[10-11]。

4.2 架构设计和器件选型

针对4.1节提出的探针功能需求和关键技术指标要求同时兼顾可扩展性,基于SiP技术的国产化网络探针芯片采用CPU+FPGA的处理架构。其中CPU选择自带以太网媒体接入控制器(Media Access Control,MAC)的芯片,物理层收发器(Physical Layer transceiver,PHY)不是直接和MAC对接,而是由FPGA转接。实验证明由FPGA控制MAC可以提升约20 Mb/s的发送速率,在捕获模式下,由FPGA对数据包进行预处理,如对包头进行信息的预处理和错误包、碎片包的分组等,可以提高分组捕获分析能力和网络接口吞吐率[10]。由于本探针芯片已集成了传统探针系统的大部分功能芯片,所以基于SiP技术的探针芯片即代表了整个探针系统的性能,表2为采用本设计的探针与CAIDA的探针性能对比。DMIPS(Dhrystone Million Instructions Executed per Second)主要用于测整数计算能力,一个处理器达到1 DMIPS的性能是指这个处理器测整数计算能力为每秒1×106条指令。

表2 采用SiP芯片的探针与CAIDA的探针性能比较

从表2可以看出,内部集成FPGA逻辑单元的处理器架构是本设计与CAIDA探针芯片最大的区别,CPU和CAIDA探针内部的四核ARM Cortex-A7性能相当。除处理器和FPGA外,本探针芯片内部还集成了2颗国产DDR3裸芯片,型号为43-46TR16512BL,总容量为2 GB,比CAIDA探针的内存扩大1倍。为增加网口吞吐率,芯片内部集成了国产千兆以太网PHY裸芯片J88E1111,与CAIDA探针的百兆接口相比,可以大大提高网口传输速率,适应更多网络测量应用场景。图2为本探针芯片的内部架构框图。为方便应用,本芯片内部还集成了系统加载用国产Flash,裸芯片型号为FM25F128。内部集成该Flash后无须像CAIDA探针一样外插SD卡,在提高系统可靠性的同时,还可以大大缩小整个探针的硬件体积。

图2 探针芯片内部架构

由于主动网络测量需要严格的时间同步,因此系统中本地时钟模块的振荡器最好采用温度补偿晶振,但是一般在SiP设计中,为提高整体系统可靠性,晶振均采用芯片外配置的设计,不考虑集成在SiP芯片内部。

4.3 探针芯片系统级封装设计

在系统级封装设计前,需要进行系统功能和性能的原型验证,即在PCB板上采用成品芯片进行电气互连,以验证系统功能和互连的正确性以及接口预留的合理性,原型验证完成后裸芯片选型也同步确定。

原型验证完成后,进入系统级封装设计阶段。由于DDR3、网口PHY裸芯片和Flash裸芯片原PAD分布为wirebonding形式,需要先将再布线工艺(Redistribution Layer,RDL)转 换 为 倒 装 工 艺(Flip-Chip,FC),与其他FC装片的裸芯片和阻容一起在塑封基板上进行回流焊,从而实现电气互连。为进一步减小整个探针芯片的面积,将DDR3两颗裸芯片进行三维堆叠后首先形成微组件。一颗微组件由两片512M×16 bit的裸芯片堆叠组成32 bit位宽的内存芯片。由于DDR3裸芯片PAD分布方便向中间开槽进行键合,所以RDL其实是把中间的两排PAD通过再布线技术扇出到芯片一边,在DDR3微组件基板堆叠时交错放置,并分别向两边进行wirebonding。图3为RDL和两层wirebonding堆叠示意图。

图3 RDL和两层wirebonding堆叠示意图(侧视)

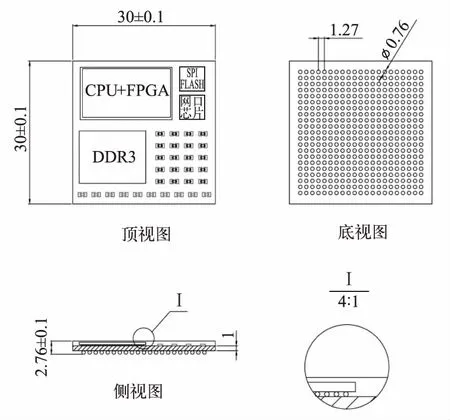

经过以上设计,整个探针芯片的系统级封装由两颗RDL转FC的裸芯片、一个两片DDR3堆叠后的微组件、一颗FC形式的SoC裸芯片以及若干阻容组装在塑封基板上完成。设计完成后的尺寸为30 mm×30 mm,封装形式为PBGA484,图4为封装示意图。

图4 封装示意图(单位:mm)

4.4 SiP仿真

在-10~120℃环境温度条件下,对SiP整体结构进行自然散热仿真模拟,其中,SiP总功耗为4.92 W。已知硅芯片的失效温度为175℃(考虑仿真误差,一般将结温控制在150℃以内)。仿真结果显示,在120℃条件下,硅芯片均不会失效,SiP能正常运行。120℃条件下的热仿真结果如图5所示。

图5 120℃环境温度时SiP热仿真结果

5 软件设计

探针芯片设计完成后,需要配套相应的软件工具。目前大部分的探针类工具软件都是运行于开源的操作系统上,多基于Ruby和Python进行开发,其工具本身也是开源的。常用的探针芯片采用Linux操作系统,系统层包括嵌入式Linux操作系统、设备驱动程序和优化的TCP/IP协议栈。TCP/IP协议栈的优化主要根据硬件平台功能,简化分组数据校验和的计算,根据RISC微处理器的特点优化一些程序数据处理的方法,并向上层提供标准的Socket编程接口[13-14]。常用的测量对象和对应模型、协议或算法见表3。

表3 测量对象和对应模型、协议或算法

本探针芯片内部集成了可编程逻辑单元,因此可以在可编程逻辑(Programmable Logic,PL)端借助已有IP进行接口扩展和数据并行预处理等操作。由于不能采用通用的MAC IP,网络接口还需要采用Verilog硬件描述语言进行定制。在处理系统(Processing System,PS)端进行操作系统的安装,PL端的数据和PS端的数据通过AXI总线进行交互[15]。

6 结论

本文基于SiP技术和已有的国产化裸芯片进行国产化网络测量探针芯片系统级设计。与国外的分布式网络测量用探针相比,使用本设计作为主控的探针具有体积小、重量轻、集成度高、芯片全国产化等特点。同时,基于本设计的探针,工具软件可以全部固化后分发,并支持远程唤醒、远程调试以及远程固件升级等,使得部署、维护和使用成本大大降低。全国产化网络测量用探针芯片在采用系统级封装技术实现体积缩小、性能提高的同时,可以从芯片级层面保证一些敏感性网络,如校内网、企业内部网、政务专网、军用专网等网络测量过程中数据收集的安全和保密。