基于Sigma-Delta 调制技术的高精度数字磁通门磁强计仿真*

2022-04-13陈武祥王劲东吕尚李云鹏薛永亮宋伟

陈武祥 王劲东 吕尚 李云鹏 薛永亮 宋伟

1(中国科学院国家空间中心 空间天气学国家重点实验室 北京 100190)

2(中国科学院大学 北京 100049)

0 引言

磁通门磁强计是一种基于软磁材料非线性工作的矢量磁场测量装置,其测量的基本原理是法拉第电磁感应定律,常用于测量恒定磁场和低频磁场。由于磁通门测量在测量精度、灵敏度、线性度、稳定性和功耗等方面具有独特优势,目前已经成为空间磁测量领域应用最为广泛和性能最可靠的载荷之一[1]。磁通门磁强计分为模拟和数字两大类别,模拟磁通门磁强计需要高精度的模拟元器件实现信号解调与处理,系统性能受电路元器件影响较大。随着数字信号处理技术的进步,小型化、低功耗的数字磁通门磁强计技术发展迅速。数字磁通门磁强计通过模数转换器(Analog to Digital Converter,ADC)对传感器模拟信号进行采样量化,在数字域完成信号处理过程[2]。数字磁通门磁强计的性能依赖ADC 的分辨率,但是经典的Nyquist ADC 受当前技术的制约,无法同时满足高采样率、高分辨率和低功耗的要求。

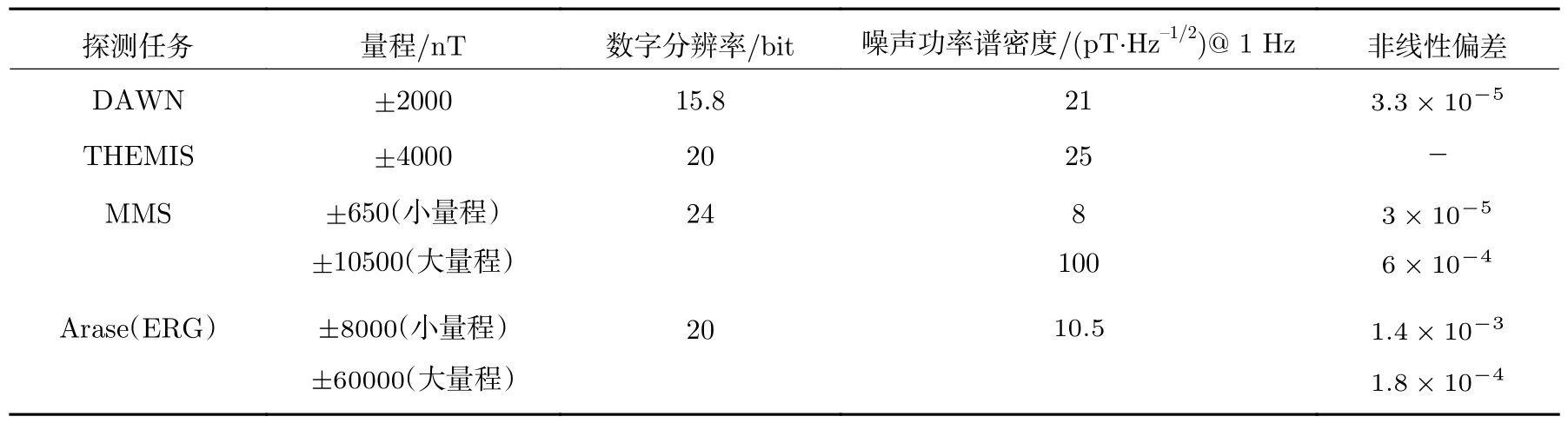

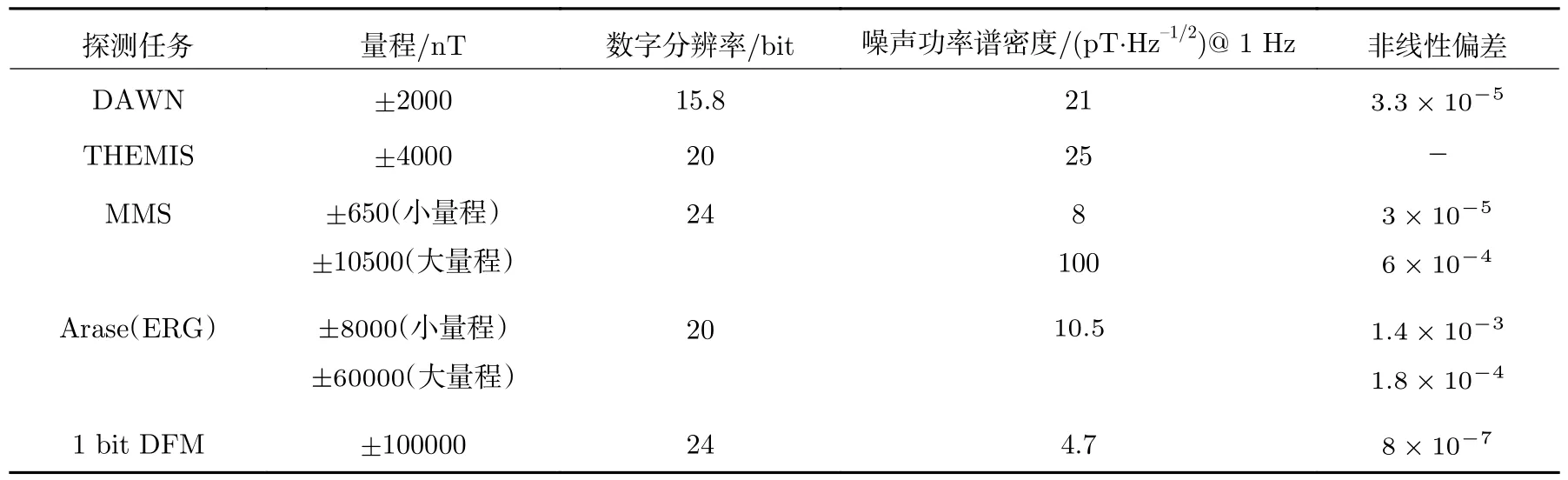

Sigma-Delta 调制器技术可以有效解决上述问题,该项术能够基于低精度的A/D 转换器(量化器)获取高分辨率的量化输出结果。2003年,Magnes等[3]结合了Sigma-Delta 调制技术创新地提出了一种新的数字磁通门磁强计架构,并应用于NASA 探索计划DAWN 任务的数字磁通门磁强计中。该磁强计摒弃了传统的高精度A/D 转换器,取而代之的是使用了二阶单环Sigma-Delta 调制器,仅使用比较器和1bitD/A转换器,最终系统测量的分辨率高达15.8bit,最小系统噪声仅为21 pT·Hz–1/2。这种新型数字磁通门架构同样被用于2007年的THEMIS 任务中,应用于地面的磁通门磁强计阵列[4],系统分辨率达到20 bits,噪声为25 pT·Hz–1/2。2015年NASA发射了用于研究地球磁层磁重联现象的磁层多尺度探测(Magnetospheric Multiscale,MMS)卫星,其中搭载的数字磁强计中使用了级联架构的Mash 2-2 Sigma-Delta 调制器,仅使用了比较器和1 bit D/A 转换器,分辨率达到24 bits,系统噪声仅为8 pT·Hz–1/2[5]。2016年发射的Arase(ERG)Satellite 卫星搭载的数字磁强计则使用了一阶Sigma-Delta 调制器,14 bits的A/D 转换器与12 bits 的D/A 转换器,系统整体分辨率达到20 bit,系统噪声为10.5 pT·Hz–1/2[6],文中提及的空间探测Sigma-Delta 数字磁强计性能参数列于表1。

表1 空间探测Sigma-Delta 数字磁强计的性能参数Table 1 Performance of Sigma-Delta digital fluxgate magnetometers for space exploration

目前中国暂时未见到基于1 bit Sigma-Delta 调制技术的数字磁通门磁强计的报道,亟待开展相应研究 工作。

1 磁通门磁强计信号分析与建模

磁通门传感器(Fluxgate Sensor)利用高导磁率磁芯,在饱和励磁下选通磁芯中的磁场分量信号,从而将低频磁场分量转变为交变电压信号输出。磁通门传感器具有灵敏度高、稳定性好、线性度好等特点,适用于测量106nT 以下的弱磁场信号。

1.1 探头信号分析

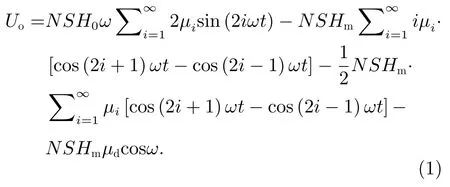

磁通门磁强计探头由磁芯和线圈两部分组成,磁通门探头中的线圈分为激励线圈和信号线圈,激励线圈在磁芯中产生饱和交变磁场,通过信号线圈输出感应电压信号。单磁芯磁通门磁强计输出信号的数学模型[7-9]为

式中,N为信号线圈匝数,S为磁芯横截面积,H0为待测环境磁场强度,ω为励磁信号频率,µi为磁芯磁导率的各次谐波分量幅值,Hm为激励磁场的磁场强度,µd为磁导率直流分量。

根据式(1)的磁通门探头工作原理,建立了磁通门传感器输出信号仿真模型。仿真模型基于激励信号频率ω(10 kHz)的各次谐波,最高使用了10 阶谐波(100 kHz)数据对磁通门探头输出信号进行数学建模,图1 给出了磁通门传感器数学模型仿真输出波形。

图1 磁通门探头仿真波形Fig.1 Simulation waveform of fluxgate probe

1.2 信号处理方法

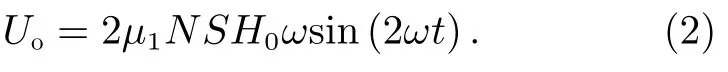

磁通门传感器信号处理流程主要是完成滤波和磁场信号提取。常用的信号提取方法是二次谐波检测法,通过对激励信号的二次谐波的检测完成对外界磁场的测量,由式(1)可知,当N,ω都确定的时候,通过提取二次谐波分量,得到磁通门磁强计的输出电压Uo与外界磁场H0成正比,有

在磁通门磁强计中通常使用负反馈形成闭环系统,在反馈线圈施加反馈电流,形成一个与环境磁场反向的反馈磁场,抵消环境磁场的轴向分量,使磁芯工作在零磁场状态,从而提高磁通门传感器的线性度和稳定度[10,11],图2 给出了模拟磁通门磁强计的信号处理流程。

图2 模拟磁通门磁强计系统Fig.2 Analog fluxgate magnetometer

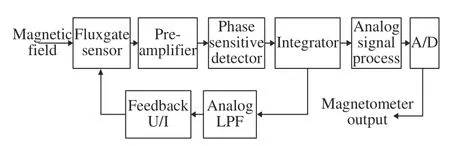

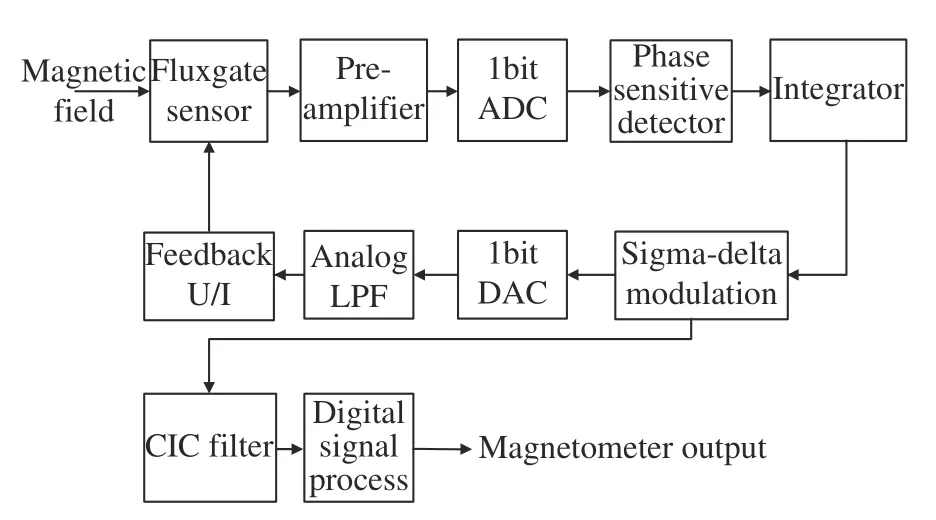

模拟磁通门磁强计使用分立元件来构建系统,电路复杂度高,抗干扰性差。数字磁通门磁强计基于数字信号处理技术,通过A/D 转换器完成对传感器模拟信号的数字化,并在数字域完成磁强计的信号处理[12,13]。本文基于数字磁通门磁强计的基本原理,设计了1 bit 数字磁通门磁强计仿真系统,利用Sigma-Delta 环路调制技术实现高分辨率磁场测量。数字磁通门磁强计信号处理系统由1 bit ADC、1 bit DAC、环路调制器、相敏检波单元、积分器和低通滤波器等模 块构成,如图3 所示。

1.3 Simulink 建模

针对图3 给出的1 bit 数字磁通门磁强计系统,在Simulink 环境下搭建了相应的仿真模型,如图4所示。仿真模型中包括磁通门探头数学模型、1 bit ADC、相敏检波器、数字积分器、环路调制器、1 bit DAC、低通滤波器、反馈驱动模块与输出信号处理等模块。其中,磁通门探头输出电压信号通过1 bit ADC 完成量化,并由相敏检波器与积分器完成信号的解调及输出。通过环路调制器与1 bit DAC 完成反馈回路数字信号到模拟信号的转换,并利用反馈驱动模块将反馈电压信号转换成反馈电流信号,实现系统的闭环测量。最终通过输出数字信号处理模块完成 数据降采样工作,输出磁场测量值。

图3 数字磁通门磁强计系统Fig.3 Digital fluxgate magnetometer

图4 1bit 数字磁通门磁强计仿真系统Fig.4 Simulation system of 1 bit digital fluxgate magnetometer

1.3.1 1bit A/D 转换器

在图4 所示的数字磁通门磁强计仿真系统中,采用1 bit ADC 模块实现磁通门原始信号的量化。1 bit ADC 模块基于Sigma-Delta 调制技术,其原理是低频信号经过采样和噪声整形生成数字信号,在生成的过采样数字信号中,有效信号分布在低频带,而量化噪声由于噪声整形分布在高频带,减少了带内的量化噪声,因此可以得到高分辨率的数字信号[14]。磁通门探头的输出模拟信号经过1 bit ADC,可以得到高 分辨率的数字信号。

1.3.2 相敏检波

相敏检波常用于信号的锁定放大,参考信号与待检波信号的频率与相位相同,通过低通滤波器来抑制宽带噪声,改善系统性能,锁定输出信号幅值信息。

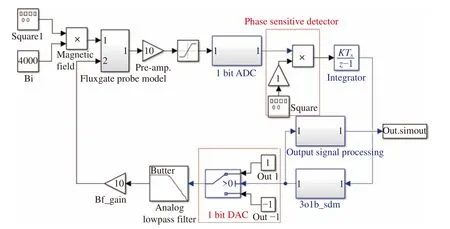

由式(2)可知相敏检波输入的二次谐波信号为

其中,V2就包含了外界的磁场信息H0,相敏检波的参考信号为幅值±Vr,频率为2ω的方波信号,其傅里叶级数为

相敏检波后的结果为

经过低通滤波器的滤波作用,n>0 的高频分量都被滤除,只保留了n=0 的直流分量

经过相敏检波,得到所需要的含有磁场信息的直流信号。仿真中的相敏检波器的参考波形为20 kHz的 方波信号。

1.3.3 1bit D/A 转换器

磁通门磁强计通常采用反馈电路实现闭环测量。在磁通门传感器中,通过反馈线圈形成一个与环境磁场反向的反馈磁场,抵消环境磁场的轴向分量,使得磁芯工作在零磁场状态,从而提高磁强计的测量线性度与稳定性。反馈回路中需要将环路调制器输出的数字信号转换成反馈电压,从而实现闭环磁场控制。在仿真中使用了1 bit DAC 模块配合环路Sigma-Delta 调制器完成了数字信号到模拟信号的转换,利用脉冲宽度调制(Pulse Width Modulation,PWM)实现反馈电压的输出。

1.3.4 其他模块

降采样滤波器由级联积分–梳状滤波器(Cascaded Integrator-Comb filter,CIC)和补偿滤波器构成[15,16]。CIC 抽取滤波器是一种结构简单且容易实现的抽取滤波器,其系数均为1,使用加法器,减法器和延迟单元就能高效的实现对信号的抽取。反馈回路的低通滤波器能够滤除1 bit D/A 的高频调制噪声,并通过反馈驱动模块将电压信号转换为电流信号,驱动磁通门 探头中的反馈线圈产生反馈磁场。

2 调制信号处理

2.1 Sigma-Delta 调制技术

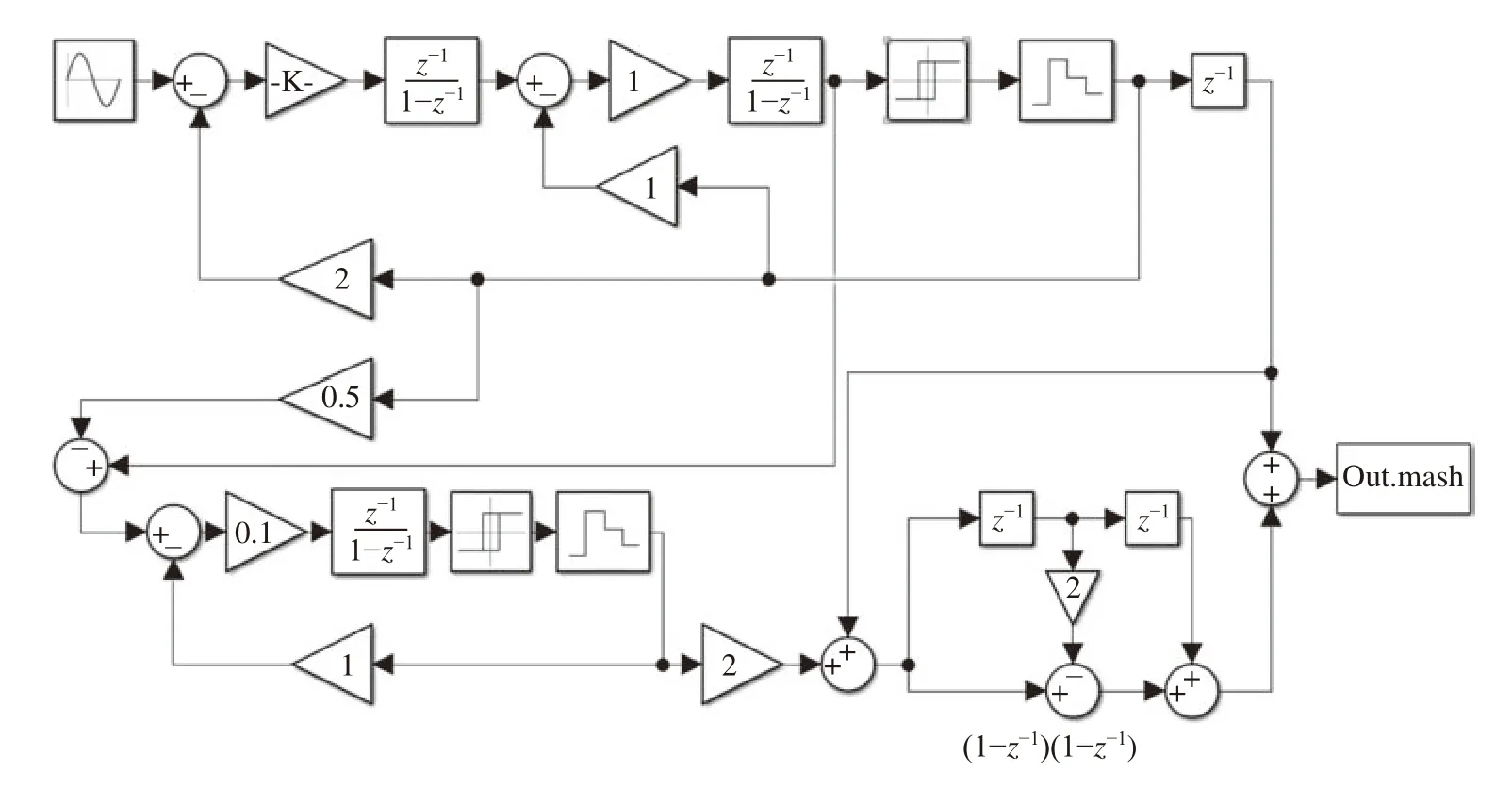

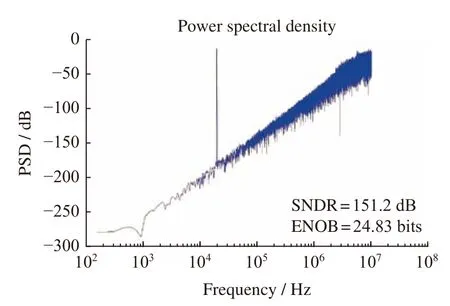

Sigma-Delta 调制技术是1 bit 数字磁通门信号处理方法中的关键技术之一。在图3 的1 bit 数字磁通门磁强计系统中,使用了Mash2-1 级联结构的Sigma-Delta 调制器实现信号调制,如图5 所示。输入信号为频率20 kHz,幅值0.8 的正弦波,在过采样率(Over Sampling Rate,OSR)为512 的条件下仿真得到调制器性能如图6 所示。Mash2-1 调制器的系统性能达到三阶噪声整形的效果,仿真计算得到的调制器性能(151 dB)与理想调制器性能(170 dB)相近,进一步验证了调制器设计的合理性,为高分辨率的S igma-Delta ADC 设计实现奠定了基础。

2.1.1 Sigma-Delta ADC

Sigma-Delta ADC 主要由两部分组成:如图5 所示的Sigma-Delta 调制器和数字抽取滤波器。调制器采样率为20.48 MHz,配合使用抽取率为64 的降采样滤波器和FIR 低通滤波器,实现抽取和滤除高频量化噪声,完成高分辨率模数转换的功能。本文仿真设计的Sigma-Delta ADC 最终实现了24 bits 的量化精度。如图7 所示,Sigma-Delta ADC 实现了对2 0 kHz 的正弦波信号采样量化。

图5 Mash2-1 级联Sigma-Delta 调制器Fig.5 Sigma-Delta modulator of Mash2-1 cascaded modulator

图6 Sigma-Delta 调制器输出信号的SNDRFig.6 SNDR results of Sigma-Delta modulator

图7 1bit ADC 量化结果Fig.7 Sampling and quantization output of 1 bit ADC

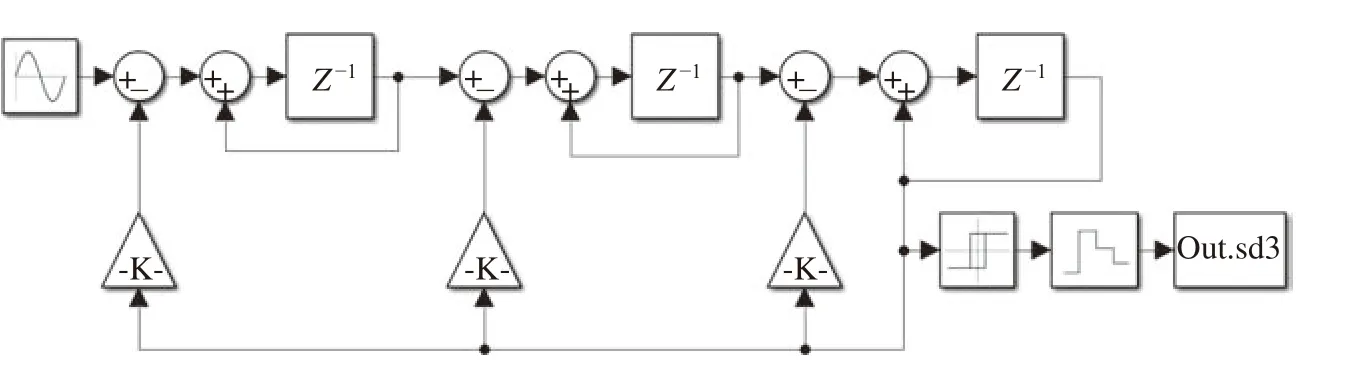

2.1.2 1bit Sigma-Delta 环路调制器

图8 为1 bit Sigma-Delta 环路调制器。其作用是生成高精度反馈数字信号,配合使用1 bit DAC模块完成PWM 调制,实现从数字信号转换成模拟信号,通过反馈回路中的模拟低通滤波器滤除模拟信号中的高频调制噪声,得到高精度的反馈模拟信号,最终完成高精度DAC 的功能。仿真中,环路调制器的采 样频率与数字积分器的频率相同,为5.12 MHz。

图8 Sigma-Delta 环路调制器Fig.8 Loop Sigma-Delta modulator

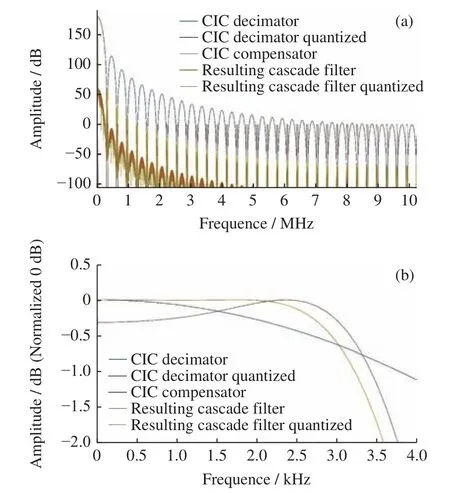

2.2 CIC 降采样数字滤波器

仿真实验中使用了Hogenauer 结构的CIC 滤波器[17]。滤波器的作用是通过抽取来降低信号频率,同时由于其低通特性,能够滤除高频噪声。降采样滤波器组整体结构为CIC 滤波器放在第一级实现抽取滤波,补偿滤波器用于补偿CIC 抽取滤波器通带内滚降的现象,保证通带增益恒定[18]。5 阶CIC 抽取滤波器的阻带衰减为67.3 dB,多级 CIC 滤波器阻带衰减增大,同时其通带幅频特性有明显衰减,这种现象会使Sigma-Delta 调制器的调制性能下降。因此在 CIC抽取滤波器之后要使用补偿滤波器来补偿通带内的衰减。CIC 抽取滤波器的设计使用了Matlab 中的Filter Designer 工具箱。

在1 bit ADC 中,Sigma-Delta 调制器的采样频率为20.48 MHz,CIC 滤波器的降采样率为64,补偿滤波器的通带为20 kHz(有效带宽),阻带为24 kHz,通过滤波器可视化工具得到了CIC 滤波器和补偿滤波器的幅频响应[19],以及级联后的幅频响应,如图9(a)所示。图9(b)则是信号带宽(20 kHz)附近的滤波器幅频特性细节,可以看到,幅值归一化后,级联后的降采样滤波器的通带内保持了增益为0 dB,避免了 带内有效信号的衰减。

图9 1bit ADC 中CIC 滤波器的补偿滤波器与级联滤波器幅频响应。(a)(0,Fs/2)幅频响应,(b) 20 kHz 带宽幅频响应Fig.9 Amplitude-frequency response of CIC filters in 1 bit ADC.(a) Amplitude-frequency response of (0,Fs/2),and (b) response of 20 kHz

3 性能仿真

根据前文对1 bit 数字磁通门磁强计分析建模和信号处理方法的研究,对数字磁强计仿真系统的噪声特性、线性度特性、频率响应特性和动态响应速度特性开展了仿真研究与结果分析。

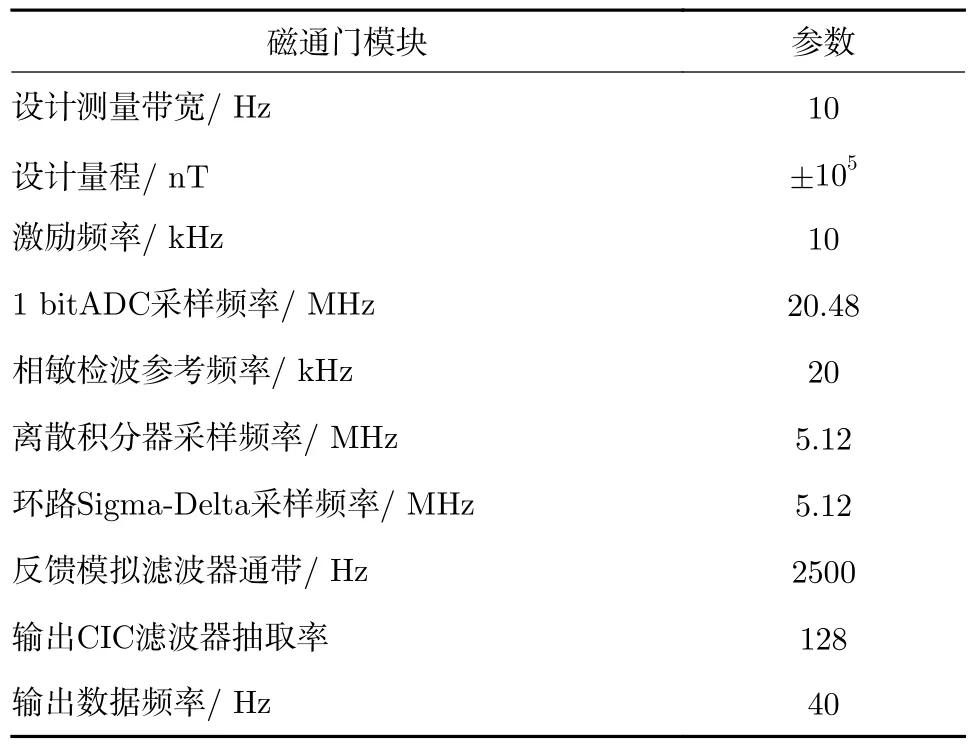

磁强计各模块特性参数列于表2。为了对仿真数据定量标定,测试了实验室的磁通门探头,计算得到该探头的灵敏度为3.9×10−5V·nT–1。输出数据的降采样方法为CIC 抽取滤波器,抽取率为128,级联窗长为1000 的滑动均值滤波器,最终数据频率为40 Hz,输出数据格式为28 位有符号的定点数据,仿真中系统最大输出电压值可以达到5 V,满足设计量程 ±105nT(输出电压幅值为±3.9 V)。

表2 1bit 数字磁通门磁强计各模块参数Table 2 Parameters of modules in 1 bit digital fluxgate magnetometer

3.1 数字磁通门磁强计噪声特性

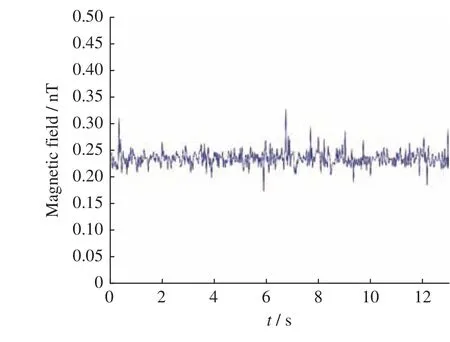

系统的噪声特性是通过对恒定磁场的仿真检测来完成的,计算其时域输出信号和噪声功率谱密度。仿真中设定的环境磁场信号为0 nT,图10 给出了系统输出信号的时域噪声波形,仿真时间为13 s。

图10 零磁场输入时的系统噪声Fig.10 System noise with zero magnetic field input

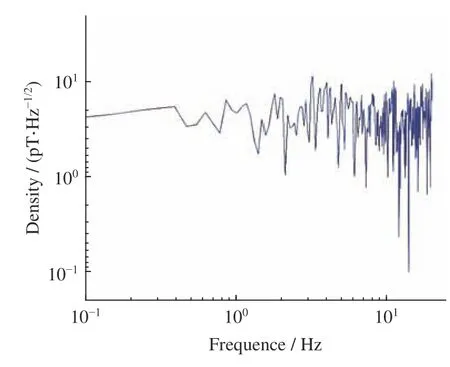

由仿真结果计算得到系统噪声峰峰值为0.1535 nT,噪声有效值(RMS)为0.0146 nT。利用Welch 法计算得到噪声功率谱密度如图11 所示,系统在1 Hz 处的噪声功率谱密度为4.66 pT·Hz–1/2。

图11 系统噪声功率谱密度Fig.11 Power spectrum density of system noise

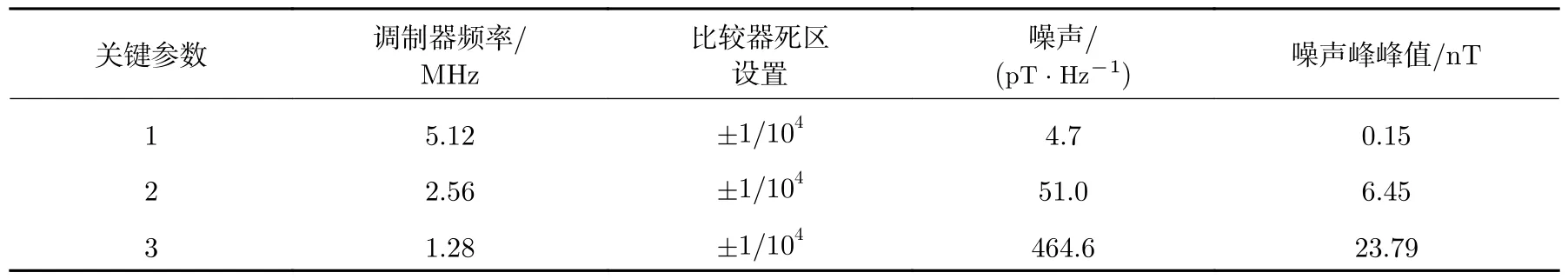

系统噪声的影响因素主要是1 bit ADC 的量化噪声和Sigma-Delta 环路调制器的性能。提高Sigma-Delta ADC 的采样频率,有利于提高1 bit ADC的分辨率,减少量化噪声。在ADC 量化性能一定时,提升环路调制器的频率可以有效提高环路调制器的性能,降低DAC 噪声,从而降低系统噪声,仿真结果列 于表3。

表3 不同参数下环路调制器对系统性能影响的比较Table 3 Performance comparison of different loop modulator parameters

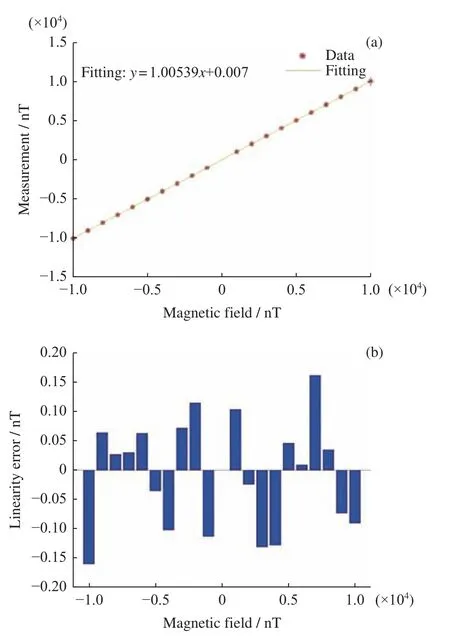

3.2 线性度特性

仿真通过测量恒定磁场探究1 bit 磁强计系统的线性度,采用线性拟合计算系统偏差,从而计算系统的线性度特性。环境磁场设定为±104nT 之间的恒定磁场,步长为103nT,仿真得到的磁场测量结果和线性拟合后的误差如图12 所示。仿真中使用了最小二乘法进行线性拟合,蓝色柱状图为系统输出与线性拟合后的误差。仿真结果表明:最大线性偏差为0.16 nT,为满量程(2 × 105nT)的8×10−7。线性误差的来源主要是系统噪声,改善系统噪声能有效提高系 统的线性度。

图12 测量磁场的输出线性度(a)以及误差(b)Fig.12 Measurement of output linearity of magnetic field (a) and linearity error (b)

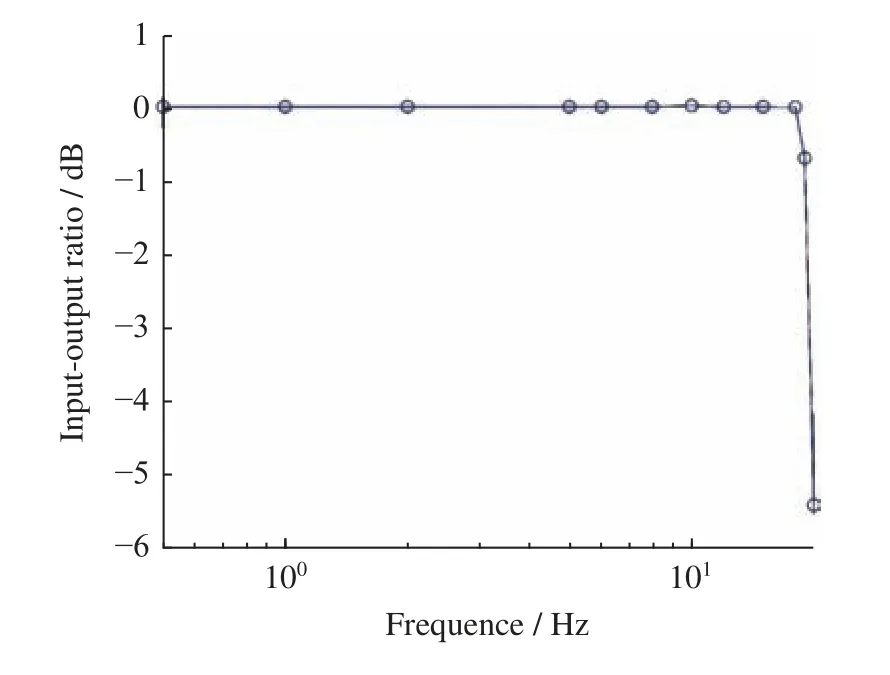

3.3 磁强计频率响应特性

磁强计的频率响应特性决定了该系统的有效带宽。仿真方法为输入0.001~20 Hz 正弦磁场信号,计算系统输出信号幅值与输入信号幅值之比(dB),仿真结果如图13 所示。设计的1 bit 磁通门磁强计系统在10 Hz 内的频率响应恒定,根据仿真结果得到系统的–3 dB 带宽大约为19 Hz。

图13 系统的频率响应Fig.13 Frequency response of magnetometer system

影响系统带宽的因素主要有输出信号处理过程中使用的CIC 抽取滤波器的降采样率及低通滤波器的截止频率。当环路调制器的频率一定时,降低CIC 滤波器的降采样率或者提高低通滤波器的截止频 率可以有效增加系统的有效带宽。

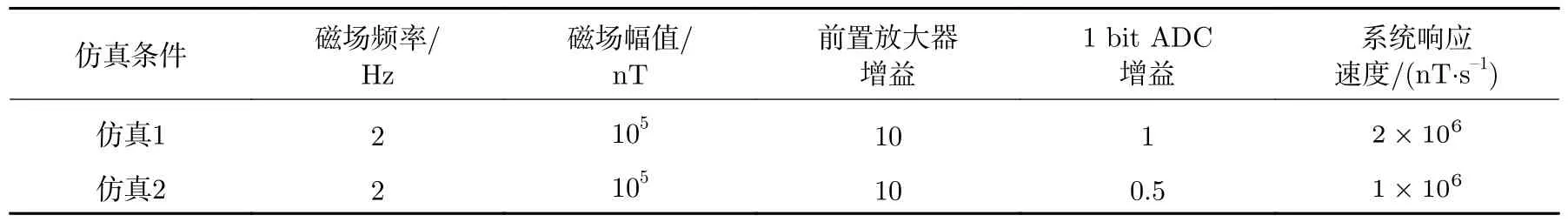

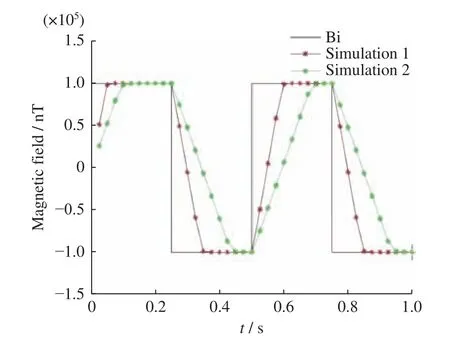

3.4 动态响应速度

动态响应速度是数字磁强计的一项重要特征,表征了数字磁强计对于外磁场快速变化时的跟踪能力。仿真测试方法为:设定系统的输入为幅值105nT,频率2 Hz 的方波变化磁场,计算数字磁强计输出响应速度。仿真条件列于表4,仿真结果如图14 所示。

表4 系统响应速度的仿真条件Table 4 Simulation conditions for system dynamic response speed

由仿真条件1 计算得到数字磁强计的动态响应速度为2×106nT·s–1,响应速度完全满足数字磁强计的测量需求。动态响应速度主要受系统的正向增益决定,提高系统正向增益,可以增加系统动态响应速度,如图14 和表4 所示。系统的动态响应速度与系统噪声关系密切。系统正向增益增大,噪声也会增大,因此系统设计中需要权衡噪声与响应速度的关系,合理设置正向增益。

图14 系统的动态响应速度仿真Fig.14 Simulation of dynamic response speed of the system

3.5 性能对比

最后对本文仿真设计的高精度1 bit 数字磁通门磁强计和前文提到的Sigma-Delta 数字磁强计性能进行对比,结果列于表5。

从表5 可以看出,与以往的Sigma-Delta 数字磁通门磁强计实测性能对比,本文仿真设计的1 bit 高精度数字磁通门磁强计在量程、噪声和非线性特性等性能上都有显著提升。虽然仿真模型中不存在电路噪声及环境影响等不利因素,但是分析结果中受噪声影响较小的量程、线性度、分辨率等参数均有了大幅度提升,表明本文的高精度1 bit 数字磁通门磁强计具 有一定的性能优势。

表5 Sigma-Delta 数字磁强计的性能对比Table 5 Performance comparison of Sigma-Delta digital magnetometers

4 结论

基于Sigma-Delta 调制器技术,设计并实现了一种高精度1 bit 数字磁通门磁强计仿真系统,测量分辨率可达到24 bits。在摒弃了传统的高精度ADC与DAC 情况下,仅需要1 位粗量化器(比较器),基于Sigma-Delta 环路调制器和1 bit DAC,可以在±105nT 量程范围下实现4.66 pT·Hz–1/2的系统磁场测量噪声。仿真结果表明:系统的最大非线性偏差仅为0.16 nT,有效带宽超过10 Hz,动态响应速度达到了2×106nT·s–1。与传统结构的磁通门磁强计相比较,有以下优势。

(1)本文设计的高精度数字磁通门磁强计采用了数字信号处理技术。相敏检波、环路调制及数字滤波等功能均可在FPGA 上设计实现,从而大幅度提高了系统集成度,增强空间探测用的磁强计系统可靠性。

(2)本文设计的高精度数字磁通门磁强计的磁场数据采样率与系统带宽均由数字信号处理模块确定,可以随磁场环境的改变而进行调整,从而有效提升了磁强计对不同空间磁场环境的适应性。

(3)采用1 bit 量化的技术途径,取代了传统设计中的高精度A/D 转换器,从而大幅度降低了对于高性能元器件的依赖,有利于提高磁强计载荷的空间环境适应性。

综上所述,基于Sigma-Delta 调制技术的1 bit数字磁通门磁强计具有量程范围宽、噪声低和分辨率高等特点,有利于提升载荷系统集成度,增强系统的空间环境适应性,在空间磁场探测领域具有广阔的应用前景。