用于硅像素探测器读出系统的流水线ADC 设计

2022-04-13黄芳芳杨苹高超嵩孙向明刘军

黄芳芳,杨苹,高超嵩,孙向明,刘军

(华中师范大学物理科学与技术学院夸克与轻子物理教育部重点实验室,湖北武汉 430079)

粒子物理实验是粒子物理学研究和发展的重要手段,其以高能粒子为基本研究对象,通过对粒子的径迹、能量、空间坐标等物理量的分析,为高能物理提供研究数据[1]。这就需要用精密的实验设备对这些物理量进行高精度测量[2]。低温高密核物质测量谱仪(CSR External-target Experiment,CEE)目前正处于设计研制阶段,研制完成后将是我国第一台运行于GeV 能区、自主研制的、基于国内核物理大科学装置HIRFL-CSR的大型核物理实验装置。在CEE 项目中,硅像素探测器主要用于测量入射粒子束流的位置和时间信息,为其他径迹探测器在重建末态粒子径迹时提供高精度的初始顶点。像素前端束流每秒击中率为10 MHz,通过调节像素芯片的响应阈值,控制每个击中事件有两个像素响应,则每秒就会有20 M的像素响应,由此产生的幅度信息需要快速、精准地被量化读出,而流水线结构是高速高精度ADC的最优选择。鉴于此,该文设计了一款13 bit、20 MS/s 流水线ADC,并从电路级分别介绍了各个核心模块的设计,最后给出的系统整体后仿真结果显示,该流水线ADC 有效位约为10.48,总功耗约为79 mW,满足项目需求。

1 系统结构

1.1 流水线ADC系统结构及工作原理

流水线ADC 拓扑图如图1 所示,整个模数转换器采用无前端采样(SHA-less)结构,主要由时钟产生电路、级转换电路、延时对准电路、数字矫正电路、基准电路以及偏置电路组成。其中,每一个子级转换电路都包含一个低精度子模数转换器和一个乘法数模单元(MDAC),MDAC 模块主要实现信号的采样、减法和余差放大功能,是流水线ADC的核心模块[3],最后一级为全并行ADC,不包括余差放大部分。

图1 流水线ADC拓扑图

流水线ADC的基本思想就是将整个模数转换器的精度分配到每一个流水线子级,每一级只对本级输入的模拟信号进行粗量化,最后将量化结果以特定的方式进行求和以达到细量化的目的。工作时,时钟模块会产生两相非交叠时钟P1、P2,确保流水线结构前一级采样,后一级保持。第一级首先对输入模拟信号进行处理,经过子ADC 后,输出本级数字量,然后子DAC 将本级输出数字量转化为模拟量并与输入模拟信号进行减法操作,将未被本级量化的模拟量经过余差放大后送入下一级继续进行量化,以此类推。由于每一级是串行连接,所以需要将每一级的数字输出送入延迟对准模块,最终经过数字矫正电路完成求和输出。对于整个流水线ADC 而言,MDAC的性能很大程度上决定了系统的整体性能,且该模块占据了大部分的系统功耗,因此,设计一个高性能的MDAC模块尤为重要[3]。

1.2 MDAC结构及工作原理

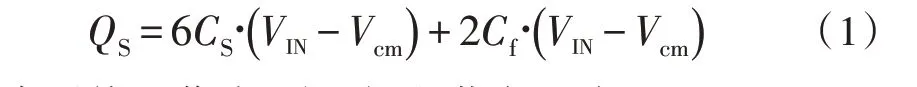

图2 所示为该设计所采用的MDAC 原理图,该模块由f1、k1和f2三相时钟交替控制工作,其中k1是f1的同相时钟,只是k1的下降沿比f1提前到来,以实现对信号的下级板采样[4],f1和f2是双相非交叠时钟,以实现开环采样和闭环放大功能。以2.5 bit 子级为例详细介绍MDAC 工作原理。根据冗余位数字矫正原理[5],本级所需要比较器的个数为6,级间放大倍数为4,当系统工作在f1相时,电荷方程为:

图2 MDAC原理图

当系统工作在f2相时,电荷方程为:

令CS=Cf,由电荷守恒定律可得:

同理可得:

其中,CAPP<0:5>和CAPN<0:5>是本级子DAC的模拟输出量,对应的逻辑高低分别是流水线ADC的量化区间边界值VREFP和VREFN。该设计采用3.3 V电源,对应的全差分量化区间边界值分别为2.15 V和1.15 V,模拟量输出由本级子ADC的数字输出决定,两差分输出端作差即可得到本级的余差模拟量。可以看出,级间放大倍数是由采样电容和反馈电容的比值决定的,k1的提前关断一定程度上会抵消f1控制开关的电荷注入效应,但是f2控制开关的电荷注入效应依然存在,由于Vcm是一个固定值,所以由于电荷注入而引起的误差可通过全差分结构相互抵消。

2 电路设计

2.1 增益增强型运算放大器

流水线ADC的采样速度取决于运算放大器的带宽,其采样精度又与运算放大器的直流增益有密切联系,若要使ADC 实现高速度和高精度,运算放大器就要同时满足高增益、高带宽的要求,因此设计者多采用增益提升技术,在不增加更多共源共栅器件的前提下通过提高共源共栅电路的输出电阻来达到提升增益的效果,通过小信号分析可以得出,此类电路[6]的等效输出电阻为:

根据运算放大器的直流增益公式可以得出,此时的直流增益为:

图3 所示是设计中用到的带有增益提升技术的全差分折叠共源共栅放大器,图中辅助运放的加入使得整个运算放大器输出电阻增加,最终提高直流增益。从图中可以看出,该运放输出节点的等效电阻和负载电容最大,因此该运放的主极点频率位于输出节点即M6管的漏极;运放的次级点则位于M3管的漏极或者M9管的漏极,一般来讲,为了获得同样的过驱动电压,PMOS 管的尺寸通常比NMOS 管的尺寸大,相应的管子节点电容也会大,因此运放的次级点频率位于M3的漏极。M12管与M11管并联作为共模反馈控制管,以达到稳定直流工作点的目的。

图3 全差分折叠共源共栅放大器

如图4 所示,为使辅助运放的引入不影响整个运放的速度以及稳定性,各个模块间应满足该频率关系,图中Atot是整个运放的增益曲线,Aadd和Aorig分别是辅助运放和主运放的增益曲线[7]。为了使辅助运放不影响整个运放的速度,须使辅助运放的主极点频率大于整个运放的主极点频率,即ω2>ω1;辅助运放的单位增益带宽处常出现零极点对[8-9],会使整个运放的建立特性变差,为避免上述问题,设计时应使辅助运放的单位增益带宽大于运放闭环使用时的主极点,且小于主运放的非主极点,即ω<ω4<ω6,最终以此为依据,分配辅助运放和主运放功耗。

图4 各运放幅频特性示意图

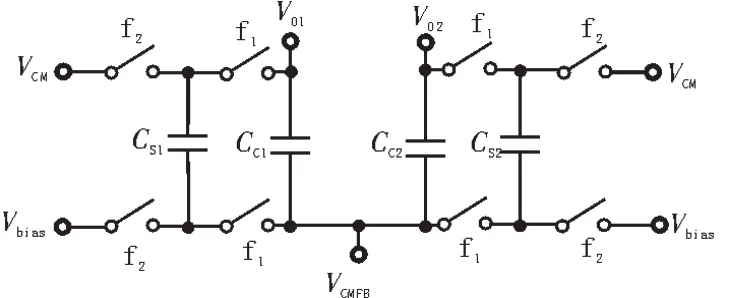

全差分运算放大器都需要共模反馈电路来稳定静态工作点,共模反馈电路决定了放大器的输出共模电平,稳定输出端信号,使得输出信号在设定的共模电平附近达到平衡[10]。共模反馈一般分为两类:连续时间共模反馈和开关电容共模反馈[11],相对于连续时间共模反馈,开关电容共模反馈没有输出摆幅的限制,且节省功耗,所以ADC的设计中通常使用开关电容共模反馈。图5 所示是该设计中开关电容共模反馈的原理。共模反馈模块一般包括3 类功能:①提取运放输出端共模电压;②与设定的共模电压比较;③输出反馈电压控制运放偏置从而调节输出共模。开关电容共模反馈工作在两相非交叠时钟f1和f2下,VCM是设定的共模电压值,Vbias是运放的尾电流管栅极控制电压,相当于图3 中的VBN。

图5 开关电容共模反馈电路

当f2闭合,f1断开时,电路的总电荷为:

当f1闭合、f2断开时,电路的总电荷为:

由电荷守恒原理Q1=Q2可得:

因为CS1=CS2,上述式子可以进一步简化为:

可以看出,最终的结果包含了上述3 部分功能。

2.2 动态比较器

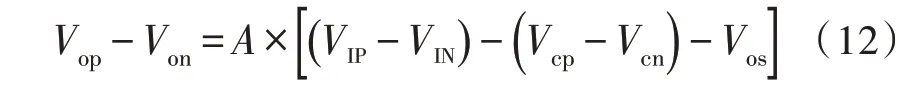

在流水线ADC 中,比较器是子ADC的核心模块,其速度和失调电压对ADC的性能有很大的影响。该设计采用预放大加锁存结构的比较器,用以减小比较器的失调电压、回踢噪声对ADC 性能的影响[12-13]。图6 所示为动态锁存比较器的原理框图,其主要工作在f1、f2、k2三相时钟下,其中k2和f2同相,k2比f2早一点闭合以建立置零状态。当f2为高、f1为低时,耦合电容两端的电压Vcp和Vcn之间的关系为:

图6 动态锁存比较器原理图

当f1为高,f2为低时,预放大的输出电压Vop和Von之间的关系为:

将上述两式合并可得:

由此可看出,比较器的失调电压被相减消除。

2.3 时钟产生电路

如前所述,流水线ADC 工作时需要双相非交叠时钟,这些时钟控制信号决定了系统采样保持的发生时刻,合理地分配双相时钟的有效时间,可以避免电容上存储的电荷发生泄漏以至信息丢失的情况发生。图7 为设计中用到的双相非交叠时钟的产生电路,其中全局时钟所产生的P1、P2是系统共用的,局部时钟每一级都有以实现前级采样后级保持的功能。其中CLK 是外部给入的20 MHz 时钟,P1、P2是全局时钟,f1、k1、f2、k2是局部时钟。k1比f1提前关断,以实现MDAC 模块的下级板采样技术,减小f1控制开关的电荷注入效应;k2比f2提前到来,以建立动态比较器的置零状态,f1高电平与f2高电平存在双相时钟非交叠的时间,在这段时间内,采样相和保持相均无效。

图7 双相非交叠时钟产生电路

3 版图设计与仿真验证

3.1 版图设计

采用GSMC 130 nm 工艺进行版图设计,在布局布线时需注意器件匹配、闩锁效应、天线效应以及电源分布等一系列影响ADC 性能的因素[14]。在版图设计过程中,系统中重要的模块如MDAC 中的全差分运放、动态比较器、电容阵列等,需要做好匹配,中间涉及到运放的部分,版图设计时需要布局为“蝴蝶状”,相应的偏置和共模反馈模块可放在版图空隙处;电流较大的信号线走线宽度需留有至少两倍的设计裕量;除此之外,模拟电源与数字电源需分开以减少耦合噪声;对于反相器或与门等逻辑电路,为防止闩锁效应的发生,需要用电源环将NMOS 管和PMOS 管隔开[15];模拟信号线与数字信号线尽量不交叉走线,如果特殊情况必须交叉,则要做屏蔽,分别用低层和高层走模拟信号线和数字信号线,用中间层作电源层进行屏蔽[16];时钟模块走线长度尽量一致,必要时需要设计时钟树来解决时钟驱动和延时的问题。

3.2 仿真验证

利用Cadence、Spectre、Matlab 等工具对流水线ADC 进行后仿真验证以及数据分析。系统工作电压为3.3 V,按照相干采样原理向系统送入正弦波信号,将系统输出的13 bit 数据送入理想DAC,将得到的离散模拟电压值用Matlab 进行有效位分析,如图8所示,该流水线ADC的ENOB 约为10.48 bits,SFDR为74.4 dB,SNDR 为64.9 dB,SNR 为65.1 dB,THD 为78.3 dB,系统总功耗约为79 mW,满足项目需求。

图8 流水线ADC有效位分析

4 结束语

该设计采用130 nm CMOS 商业标准工艺进行电路设计,后仿真结果表明,当工作电压为3.3 V,采样率为20 MHz 时,流水线ADC 后仿真有效位约为10.48,可以对前端硅像素探测器信噪比约为60 dB的模拟量输出进行高精度采样;单端输入信号动态范围为-1~1 V,系统总功耗约为79 mW,各项指标均达到预期且满足项目需求。