基于性能匹配的SoC 自适应电压调节系统

2022-04-13林胜楠梁利平

林胜楠,梁利平

(1.中国科学院 微电子研究所,北京 100029;2.中国科学院大学,北京 100049)

理论上电路的最佳运行电压-频率工作点取决于当前的运行环境,包括随着芯片的集成温度、压降、老化、工艺差等,然而,芯片在设计阶段就要考虑最坏情况下的运行条件,因此,设计人员往往在芯片设计阶段,为了保证芯片的正常运行,使得最坏情况下依然能够正常运行,留有较大的电压余量[1],造成功耗的浪费。自适应电压调节(Adaptive Voltage Scaling,AVS)技术可以显著压缩电压余量,被广泛研究。文献[2-5]介绍了基于Razor 结构的AVS 系统。文献[6]提出了一种基于可调复制电路(Tunable Replica Circuit,TRC)来监测电路温度以及老化,TRC 触发AVS 调节系统,电路运行时根据需要动态调整供电电压,以保持在最小电压下功能正常。文献[7]将可配置的延时链用于数字低压差线性稳压器(DLDO)设计中,减少在电压发生下过冲时产生的功能异常。文献[8-12]也评估了拟合延时链技术应用于自适应电压调节系统的可行性。

1 AVS系统设计

1.1 电压对延时和功耗的影响

大多数的应用程序并不是总要求电路的频率处于最高状态,随着处理器频率的降低,电源电压也可以降低。电压与功耗以及延时的关系如式(1)、(2)[13]。当电路的频率降低时,其电压也可以降低,动态功耗与频率以及电压的二次方成正比,所以当频率和电压都降低时,功耗以三次方的速度降低,但是随着频率的降低,完成一项任务的时间增加,所以完成一项任务所需的总能耗以二次方的速度降低。故可知降低电压对能耗的降低是非常有效的。

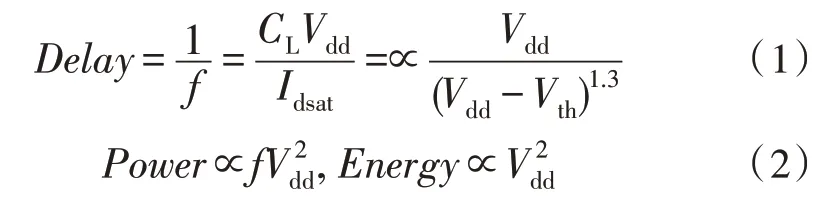

1.2 AVS系统整体结构

自适应动态电压调节系统主要包括延时链监测器、电源管理单元、数字稳压器、参考电压产生单元4 个部分,如图1 所示。数模转换器采用文献[14]中的分压偏置电路。延时链监测器可以监测当前数字负载的时序余量,输出2 bit的数字信号(KEEP、UPDN)指示当前电压是否是当前运行环境(包括温度、工艺、频率)下的最合适电压。使用DLDO 代替Buck 变换器或开关电容DC-DC 变换器,因为数字LDO 不需要芯片外电感而且可以提供对输出电压的精确控制,为了减小供电电压的电压波纹并提高响应速度,采用文献[15]中提出的结合推挽输出和电压峰值监测的数字LDO 来为数字负载供电,数字LDO 会将供电电压调节到参考电压。电源管理单元为纯数字控制逻辑,会根据延时链监测器的输出状态调整数控电压信号,将其输入到数模转换器来提供参考电压,参考电压每次变化一个步长或者不变,采用的电压调节步长为100 mV。这种全数字设计对数字电路友好,可以形成一整套基于EDA的低功耗设计流程。

图1 自适应电压调节系统结构图

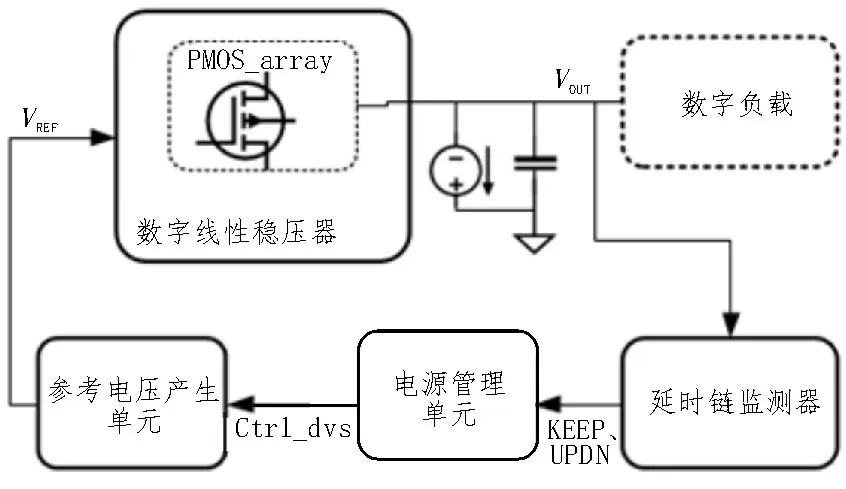

1.3 延时链监测器

延时链监测器结构如图2 所示,其是该自适应电压调节系统的核心模块,用于监测测试脉冲在延时链传递时的时序余量。监测器全部由数字标准单元构成,主要由延时链、4 个D 触发器、组合门逻辑以及控制逻辑电路构成。文献[16]中阐述了电压过冲时钟树的延时变化对时钟周期的影响,所以监测器的采样时钟均采用经过时钟延时链(与关键路径采样时钟延迟一致)的时钟clk_d,以此模拟时钟树对时序的影响。监测使能信号有效时,时钟二分频脉冲信号作为延时链的输入信号,经过延时链和D 触发器采样后与直接D 触发器采样的信号异或得到S0、S1,S0、S1 信号分别指示电压上升或下降,经控制单元输出KEEP、UPDN 信号,控制电源管理单元。

图2 延时链监测器结构图

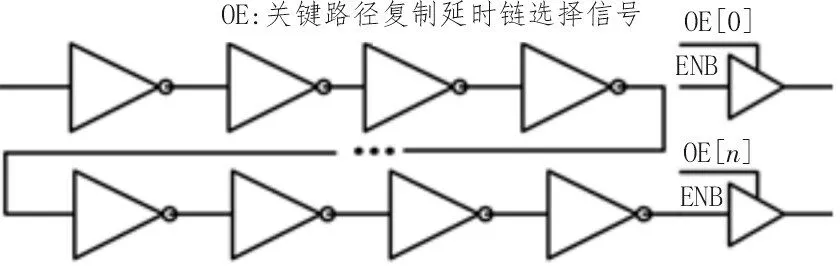

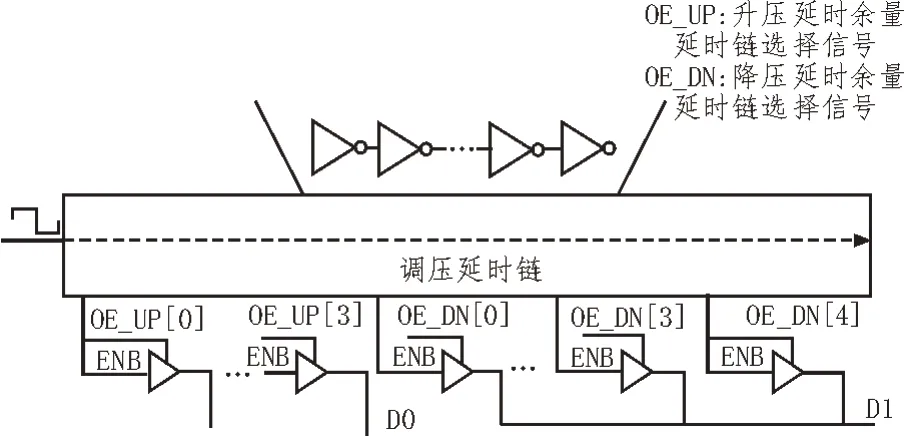

用于监测脉冲信号的延时链由可配置的关键路径复制延时链(Critical Path Replica,CPR)和调压余量延时链(Adjust Voltage Timing Margin,AVTM)构成。可调制关键路径复制延时链,如图3 所示,由反相器首尾相接构成,长度由数字负载的关键路径长度决定。调压余量延时链,如图4 所示,其也是由反相器首尾连接构成,升压余量监测信号D0和降压余量监测信号D1 是电压敏感的,基于不同电压下延时变化一个电压步长,关键路径延时变化差别很大,根据电路当前的工作电压选择不同的延时链长度。

图3 可调制关键路径复制电路图

图4 调压时序余量结构图

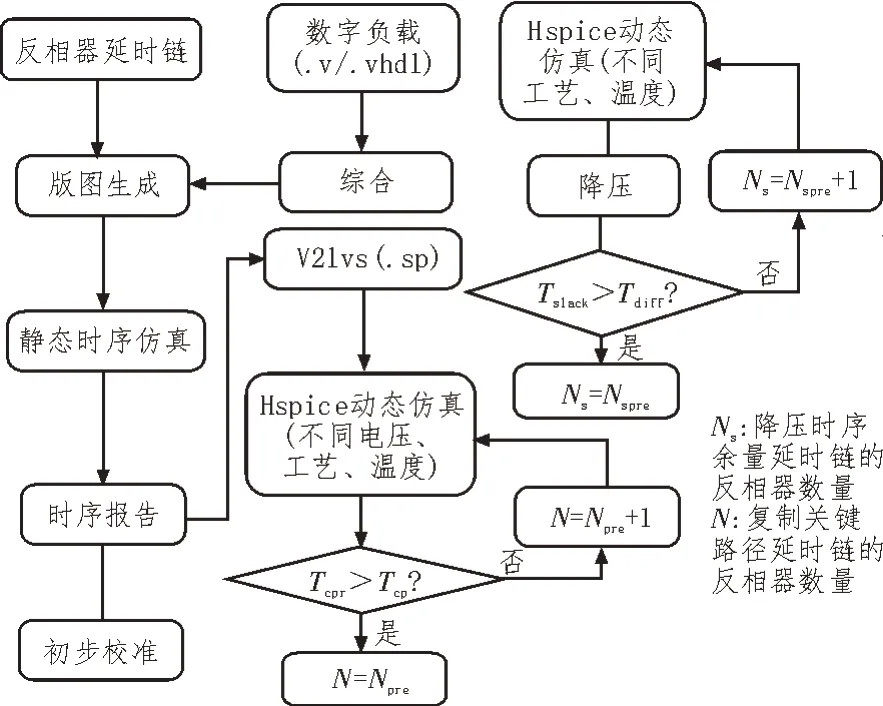

1.4 线下校准程序

自适应电压调节系统很重要的一个方面是如何精确关键路径监测器跟踪真实关键路径在温度、老化和电压过冲下的延时行为;另一个方面,也要考虑降低一个电压步长时需要在当前运行电压下留出的时序余量,从而在保证功能正常的情况下最大限度节省功耗。图5 显示了延时链监测器的线下校准程序,该程序考虑了复制关键路径对温度、电压以及工艺的灵敏度影响。

图5 线下校准程序图

采用静态时序仿真和动态时序仿真相结合的方式校准CPR。延时链监测器是面向特定数字负载的,所以该方法首先对数字负载进行静态时序分析,提取数字负载的关键路径(包括标准单元和RC参数)。与此同时,对可配置的反相器延时链生成物理版图,同样进行静态时序分析,预估匹配关键路径延时的反相器延时链的长度N。然后,依照复制关键路径延时链的延时比真实关键路径延时链延时大的原则,动态仿真关键路径在不同环境下的延时行为,最终确定关键路径复制反相器延时链的长度N。

动态仿真确定图4 中降压时序余量延时链的长度Ns。降压时序余量延时链长度的确定:基于不同的电压下,延时变化一个电压步长关键路径延时变化不同,电压从最低电压到最高电压,不同的工艺和温度条件下对提取的关键路径进行仿真扫描,特定电压下,在不同工艺、温度条件下,电压下降一个电压步长选取最大的延时增量∆t,以此为标准选取该电压下降低电压的余量延时链长度Ns,使其延时与∆t相近。相比于文献[6]中的校准程序,该校准程序不需要因为运行频率的不同重新校准监测器的bit 值,只面向数字负载的关键路径,所以大大缩短了校准时间。

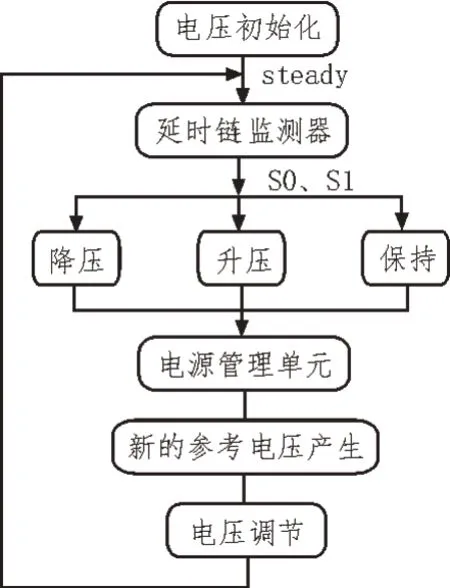

1.5 自适应电压调节过程

图6 是自适应电压调节的流程图,首先电压初始化到初始电位,电压稳定后,延时链监测器会根据当前电路运行频率产生一个二分频的脉冲,延时链监测器输出KEEP、UPDN 信号,电源管理单元根据延时链监测器的结果升压、降压或者保持当前电压,若产生新的参考电压,数字LDO 重新对低电压进行调节,此时为了节省功耗关闭延时链监测器,形成反馈回路。

图6 自适应电压调节流程图

2 仿真与结果分析

2.1 仿 真

该设计采用SMIC 55 nm 工艺,通过Hspice 进行了后仿真。根据电路运行环境和频率,自适应调节供电电压到适当水平,当KEEP=0,UPDN=1 时,升高电压;当KEEP=0,UPDN=0 时,降低电压;当KEEP=1时,保持当前电压不变。将电压调节到适应当前频率和运行环境的最小电压,从而明显节省功耗。

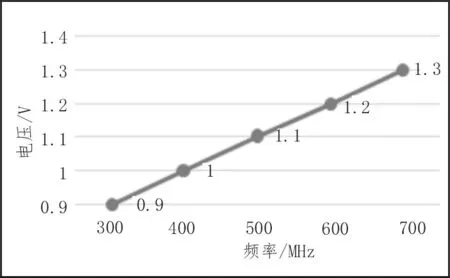

将自适应电压调节系统应用到滤波器上来检测其效果,之所以用滤波器,因为滤波器中的加法器、乘法器是数字电路中的常见单元,具有代表性。图7中是特定工艺角、温度条件下不同频率调节到的最合适电压,相比于固定电压1.4 V,频率从700 MHz下降到300 MHz,电压下降了约7%~36%,相应功耗节省了约14.9%~64.7%,如图8 所示。

图7 AVS电压和频率的关系

图8 AVS功耗与固定电压1.4 V功耗对比

2.2 结果分析

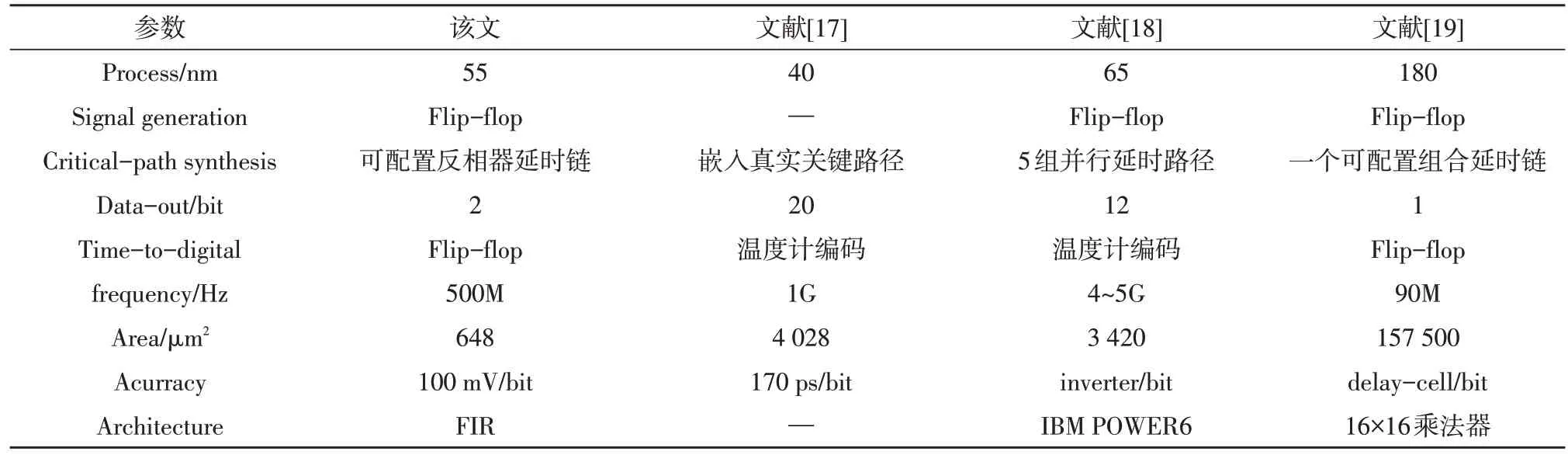

文中提出的延时链监测器能够实时监测电路频率以及PVT的变化,且监测精度完全适应于电压调节的需求,能够准确监测到降低一个电压步长所需的时序余量。表1 将文中延时链监测器与已发表文献进行了对比。可以看到,监测器的监测信号一般是时钟信号经过触发器产生,输出数字信号。文中关键路径拟合采用通过校准后的可配置反相器延时链,相比于嵌入真实关键路径的监测器,省去了选择关键路径这一复杂步骤,不会对负载电路产生影响,且结构简单、可移植性好。监测器的面积评估,包括时序转数字单元和数字控制模块的面积,该文监测器的面积明显小于其他文献。监测器灵敏度的比较是非常困难的,没有统一的标准,监测器的灵敏度与产生数字信号的延时链分辨率、不同的架构以及电路的运行环境(包括工艺、温度、运行频率)有很大的关系,这里列出的灵敏度根据每篇文献的测量结果给出,该文可以监测降低一个电压步长(100 mV,根据电压调节方案可以更小)的时序余量。

表1 该文延时链监测器与已发表文献对比

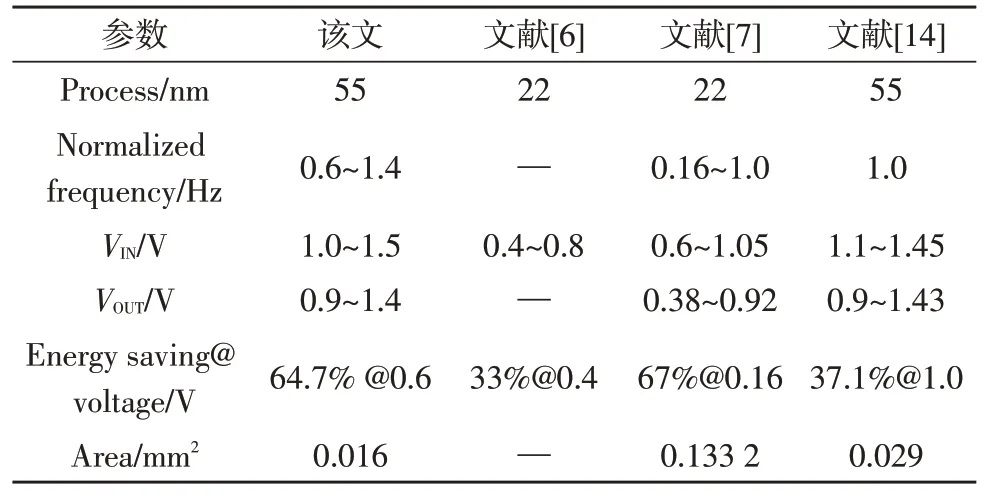

表2 将文中的AVS 系统和已发表文献进行了对比,表中列举文献的运行频率以及电压调节的范围,因为AVS 对功耗的节省跟电路频率以及当前工作电压有很大的关系,所以引入归一化频率,将功耗节省对应到当前运行频率上。该文的功耗节省是在工艺SS、125 ℃情况下进行评估的,在归一化频率为0.6时,相比于固定电压功耗节省64.71%。该文实现的AVS 系统能够适用于较大频率范围内的电压调整,实现功耗优化,且面积较小,能够达到一个较有竞争力的水平。

表2 该文AVS系统与已发表文献对比

3 结论

文中提出了一种基于线上实时监测和线下校准相结合的自适应动态电压调节系统,能够根据电路运行频率和运行环境对供电电压做出调整。该文提出的延时链监测器结构更加简单,面积小,将其结合数字LDO 实现了自适应电压调节,适用于宽频率以及PVT 条件的监测,AVS 系统采用SMIC 55 nm CMOS 工艺,在125 ℃、SS 工艺角下,频率从700 MHz下降到300 MHz时,相比于固定1.4 V 电压,AVS 功耗节省14.9%~64.7%,能够达到一个较有竞争力的水平。