基于SRAM型FPGA的多源自主重构方法

2022-04-07李璐芳周双喜黑花阁喻琪超林长青孙胜利

李璐芳, 周双喜, 黑花阁, 喻琪超,林长青, 孙胜利,*

(1. 中国科学院上海技术物理研究所, 上海 200083; 2. 中国科学院智能红外感知重点实验室,上海 200083; 3. 中国科学院大学, 北京 100049)

0 引 言

红外遥感相机在轨运行时,需要长时间对目标进行观测成像,国内外对航天故障的统计显示:约有40%的故障源自太空辐射,太空中的单粒子翻转(single event upset, SEU)将对红外遥感相机运行状态、图像质量产生影响。在红外遥感相机中应用最为广泛的是Xilinx公司Virtex系列静态随机存储器(static random-access memory,SRAM)型现场可编程逻辑门阵列(field programmable gate array, FPGA),SRAM工艺的FPGA受空间高能粒子影响较大,内部配置存储器的逻辑状态常常受单粒子的影响,可能会影响整个系统的正常工作。航天高可靠性应用的设计必须要考虑单粒子效应对FPGA配置存储器的影响。配置存储器的打翻可能会导致器件的功能和性能发生变化,SRAM型FPGA除了配置存储器易受到单粒子效应的影响外,其内部包含的锁存器、触发器、块RAM存储等用户可用资源也易受单粒子效应的影响,这些内部资源受单粒子效应影响可能导致器件应用的功能发生中断。由于FPGA所实现功能取决于存储在器件中数百万个配置存储单元中的数据,所以配置存储器阵列发生SEU可能会对预期的功能产生不利影响。

虽然降低SEU影响的措施有很多种,比如可以通过三模冗余(triple modular redundancy, TMR)对内部关键寄存器进行三模冗余设计,或者使用多片FPGA进行备份,但是必须通过刷新纠正SEU所导致的错误,否则错误数会越来越多。虽然TMR能够提高FPGA可靠性,但是也会降低经过布局布线后的最大时钟速度,增加FPGA的资源使用量,增大芯片功耗。如果FPGA逻辑设计本身就很复杂,则TMR设计后所带来的资源和功耗往往是系统设计所无法容忍的。因此在具体设计时,可针对部分关键逻辑和电路进行TMR加固设计。国内外多个研究机构对该类型FPGA进行了单粒子翻转特性的试验,其中某型号卫星在轨数据表明,在未做抗单粒子加固措施的条件下,在轨测试期间(共73天),400万门FPGA共发生496次翻转事件,60万门FPGA共发生74次翻转事件,虽然小门数FPGA翻转概率小,但是研究数据表明用多片小门数FPGA代替一片大门数FPGA的方法并不能降低SEU次数,因此在轨应用时需要采取一定的抗单粒子加固措施。

SRAM型FPGA器件在实时回读(功能不中断的回读)时,SRAM cell易受噪声影响,导致存储值翻转,甚至导致系统功能错误,航天应用时,需在保证系统功能不中断的前提下,进行抗SEU的加固。因此,不推荐在航天应用时,通过持续的回读配置存储值,判断是否发生SEU,依据回读比较结果再进行SEU系统加固。SRAM cell在写操作时,不易受到噪声影响,所以推荐在航天应用时,系统功能不中断的情况下,通过对配置存储器进行刷新的方式,来恢复发生SEU翻转的SRAM cell存储值,消除SRAM cell发生SEU后的累计错误位。经研究数据表明,SRAM 型FPGA 对SEU敏感,同时存在单粒子功能中断,对于红外遥感相机图像信息处理电路等关键部位,应慎用SRAM 型FPGA,若使用则需要相应的加固技术。通过重配置的方法可以有效地减缓SEU与单粒子功能中断(single event function interrupt, SEFI)的影响,所以动态重配置是防护SRAM 型FPGA SEU与SEFI的有效手段。

国内比较常用的加固技术采用TMR+scrubbing+reload的容错系统,文献[5]使用配置PROM作为外部配置存储器,使用300万门大容量Virtex-2系列作为实现应用设计的FPGA,用反熔丝FPGA对Virtex-2系列FPGA的配置数据进行毫秒级周期刷新。文献[19]综述了几种FPGA抗SEU的设计方法,FPGA的TMR设计、重配置、自动刷新技术、回读和刷新技术以及局部动态可重构技术等,通过采用以上一种或者多种容错设计方法,可以增强FPGA对于空间SEU的防护能力,有利于提高红外遥感相机在轨工作的可靠性。文献[20]对常规采用的配置刷新方式、回读刷新和定时刷新进行了对比,得出结论:定时刷新方法简单可靠,并且占用存储空间小。文献[21]提出了FPGA自主刷新+三模冗余的解决方案,在保证FPGA抗单粒子性能的基础上提高了系统的资源利用率。文献[22]提出了FPGA可重构技术的分类以及动态可重构技术的原理,并在此基础之上选取Virtex-4系列FPGA 给出一种动态重构的应用以及具体实现。

近几年,国内772所和复旦微电子等为了应对SRAM型FPGA在轨SEU问题,推出了针对Xilinx公司Virtex系列以及国产相应FPGA的刷新芯片,可以实现上电配置、定时刷新、回读刷新、在轨重构功能,但该刷新芯片仅支持特定型号的存储器件和Xilinx公司一些主流的FPGA。

1 基于SRAM型FPGA多源自主重构的架构

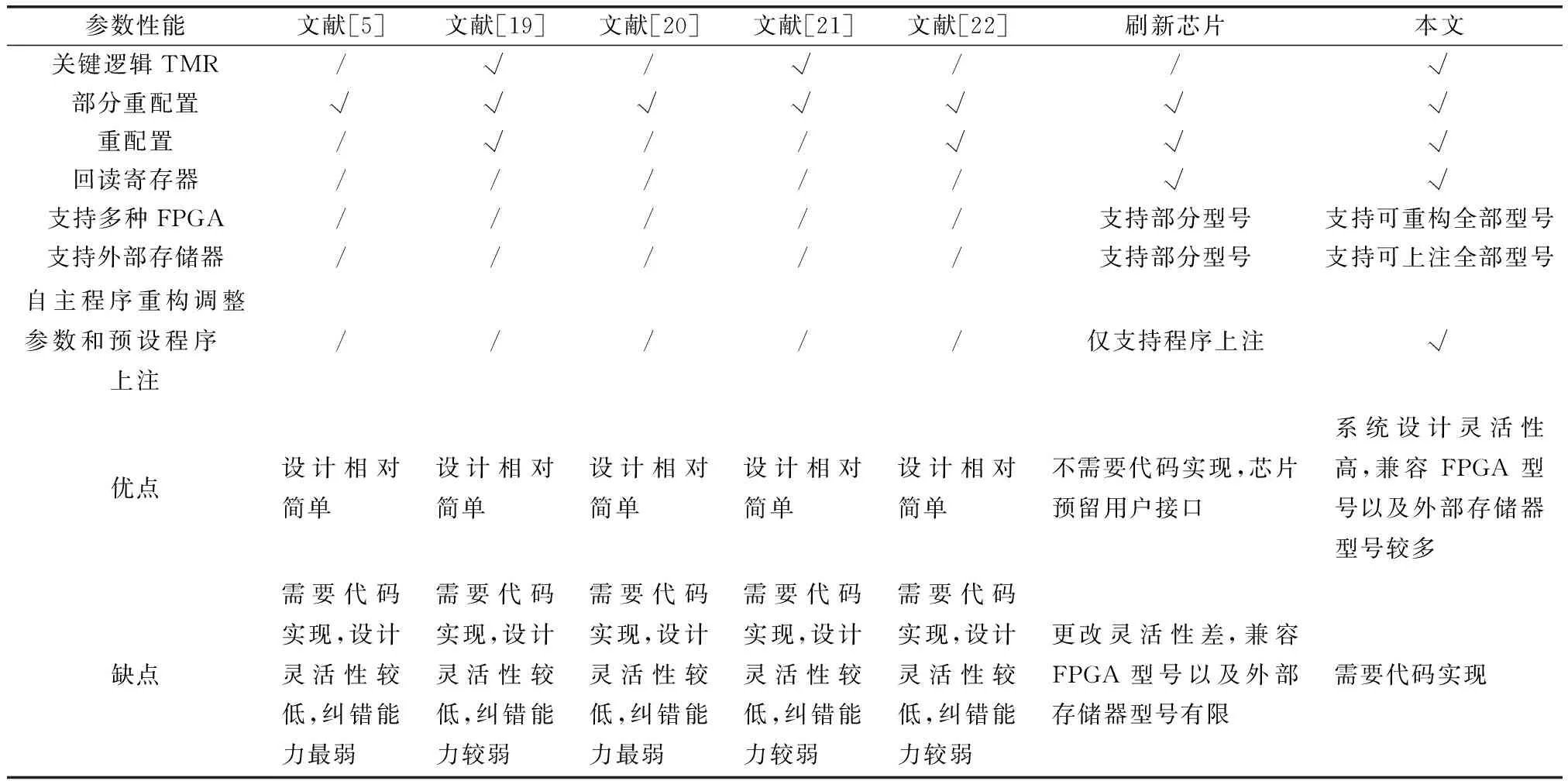

综上,对各种解决SEU的方法进行对比,如表1所示,并得出以下结论。

对于以上各种解决SEU的方法,总结出以下几点:

(1) 抗SEU的加固技术主要采取如表1中的一种或者几种组合措施。因此,只有根据实际需求情况,各种措施共同配合,才能达到较好的抗SEU效果。

(2) 由于红外遥感相机中不同规模探测器对图像信息获取以及处理能力不同,因此对FPGA的资源大小要求也不同。如果反熔丝FPGA的核心算法不兼容SRAM FPGA型号,那么每当使用不同资源类型大小的SRAM FPGA 都需要对反熔丝FPGA核心算法进行升级。

(3) 红外遥感相机在轨运行时由于寿命、故障等原因导致探测器性能衰减,造成图像性能参数发生变化不满足使用要求时,需要在轨进行调整,使图像性能满足使用要求。

(4) 国产刷新芯片可满足以上基本功能,但只支持特定型号的NOR FLASH或者SPI FLASH等存储器件,选择性有限。

(5) 国产刷新芯片仅支持Xilinx公司主流FPGA以及国产相应的FPGA,仍不能覆盖所有相关FPGA型号的需求。

表1 方案对比Table 1 Option comparison

针对以上问题,结合实际工程应用需求,设计了一种基于SRAM型FPGA的多源自主刷新重构方法,不仅可以实时监测SRAM型FPGA的健康状况,在轨回读SRAM型FPGA工作寄存器的状态,还可以对SRAM型FPGA进行全部重配置和时间可设置的动态部分配置,并且对SRAM型FPGA内的关键寄存器进行TMR设计。除此之外还有以下优点:

(1) 可根据器件IDCODE自主识别所用SRAM型FPGA的型号。针对红外遥感相机中不同规模的探测器对图像信息获取以及处理要求不同,对FPGA资源需求也不相同,如果采取一片反熔丝FPGA管理几片不同类型的SRAM型FPGA,不仅增加了硬件资源,还增加了设计难度。因此为了更好提高本架构的系统兼容性,本设计可以对多种型号的不同资源类型大小SRAM型FPGA(比如Virtex-2/4/5/7全系列等)的IDCODE进行自主识别并对其进行重构和刷新,提高系统沿用性。

(2) 可选择多源外部程序存储器进行定时刷新以及重构,如果采用的多源存储器都为PROM,那么程序烧写完成后,不能根据在轨使用需求对SRAM型FPGA内的程序进行上注更新,因此选择NOR FLASH对SRAM型FPGA内的程序进行上注存储,根据使用需求对上注的程序选择自主重构。当NOR FLASH内上注程序不满足使用需求时,又可切回PROM对SRAM型FPGA内的程序进行更新,并且兼容各种可上注NOR FLASH型号。因此该项功能可增加系统灵活性、提高系统可靠性。

(3) 通过在轨监测红外遥感相机图像性能参数,当发生变化不满足使用需求时,对上注程序进行自主重构,使图像性能参数满足使用需求。

以反熔丝FPGA为核心处理器件,系统框图如图1所示,有接口关系的器件有PROM、flash、NOR FLASH以及SRAM型FPGA。

反熔丝FPGA左侧,与SRAM型FPGA的SelectMAP接口对程序数据进行读写操作,SelectMAP 接口是一个8位的双向数据端口,是定时刷新、配置和回读的数据接口,可以通过它对Virtex FPGA进行配置,也可以通过它读回配置数据,是Virtex FPGA 最快的配置方式。与SRAM型FPGA的控制接口控制SRAM型FPGA进行不同程序源存储器的定时刷新和重配置,以及控制切换选择程序刷新重配置通道和上注程序通道。与SRAM型FPGA的上注/回读程序通道接口主要完成在控制接口切换为上注程序通道时,对NOR FLASH进行程序上注和回读对比。

反熔丝FPGA右侧,与PROM、flash和NOR FLASH接口主要为刷新和重配置数据通道,还有上注程序数据以及控制线选择通道。

图1 系统框图Fig.1 System architecture

2 基于SRAM型FPGA多源自主重构的算法流程

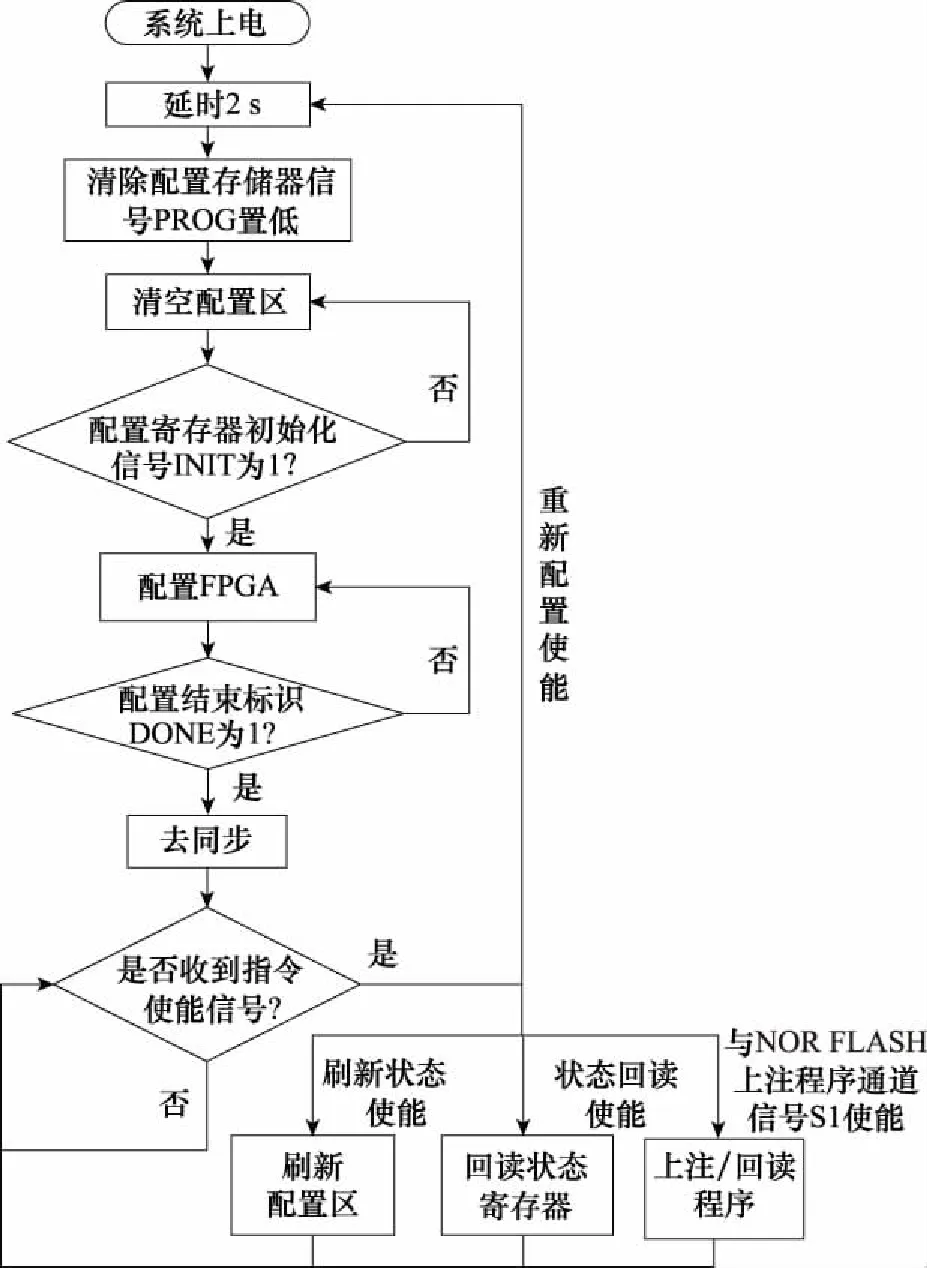

反熔丝型FPGA需要完成上电配置、全部重配置、定时动态刷新(部分配置)控制以及配合SRAM型FPGA完成在轨上注程序的管理,整体算法流程如图2所示。

图2 整体算法流程图Fig.2 Overall algorithm flow chart

(1) 在系统上电阶段从外部存储器加载SRAM型FPGA的配置数据或者发送指令全部重配置SRAM型FPGA配置区,实现系统上电后SRAM型FPGA正常运行和程序重配置。

(2) 在刷新信号有效后,对SRAM型FPGA的配置区进行周期性的刷新,实现在轨定时刷新。

(3) 当SRAM型FPGA进行在轨上注预设程序时,反熔丝FPGA与NOR FLASH存储器的数据通道将自主切换至读/写通道,对参数或者程序进行读/写工作,实现在轨程序上注以及回读。当监测到相关图像性能参数发生变化时,可进行自主程序重构使图像性能满足系统要求。

(4) 自主识别SRAM型FPGA的IDCODE,实现了系统兼容Xilinx Virtex全系列(Virtex-2,Virtex-4,Virtex-5,Virtex-7系列)。

(5) 多源选择外部存储器,实现了从PROM,flash,NOR FLASH任意源切换的功能。

(6) 在轨回读SRAM型FPGA状态寄存器状态,对SRAM型FPGA的健康情况进行实时监控。

2.1 上电配置和全部重配置

在系统上电阶段从外部程序存储器加载SRAM型FPGA的配置数据,实现SRAM型FPGA的正常运行,与上电配置的不同之处是重配置需要发送指令,反熔丝FPGA对接收到的重配置指令解析后,对SRAM型FPGA进行全部重配置;上电配置是接收到外部复位信号后,先进行上电复位,然后进行全部配置,具体配置流程如下所示:

(1) 上电复位结束后,将SRAM型FPGA的PROG信号置低至少300 ns后置高,清空FPGA配置存储器。

(2)检测SRAM型FPGA的配置寄存器初始化信号(initialization, INIT),若其值为高,将SelectMAP接口的片选信号(ChipSelect, CS)、读写信号(ReadWrite, RDWR)置低,同时将程序存储器PROM的使能信号(ChipEnable, CE)置低,输出使能端(OutputEnable, OE)置高,使得数据从外部存储器到SRAM型FPGA的数据通道开通。若INIT为低,则持续检查INIT的值,直到其值为高,进行配置。若此时收到全部重配置指令,则进行全部重配置。

(3) 检测SRAM型FPGA的输出配置结束信号DONE,若DONE值为高,说明配置成功,然后将CS置高使得数据总线呈高阻态等待后续操作;若DONE值为低,则对DONE值持续检查,直到其值为高。

2.2 周期定时自动刷新

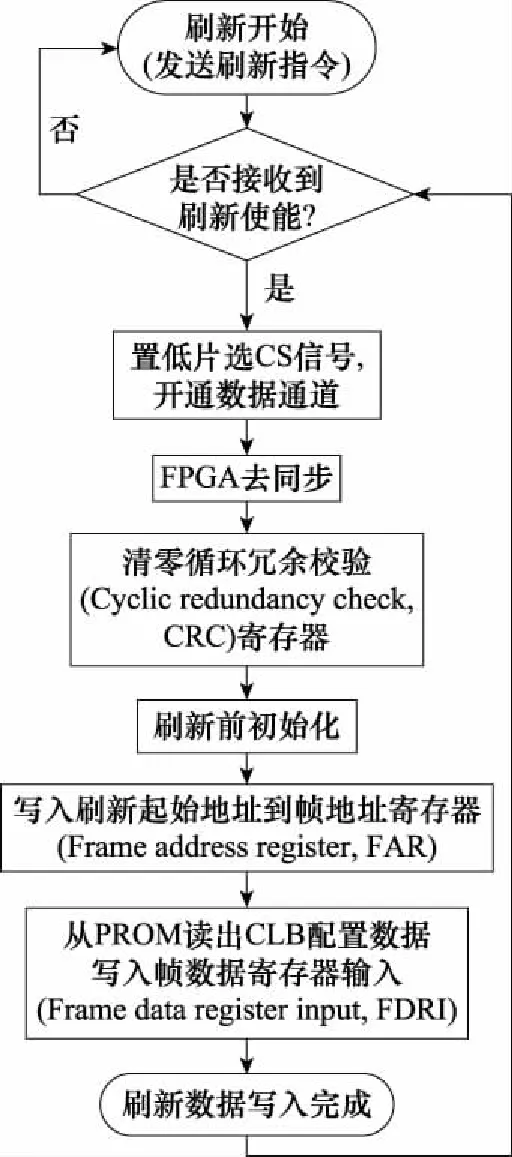

FPGA应该要被刷新以防止配置存储器中的SEU错误累加而影响系统的正常工作。配置帧是配置数据在Virtex FPGA配置存储器中可以读写的最小单位,多组配置帧组成一个配置帧列,配置帧列分为可配置逻辑块(configurable logic block, CLB)帧列、输入/输出缓冲器(input/output buffer, IOB)帧列、全局时钟(global clock, GCLK)帧列、数字信号处理(digital signal processing, DSP)帧列、块随机存储器(block random access memory, BRAM)内连帧列、BRAM 帧列。一个完整的配置文件就是由所有配置位置的帧信息和一些必要的首尾控制字组成。在不影响当前程序正常运行条件下,其中CLB 帧列、IOB 帧列、GCLK 帧列、DSP 帧列、BRAM 内连帧列为可在线重配置帧(在线重配置不影响FPGA 正常功能),BRAM 帧列为不可在线重配置帧(在线重配置会造成FPGA RAM 区数据错误)。FPGA自动刷新是指周期性地对配置信息进行刷新,无论是否发生SEU,均对FPGA配置区进行刷新操作。为了减少刷新中断,本设计采用基于帧的刷新算法,这种算法把刷新最小单位限制在一帧范围内,根据FPGA刷新配置区的寄存器命令序列对FPGA配置区进行刷新,并且可以根据实际需求对刷新周期进行参数设置(2 s,10 s,60 s等)。具体算法如下所示,定时刷新过程流程如图3所示。

图3 定时刷新过程流程图Fig.3 Timing refresh flow chart

(1) 定时刷新使能信号为高时启动周期性刷新。接着置低SRAM型FPGA的片选CS信号,开通数据通道。

(2) 根据FPGA刷新配置区的寄存器命令序列对SRAM型FPGA的相关寄存器进行设置,完成刷新起始地址FAR寄存器的设置。

(3) 根据FPGA刷新配置区的寄存器命令序列完成对写FDRI寄存器指令的设置后,开始写配置数据量,指示刷新的第一步是从地址0开始写入数量等同CLB帧块的配置数据;在设置完后的下一个时钟,开始刷新从PROM来的CLB帧块的第一帧配置数据。

(4) 最后向数据总线写入一帧空闲字节以配合流水逻辑,将最后一帧有效配置数据写入FPGA内部配置寄存器,完成对SRAM型FPGA内部配置寄存器的刷新过程。

(5) 状态机回转,再次检测刷新使能信号进行周期性刷新。

2.3 上注数据读写通道切换以及自主重构

在轨可通过卫星总线通信指令对NOR FLASH存储器进行程序上注,并根据对相机图像性能参数的监测情况,对程序进行自主重构。本文以相机非均匀性校正后的残余非均匀性为监控参数,通过上注预设了2套非均匀性算法程序,分别为定标法和基于场景法校正算法。根据非均匀性的变化情况,在轨默认选择定标法进行自主重构,当定标法无法满足系统要求时,自主切换至另外一套基于场景法程序进行重构,使红外遥感相机的残余非均匀性符合系统使用要求。当红外遥感相机在轨运行监测到系统性能参数发生变化需要上注程序时,切换至NOR FLASH与反熔丝FPGA,反熔丝FPGA与SRAM型FPGA的8位数据通道以及NOR FLASH的控制线和地址线等,实现反熔丝FPGA作为NOR FLASH上注程序到SRAM型FPGA的通路选择开关,切换至上注数据读写模式时,要确保停止刷新配置区。利用NOR FLASH存储空间大的优势,可以存储多套参数或程序,并且上注完成后通过回读与实际写入的程序进行对比,确保上注程序的有效性。按照上述流程可对NOR FLASH写入多套参数和程序,并且可以对NOR FLASH内的参数和程序进行擦除重写,成功实现了既可以在轨多套参数和程序上注、又可以对多套上注程序进行定时刷新以及重配置,增加了SRAM型FPGA在轨运行的可靠性,上注数据读写通道切换流程图如图4所示。具体算法如下所示:

(1) 准备开始上注程序,反熔丝FPGA收到来自SRAM型FPGA的SRAM型FPGA与NOR FLASH的上注程序通道信号S1、NOR FLASH的读/写程序通道信号S2和停止刷新不回读标志位同时有效,数据和控制主动权在SRAM型FPGA,此时SRAM型FPGA对NOR FLASH执行写操作。

(2) 当SRAM型FPGA与NOR FLASH的上注程序通道信号S1有效停止刷新不回读标志位有效时,数据和控制主动权在SRAM型FPGA,此时SRAM型FPGA对NOR FLASH执行读操作。

(3) 完成对NOR FLASH的读写操作后,也能当系统性能指标无法满足系统要求时,自主切换至另外一套程序进行重构,满足使用要求。也可发送指令从NOR FLASH定时刷新和重配置。

图4 上注数据读写通道切换流程图Fig.4 Switching the inject data between read and write

2.4 自主识别SRAM型FPGA

自主识别SRAM型FPGA的IDCODE,实现了系统兼容Xilinx Virtex系列FPGA。每一款FPGA都有其固定的ID编码,该编码是一个固定的由供应商来制定的值,用来鉴定识别该FPGA的制造商和型号。ID寄存器提供了一个很方便的方法来识别进行测试或者编程的FPGA的ID编码,通过配置寄存器内发送的IDCODE指令,可以将所用的FPGA的ID编码读出来进行检查。通过对不同FPGA的ID进行识别,能够检测并判断目前正在运行的FPGA属于哪种系列。FPGA的ID可以通过Virtex-2/Virtex-4/Virtex-5/Virtex-7等系列的IDCODE编码表进行查找。

具体算法流程如下所示:

(1) 在执行重配置指令时,SRAM型FPGA进行配置初始化,在器件进行同步化后,在配置数据下载前必须先通过器件自身的ID检查,FPGA会解同步,然后进行配置数据的下载。

(2) 在执行定时刷新指令时,首先回读SRAM型FPGA的IDCODE,然后根据回读的IDCODE,对不同类型的SRAM型FPGA的刷新配置区刷新序列代码进行调用,实现了对不同系列SRAM型FPGA刷新代码的兼容。

2.5 多源外部存储器切换

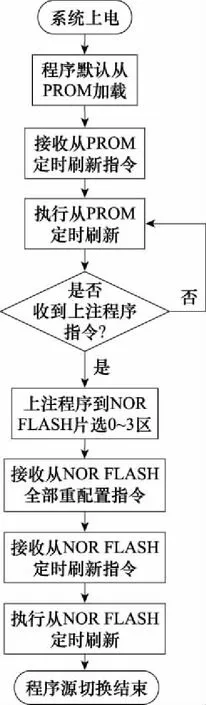

SRAM型FPGA可以从不同外部程序存储器芯片中(PROM、flash和NOR FLASH)进行程序动态定时刷新以及全部重构。可以通过指令对定时刷新以及程序重构源进行选择,提高了SRAM型FPGA在轨使用的可靠性,多源外部存储器切换流程如图5所示。

图5 多源外部存储器切换流程Fig.5 Switch of multi-source external memory

多源选择外部存储器,实现了PROM,flash以及NOR FLASH内多套程序任意源切换的功能。系统上电运行正常后,刷新/重配置数据通道(SelectMAP接口)优先级最高,此时可以发送从PROM刷新/重载,从flash刷新/重载以及从NOR FLASH刷新/重载指令,通过指令解析单元,分别对相应的指令进行解析并且对相应的程序存储器执行对应指令的操作。只有当SRAM型FPGA与NOR FLASH的上注程序通道信号S1有效时,把数据通道切换至NOR FLASH上注程序读写通道。

2.6 在轨回读FPGA工作状态

为了更好地实现SRAM型FPGA在轨工作的可靠性,可以在轨通过selectMAP接口回读SRAM型FPGA状态寄存器的关键状态信息,状态寄存器内的信息发生变化,可以判断FPGA在轨工作出现SEU,那么此时FPGA应该要被完全重配置。因此能有效判断SRAM型FPGA在轨工作状态,是否受单粒子等空间环境影响,能及时有效地提高其在轨运行的可靠性。

以Virtex-4 FPGA为例,其状态寄存器共32 bits,如果bit5或者bit6返回“0”会有三态输出或者不能对器件进行同步更新;如果bit7翻转,FPGA会被打翻,丧失功能。因此通过回读状态寄存器内的信息,判断器件有无翻转,根据需要进行重新配置或者定时刷新,以减轻SEU造成的影响,根据Virtex-4 FPGA状态寄存器检测命令,实现了对FPGA状态寄存器的读取操作。

3 系统验证

系统中的SRAM型FPGA以Xilinx公司 Virtex-4系列FPGA为例,反熔丝FPGA以Actel公司A54SX72A为例,验证周期性定时刷新、程序上注、数据源切换以及系统功能。

3.1 定时刷新验证

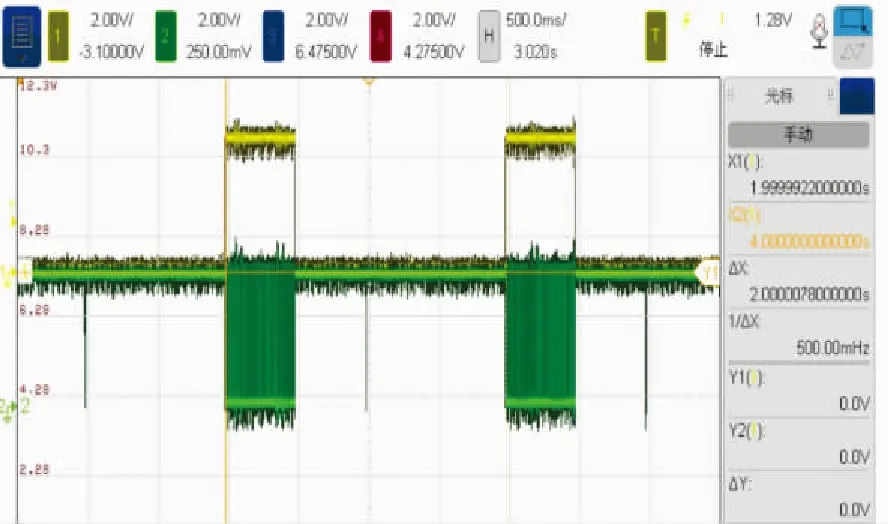

首先程序中设置刷新时间间隔为2 s,系统运行时,通过示波器观察Virtex-4 FPGA的写信号CS为“0”,此时开通数据通道,由于配置时钟CCLK为4 MHz,2 s定时刷新部分配置数据有大约1 996 000个数据(8 bit并行数据),因此2 s定时刷新的部分配置数据长度约为499 000 μs,约499 ms,如图6所示。实测刷新时间间隔为2 s,如图7所示。

图6 刷新数据时间 Fig.6 Data refresh time

图7 刷新时间间隔Fig.7 Refresh interval

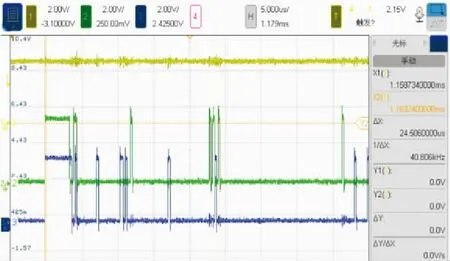

经过查找.bit或者.rbt文件,找出第一个同步字FF FF FF FF在第一行配置数据,到最后一个配置数据头共有98个数(8 bit并行数据),配置时钟CCLK为4 MHz,因此到后一个配置数据头的时间为98×0.25 μs=24.5 μs。通过观察示波器数据位的输出,从配置数据头的第一个FF到最后一个数据间隔时间为24.5 μs,如图8所示。

图8 配置数据帧头时间Fig.8 Time of the header of the configure data

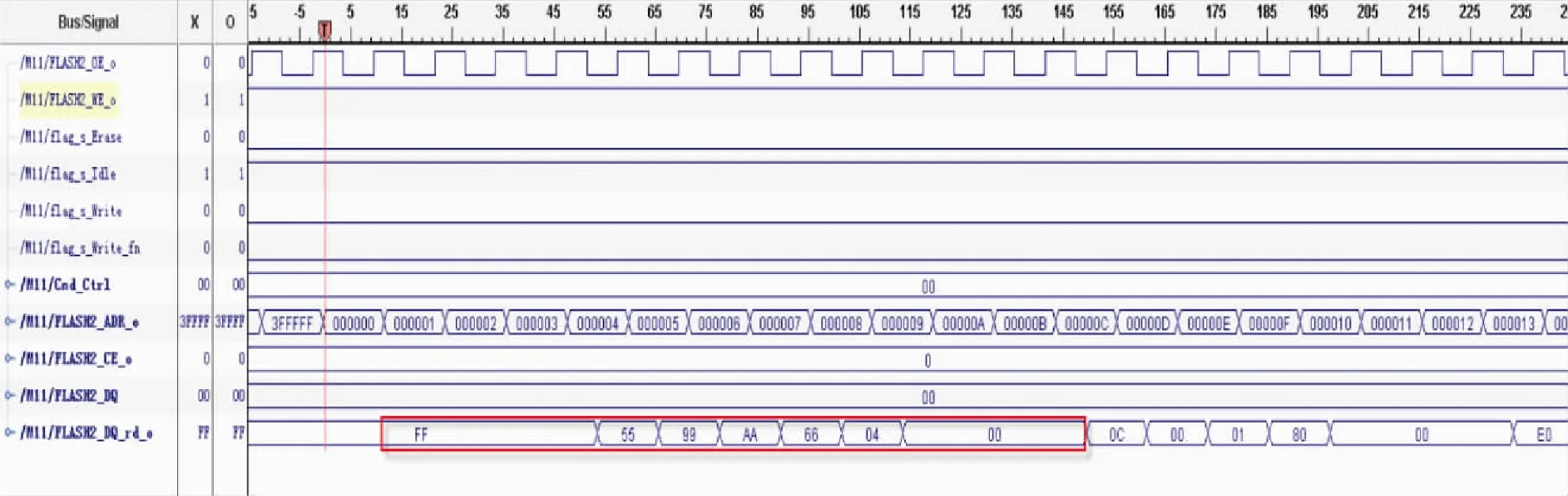

3.2 程序上注验证

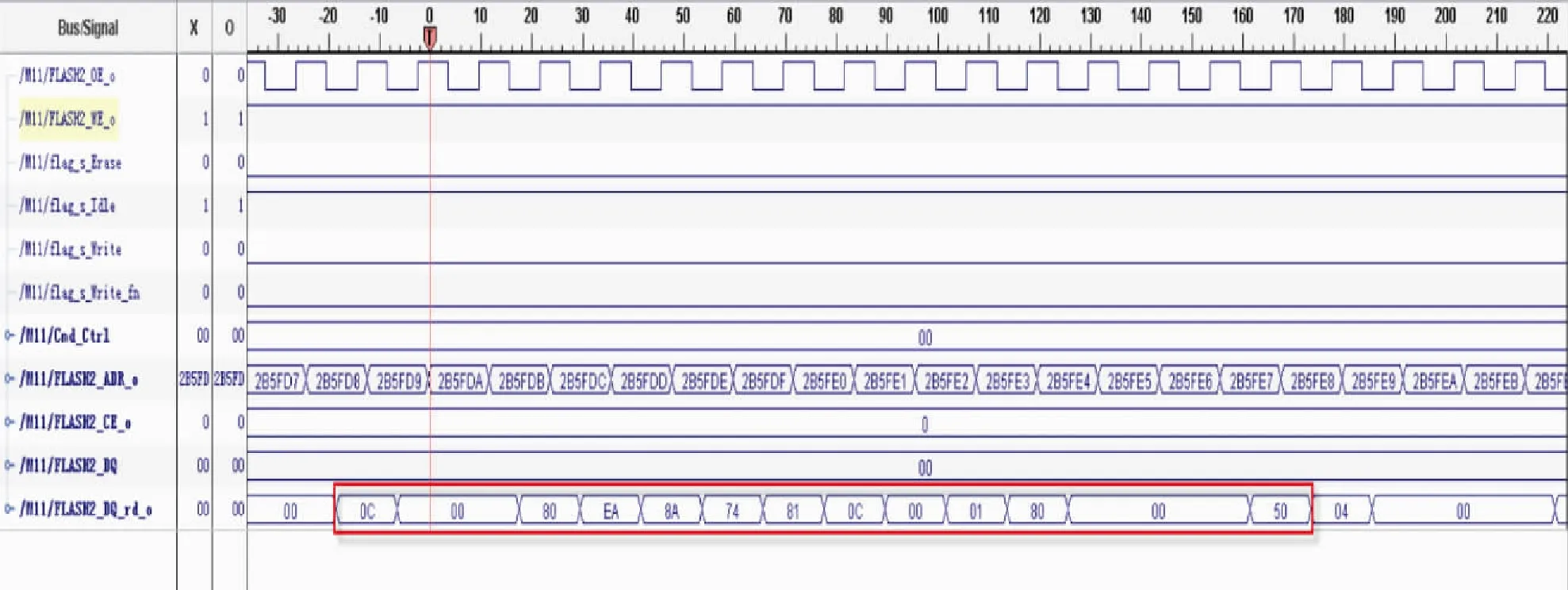

上注程序后,通过Xinlinx公司的集成软件环境(integrated software environment, ISE)中的ChipScope工具插核回读数据是否上注成功。从ChipScope工具插核回读第一包与实际注数包比对,上注数据正确,如图9所示。

从ChipScope插核回读最后一包上注数据与实际注数包比对,上注数据正确,如图10所示。

3.3 数据源切换验证

对不同数据源用指令进行切换,数据源切换后,通过示波器观察刷新数据时间约为499 ms,刷新时间间隔为2 s,配置帧头时间为24.5 μs,如图6~图8所示,每次通过刷新指令切换不同数据源均符合以上要求,说明对不同数据源用指令切换操作成功。

图9 回读第一包上注数据示意图Fig.9 Readback of the first injected data

图10 回读最后一包注数包Fig.10 Readback of the last injected data

3.4 系统功能验证

该方法已在轨应用于某型号红外遥感相机,并对关键测控信号进行TMR。该型号红外遥感相机图像用SRAM型FPGA采集红外图像时发现闪点(高亮度孤立点)增加的现象。经过分析是由于SRAM型FPGA中控制图像排列时序的寄存器单元受空间环境中单粒子影响发生了翻转,导致时序不匹配,数据读写的建立时间不满足要求造成图像散点增加,最终导致SRAM型FPGA的SEU故障发生。经过在轨连续监测,该现象的SEU故障发生概率约为1.5年/次,没有进行该架构设计的其他星上载荷监测到SEU发生故障概率平均约1月/次,由此可见该架构和算法能有效降低SEU的故障次数,满足工程实用性的需求。

对红外遥感相机图像的非均匀性指标进行预设,若其变化超过5%(可设置),则对图像参数算法进行程序自主重构,使图像性能达到系统要求指标范围5%以内。图11为程序自主重构前参数效果图,图12为程序自主重构后参数调整效果图。

图11 参数调整前图像Fig.11 Image before parameter adjustment

图12 参数调整后图像Fig.12 Image after parameter adjustment

通过以上系统功能性验证表明,本设计实现了多源刷新重构,对于在轨遇到性能参数发生变化影响系统使用时,可通过在轨程序自主重构满足系统在轨使用性能,并且在工程项目中得到很好的应用。

4 结 论

本文提出了基于Xilinx Virtex系列SRAM型FPGA的自主多源重构方法,针对不同Xilinx Virtex系列FPGA能够自主识别,采用不同存储器源头,对SRAM型FPGA进行灵活刷新、重构,不仅提供了可以通过在轨上注程序并且自主重构满足图像性能的办法,还有效减少了SRAM型FPGA在轨遇到单粒子问题的次数,成功实现了在轨定时刷新+多源+自主的抗单粒子高可靠性方案。