基于ADF4356锁相环的雷达频率合成器设计

2022-03-31王玉江刘刚张迪雅陈

王玉江刘 刚张迪雅陈 珊

(四川航天电子设备研究所,四川 成都 610100)

0 引言

雷达频率合成器将一个高稳定晶振作为基准源,经过混频器、倍频器、分频器等进行加减乘除运算后产生各个输出相位差固定的全相参信号,其主要包括采样时钟信号、本振信号、直接数字合成(DDS)时钟信号等。频率合成技术主要包括直接式频率合成、直接数字式频率合成,间接式频率合成3种方法。其中直接式具有分辨率高、频率转换快、相位噪声极低等主要优点,但是由于直接频率合成采用大量的有源和无源器件,易产生大量杂散,需要通过体积较大的腔体滤波器进行滤除,从而使得合成器的体积变大,成本升高,这是其主要缺点。直接数字式同样具有相位噪声低、频率转换快等优点;但其工作频率较低,无法直接产生高频段信号。间接式的优点在于将锁相环构成一个窄带跟踪滤波器,具有良好的窄带跟踪特性,可以很好地选择所需的频率信号,抑制杂散分量,避免使用大量滤波器,有利于集成化和小型化,具有成本低的优势;其缺点主要是相位噪声和跳频响应时间相比前两者较差。由于本频合器输出信号均为固定频信号,且不需要进行频率跳变,故对跳频时间不做要求,其中产生的信号作为雷达的第二接收本振信号,对相位噪声要求没有那么高。因此,采用间接式频率合成技术对雷达频率合成器进行设计。本文详细介绍了高性能锁相环芯片ADF4356,该芯片集成了压控振荡器,外围电路简单,性能稳定,输出信号相位噪声低、杂散抑制度高,为弹载雷达导引头提供了一种基于锁相环雷达频率合成器的解决方案。

1 锁相环工作原理

间接式锁相式频率合成技术的核心是锁相环(PLL),锁相环是闭环跟踪电路,可以实现对压控振荡器(VCO)的输出信号频率与输入信号频率的自动跟踪,保持信号相位一致。锁相环主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)组成。其工作原理如图1所示,为输入信号的频率,为输出信号的频率。当和的次分频的频率不一致时,PD 将产生一个低频分量,使得VCO 的输出频率通过LF 控制电压来控制VCO 的输出频率。受闭环反馈电路的影响,和的相位差将保持在一个不变的范围内,PLL环路此时处于“锁定”,输出信号频率为=×。

图1 锁相环工作原理图

本雷达频率合成器采用多片锁相环芯片,以产生不同频率的输出信号,从而满足雷达系统总体的要求。输出信号主要包括采样时钟信号、接收本振信号以及DDS工作时钟信号等。

1.1 指标要求

本雷达频率合成器根据雷达系统的工作要求,确定了其参数指标,设计指标如表1所示。

表1 不同输出信号指标要求

1.2 器件选型

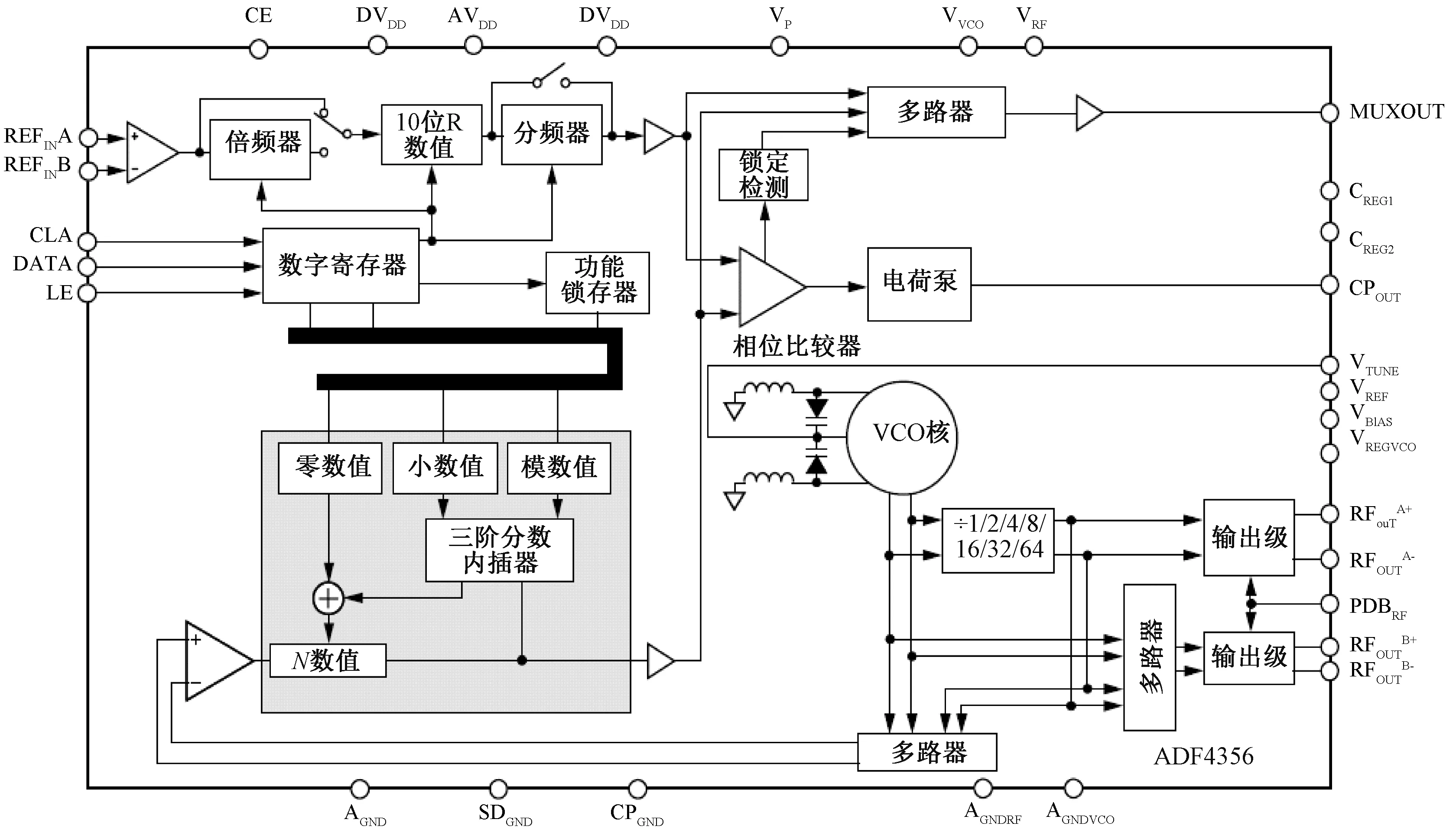

PLL芯片是频率合成器的核心器件,该器件选用ADI公司生产的ADF4356型锁相环芯片,其最高鉴相频率达到125 MHz,参考输入频率最高可达600 MHz,可获得极低的带内相位噪声性能,归一化相位噪声基底为-227 d Bc/Hz,工作频率为53.125~6 800 MHz,满足合成器产生各个不同频率信号输出范围。ADF4356 具有集成的VCO,并带有4.75~5.25 V 的电荷泵和VCO 电源,无需有源环路滤波器,只需外部添加无源环路滤波电路,实现环路带宽的设置。片内寄存器均采用三线式接口进行控制,并具有硬件、软件掉电模式。ADF4356是一款高性能的PLL芯片,其内部结构如图2所示。

图2 ADF4356内部结构图

由图2可得,锁相环芯片ADF4356内部集成了鉴相器、压控振荡器、分频器以及各个寄存器,其工作频率为3 400 MHz~6 800 MHz,通过内部各个分频器,从而产生53.125 MHz~6 800 MHz的输出信号。结合外部环路滤波器和外部参考输入信号使用时,可实现小数分频或整数分频,从而产生不同频率的输出信号,且输出功率为-2~7 dBm。本设计采用现场可编程门阵列(FPGA)作为锁相环芯片ADF4356 的程序控制,通过配置锁相环芯片的寄存器,实现了采样时钟信号、DDS工作时钟信号、接收本振信号分别为1.2 GHz、4.8 GHz、6 GHz不同频率的输出信号。ADF4356的CLK、DATA 和LE 为控制数据传输接口,时钟信号频率最大50 MHz,当CLK 从低电平到高电平时,32位数据写入内部的R0~R13寄存器;当LE由低电平变为高电平时,数据被传输至对应的锁存器,从而实现不同频率信号的输出。

1.3 ADF4356寄存器配置

根据芯片手册可知,PLL输出信号频率为:

式中:为PLL 内部分频器分频比的整数部分;为PLL 内部分频器分频比的小数部分;为鉴相频率;为参考输入信号的倍频位(0或1);为二进制可编程控制器的预设分频比(1~1 023);为参考输入信号的分频位(0或1)。

本文参考输入信号频率为100 MHz,由于产生的输出信号均为参考输入信号的倍数关系,故选用内部分频器的工作模式为整数分频模式。当输出信号频率为4.8 GHz信号时,相关参数设置为=100 MHz,=0,=1,=1,=96,=0;当输出信号频率为6 GHz信号时,相关参数设置为=100 MHz,=0,=1,=1,=120,=0。通过FPGA 软件配置控制程序,从而控制锁相环ADF4356 相应的寄存器R0~R13,实现对不同输出信号4.8 GHz和6 GHz频率的控制,根据以上参数值,可确定锁相环的主要寄存器R0分别为0x00200600、0x00200780。

1.4 相噪分析

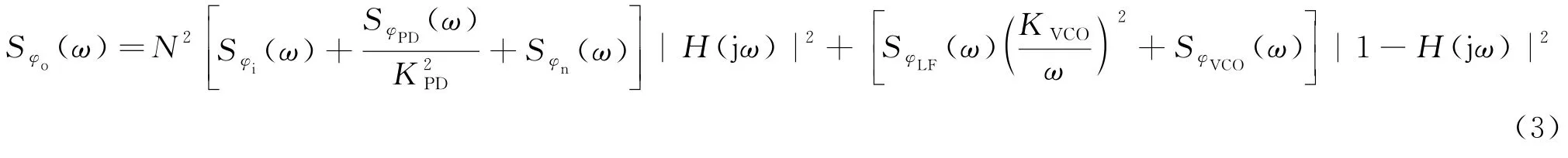

在进行相位噪声分析时,必须考虑输入信号、鉴相器、环路滤波器、压控振荡器、分频器等引入的相位噪声,其锁相环的相位噪声分析模型如图1所示。图中S()为输入信号引入的相位噪声功率谱密度,S()为鉴相器引入的相位噪声功率谱密度,S()为环路滤波器引入的相位噪声功率谱密度,S()为压控振荡器引入的相位噪声功率谱密度,S()为分频器引入的相位噪声功率谱密度,S()为输出信号的相位噪声功率谱密度,为鉴相器增益常数,()为环路滤波器的传递函数,为VCO 的压控灵敏度,为分频比。通过对相关器件的传递函数理论分析与公式计算,最终可得输出信号的总相位噪声功率谱密度为:

由式(2)可得,锁相环路对输入信号噪声、鉴相器输出噪声、分频器输出噪声具有低通作用,而对环路滤波器输出噪声、压控振荡器的相位噪声呈高通作用,则低通上限截止频率和高通下限截止频率就构成了环路带宽。其输出信号的相位噪声由输入信号、鉴相器、分频器、环路滤波器和压控振荡器共同决定。锁相环ADF4356芯片主要由低噪声鉴相器、精确电荷泵和可编程参考分频器等组成。锁相环带内的相位噪声主要由鉴相器、环路滤波器、分频器以及压控振荡器决定。通过分析鉴相器对相位噪声的影响起决定性作用,鉴相器的噪声主要由闪烁噪声和基底噪声组成,其中基底噪声对相位噪声起主要作用,根据锁相环相位模型可得,锁相环输出相位噪声为:

式中:S为锁相环输出相位噪声;S为锁相环输入相位噪声;为鉴相器输出相位噪声;为鉴相器增益;为分频数。

由式(3)可得,输出相位噪声由输入参考信号相噪和鉴相器噪声共同决定,当参考信号的相噪较好时,锁相环输出带内噪声主要由鉴相器决定。根据鉴相器归一化噪声基底、鉴相频率及分频数,可计算输出相位噪声为:

式中:为噪声基底;为鉴相频率;为分频数。

当输出信号频率为4.8 GHz 时,则=50 MHz,=96,由式(4)计算得到带内相噪约为-110 d Bc/Hz;当输出信号频率为6 GHz 时,则=50 MHz,=120,计算得到带内相噪约为-108 dBc/Hz。

2 锁相频率合成器在ADIsimPLL 中的仿真设计

ADI公司提供了一款仿真软件ADIsim PLL,在功能和参数方面进行辅助仿真设计,适用于一切ADFxxx 系列的锁相环产品。其特点主要有:包含整数分频和小数分频2种分频模式;输出信号既可以是点频信号也可以是一定频率范围的信号;内部包含ADFxxx系列产品全部信息库;具有多种环路滤波器电路拓扑结构选择等。

在已知参考输入频率、鉴相频率、输出频率、环路带宽和相位裕度时,可以通过ADISimPLL 对环路滤波器的电阻、电容值参数进行确定,从而实现对环路滤波器的设计。环路滤波器的设计参数直接关系到输出信号的杂散、相位噪声以及锁定时间等技术指标。由于无源滤波器只使用电阻、电容(RC)低通滤波器,其具有结构简单、成本较低、稳定可靠等优点。

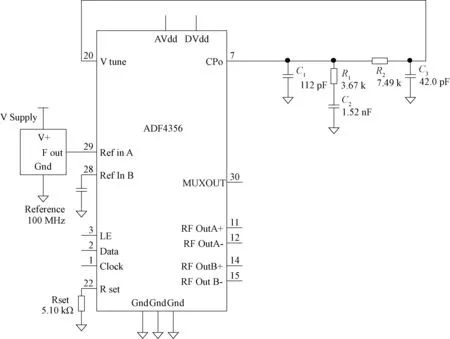

通过ADIsimPLL 对环路特性进行仿真,环路带宽设置为80 k Hz,输出频率为6.0 GHz,参考输入信号为100 MHz,且相位噪声为-150 dBc/Hz@1 k Hz,鉴相频率为50 MHz,采用3阶环路滤波器结构,ADF4356接收本振信号ADIsimPLL 仿真电路如图3所示。

图3 ADF4356环路滤波器仿真图

其中环路滤波器仿真参数值为:=112 p F,=3.67 kΩ,=1.52 nF,=7.49 kΩ,=42 p F。由于电阻、电容值与实际工程值存在偏差,故电阻、电容值采用=110 p F,=3.6 kΩ,=1.5 n F,=7.5 kΩ,=40 p F。

由ADISimPLL 仿真可得系统输出6 GHz相位噪声,如图4所示。图4中1 k Hz时,系统的相位噪声约为-95 dBc/Hz@1 k Hz,该理论值在实际应用中,由于存在电源噪声、外界杂波信号干扰等因素,实际相位噪声会有一定的恶化。

图4 相位噪声仿真图

因此,可以通过设置环路滤波器带宽、提高参考信号的相位噪声等方法来改善系统输出信号的相位噪声。输出信号6 GHz的时间关系如图5所示,系统输出信号的稳定时间为1.7 ms,锁定时间小于2 ms,满足雷达系统对固定点频接收本振信号稳定时间的要求。

图5 输出信号与时间关系图

3 锁相环雷达频率合成器总体设计

基于ADF4356 锁相环雷达频率综合器以100 MHz高稳恒温晶振作为参考输入信号源,运用功分器、锁相环、分频器、放大器、滤波器等器件,产生不同输出信号的频率源。锁相环雷达频率合成器产生原理如图6所示,其输出信号为:1.2 GHz信处采样时钟信号,4.8 GHz的DDS时钟信号,6 GHz的接收本振信号。由于恒温晶振相位噪声较好,产生不同输出信号的频谱比较干净,相位噪声较低,因此,本设计通过使用高性能恒温晶振作为参考信号源,运用LC元件参数滤波器仿真和ADIsim PLL锁相环环路滤波器仿真等方法,最终设计了一种高性能的频率综合器。

图6 锁相环雷达频率综合器总体原理框图

3.1 DDS参考时钟信号

由于DDS具有频率分辨率高、频率捷变快和易于控制等优点,广泛应用在雷达系统中。DDS参考时钟信号为DDS提供工作时钟,但由于受到奈奎斯特采样定理的限制,DDS输出频率只能达到参考时钟的40%,其国产芯片GM4912的参考时钟高达5 GHz,输出频率最高可达2 GHz。为了保证DDS既要在合理区间,又要满足输出信号的高频率要求,因此DDS参考时钟定为4.8 GHz,其输出频率可达1.9 GHz,满足上行基频信号的要求。

DDS时钟信号由ADF4356 直接产生,其参数指标要求:输出功率为0±2 d Bm,杂散≤-50 dBc。芯片输出信号功率为-2~7 dBm,满足0±2 dBm输出功率要求;锁相环自身具有较好的杂散抑制度,其抑制度达到60 dBc以上,满足杂散指标要求。

3.2 接收本振信号与采样时钟信号电路设计

接收本振信号是将接收通道进行下变频所需要的本振信号,该信号为6 GHz点频信号。信处时钟信号为信号处理机提供采样时钟,根据系统要求,信处采样时钟信号为1.2 GHz,其详细产生原理图如图7所示。接收本振点信号将100 MHz参考信号作为输入,芯片ADF4356直接产生,该芯片最大输出信号频率为6.8 GHz,满足产生6 GHz点频信号。6 GHz信号经过两功分器,一路信号放大后再四路功分,从而产生四路接收通道的接收本振信号;另一路信号经五分频器分频得到1.2 GHz信号,再经滤波、放大后输出给信号处理机。

图7 接收本振信号与采样时钟信号电路原理框图

接收本振信号的指标为:输出功率为13±2 dBm,杂散优于60 dBc,相位噪声优于-80 dBc/Hz@1 k Hz,输出信号功率采用两级芯片进行放大,保证足够的输出功率;锁相环产生信号的杂散抑制度都可以达到70 d Bc以上。采用100 MHz恒温晶振,相位噪声达到-150 dBc/Hz@1 k Hz,而在对锁相环芯片进行配置时,通过ADISim PLL仿真,产生6 GHz信号的相位噪声达到-95 dBc/Hz@1 k Hz,满足-80 d Bc/Hz@1 k Hz 的设计要求指标。1.2 GHz采样时钟信号的指标为:输出功率10±2 dBm,杂散优于-60 d Bc。1.2 GHz采样时钟信号由6 GHz五分频得到,由于分频导致谐波较高,需要使用低通滤波器滤除谐波再进行放大,放大后再用带通滤波器滤除杂散,从而使杂波抑制度满足指标要求。

4 实验测试与分析

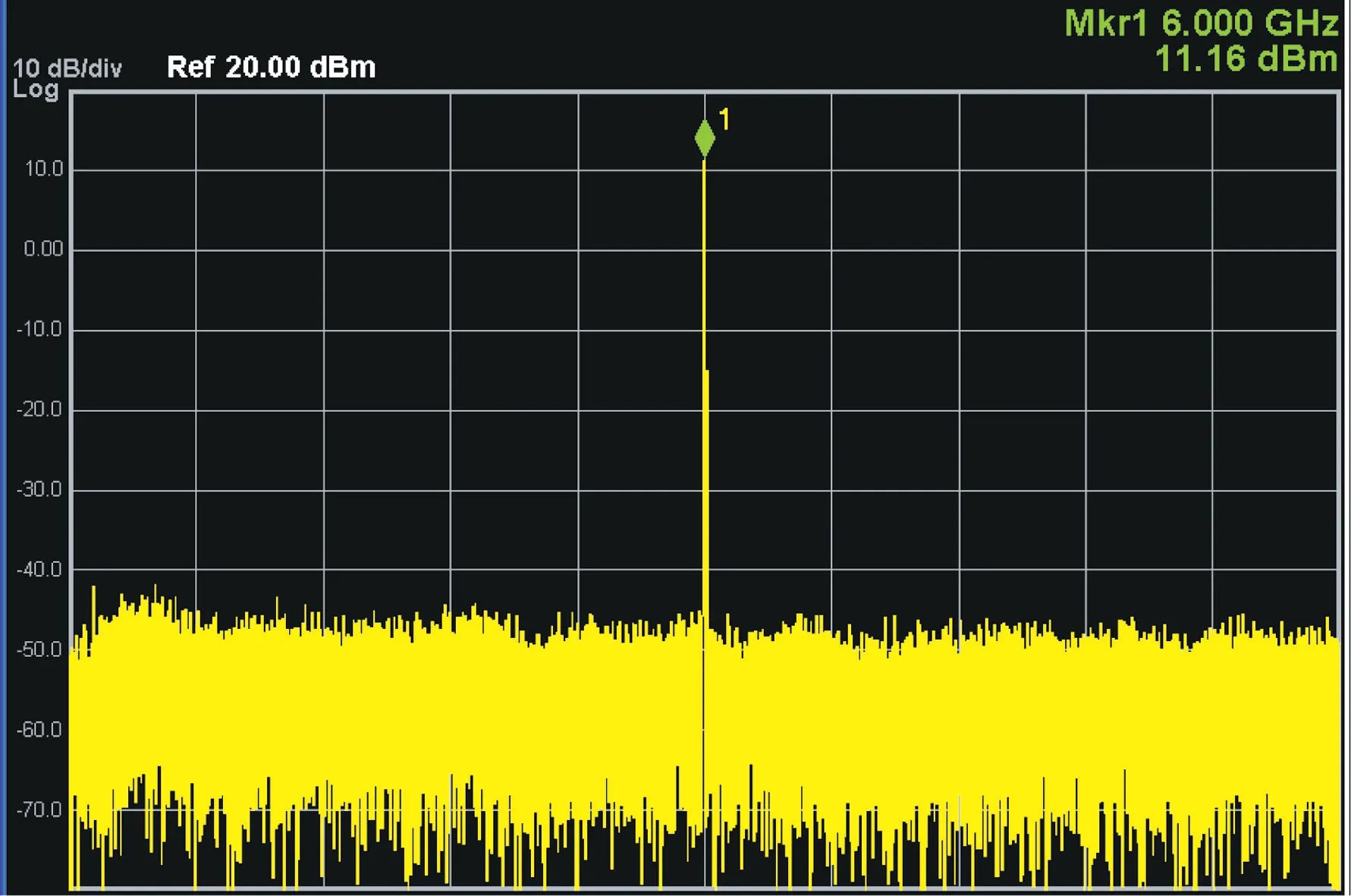

通过搭建实验测试平台,使用9030A 频谱仪对雷达频率合成器输出的接收本振信号、DDS参考时钟信号以及采样时钟信号的功率、杂波、相位噪声等参数进行实测,其中接收本振信号的功率谱如图8所示,输出功率为11.16 dBm,杂散抑制度为55 dBc,其相位噪声实测图如图9所示,相位噪声曲线平稳,在1 k Hz条件下的实测相位噪声为-83 dBc/Hz,理论相位噪声值为-95 dBc/Hz@1 k Hz,实测值存在一定的恶化,这是由于晶振的相噪存在一定偏差或电源模块噪声代入等因素所致,实测值优于-80 d Bc/Hz@1 k Hz的指标设计要求。虽然锁相环间接频率合成信号的相噪指标与直接频率合成信号的相噪存在一定差距,直接频率合成虽然相噪指标优异,但是大量的倍频器、高性能LC 滤波器、放大器等器件集合在一起,导致链路较长,电路复杂,体积较大,可靠性低等问题。基于锁相环频率合成信号的电路简单,频谱干净,易实现产品的小型化,在电性能指标不变的情况下,采用锁相环形式,可以满足当前对雷达导引头小型化的需求。

图8 本振信号频谱图

图9 本振信号相位噪声实测图

雷达频率合成器各个输出信号的实测参数值与设计值对比如表2所示,所有测试值均满足指标要求,达到了预期效果,从技术层面改善了雷达导引头频率合成器的整体性能,为雷达系统提供了高质量的本振信号。

表2 不同输出信号实测参数对照表

5 结束语

雷达频率合成器运用锁相环间接频率合成技术,基于ADF4356 锁相环芯片,配置寄存器产生4.8 GHz和6 GHz不同频率输出信号,其中6 GHz本振信号的相位噪声达到-83 dBc/Hz@1 k Hz,近端杂散可达60 d Bc,远端杂散可达55 d Bc,高质量的本振信号提高了雷达导引头接收机的灵敏度。该频率合成器具有体积小、重量轻、功耗低、稳定可靠等特点,为弹载雷达导引头提供了一种基于锁相环雷达频率合成器的解决方案。