基于FPGA 的多通道音频信号评估系统

2022-03-07张皓然万书芹蒋颖丹

张皓然,万书芹,蒋颖丹,张 涛

(中科芯集成电路有限公司,江苏 无锡 214063)

0 引言

人类的耳朵可以感受各种频段的音波,包括自然界里各种天然的声音,也包括人工生成的声音。科学研究表明人耳所能感受到的声音范围是20~20 000 Hz,但这并不是人耳真正能识别的频率[1]。人们正常说话的声音频段在500~4 000 Hz,而让人们放松舒适的频段在20~600 Hz,所以20~4 000 Hz 频段的声音最有研究价值。如何精确地获取这个频段声音的信息参数成为评估其质量的关键。

因此,本文提出了一种基于FPGA 的六通道音频信号评估系统,针对20~4 000 Hz 频段的声音,选用最高64 kS/s 采样频率,16 bit 采样精度的六通道ADC。系统中FPGA 和ADC 通过工业串行端口(SERIAL PORT,简称SPORT)进行功能配置和数据传输,依托MATLAB 图形化用户界面(GUI)实现了对应的上位机,配合FPGA 的嵌套状态机,可实时显示采样数据的时域波形和经过快速傅里叶变换(FFT)的频谱曲线。该系统经过了测试和验证,可以准确反映出对应频段音频信号的质量。

1 系统架构设计

一般信号采样处理系统会采用具备一定速度和容量的存储器件来暂存数据,以解决采样端数据发送速率和上位机数据接受速率之间不匹配的问题[2]。常用系统结构如图1 所示。信号源为ADC 提供输入模拟信号,经由ADC 转换成数字信号并传输给FPGA,FPGA 在高速时钟下将采样信号保存到存储器件中,在存储了一定容量的数据后,再将信号从存储器件中读出,通过USB 接口传输给上位机。

图1 一般信号采样处理系统总体框图

该结构非常适用于数据采样速率快且传输数据量大的应用场合,此时需要使用高速的大容量存储器件,成本较高,设计难度较大。当数据采样速率较慢,数据量较小时,该方案并不是最好的选择。

本文提出了一种新的设计方法,为低频采样且数据量小的应用需求提供了另外一个可选方案。以FPGA 作为主体芯片,实现对ADC 器件的功能配置;ADC 信号采样后通过SPORT 端口发送给FPGA,FPGA 按照状态机跳变将接收到的数据依次存入内部FIFO 中,然后在ARM 处理器计算出波特率,再将数据发送给上位机,完成数据存储和处理。系统总体架构如图2 所示。这种方法减少了系统对存储芯片的依赖,简化了硬件电路板的设计。

图2 系统总体框图

2 器件选型

2.1 FPGA 选型

本设计选用Intel 公司的Cyclone III 系列的EP3C25-Q240C8N 芯片。该型号具有丰富的资源,包括24 624 个逻辑单元,608 256 bit 的存储空间,并有着丰富的IP 资源,可根据不同需要例化不同的IP[3]。其系统时钟倍频后最高可达800 MHz,满足应用需求。

由于FPGA 的自身特点,掉电会丢失数据,实际应用中需配备具有存储功能的芯片来保存程序或者其他一些关键数据。这里选用EPCS16N 芯片存储FPGA 程序数据,在Debug 程序时,选择JTAG 下载方式,无需Debug可直接固化程序时,选择AS 下载方式,这样程序就会被保存在EPCS16N 中,掉电后也不会丢失。

2.2 ARM 处理器选型

ARM 处理器在整个系统中作为辅助单元,主要用于计算FPGA 和上位机间最匹配的通信速率以满足在任何ADC 速率下不会出现丢码。

ST 公司的STM32F4 系列芯片是F1 系列的加强版,内部新增DSP 内核,具有强大的数据计算能力,并且具有快速的总线通信机制——可变静态存储控制器(Flexible Static Memory Controller,FSMC),通信频率可达84 MHz,满足快速通信的需求[4]。因此选用该系列的STM32F407型号。

2.3 ADC 选型

本文选用亚德诺半导体公司的AD73360。该模数转换芯片具有16 bit 的有效位数,内置了6 个独立的ADC内核,可同时对6 路通道的输入信号进行轮流采样,并且每路通道在4 kHz 的信号带宽上提供77 dB 的信噪比,通过SPORT 可以设置成四种不同的采样速率,分别是8 kHz,16 kHz,32 kHz,64 kHz。

2.4 USB 协议芯片选型

FPGA 与上位机通信的速率需要考虑输入信号的频率和ADC 的采样速率是否匹配,如果两者之间的速率不匹配会导致最后的采样出现丢码。考虑到通信的多变性和稳定性,将USB 协议作为传输协议,连接上位机和FPGA。

设计中采用RS232 协议转USB 协议的方式实现USB通信。输入信号频率范围是20 Hz~4 000 Hz,如果ADC采样频率一直是64 kHz,当输入20 Hz 信号时,一个周期采样3 200 个点;如果一直是8 kHz,当输入频率是4 000 Hz时,一个周期才2 个点,这显然是不合理的。因此,为了使得采样数据个数在合理的范围内,本文设计通过另一路RS232 告知FPGA 输入信号的频率,然后FPGA 根据最小采样点不少于16,最大采样点不大于400 的规则去酌情选择采样频率。

ADC 的采样频率是8 kHz~64 kHz,输入信号的频段是20 Hz~4 000 Hz,各个频率的声音信号一个周期不少于16 个点,6 个通道数据一起输出,可由式(1)计算出波特率的范围是1 536 b/s~307 200 b/s。

其中R 表示通信波特率,m 表示采样精度,n 表示通道数,S 表示ADC 的采样频率,I 表示ADC 的输入频率。

RS232 通信协议的发送操作中包含11 位信号,其中8 位是数据位,1 位起始位,1 位停止位和1 位空闲位,因此,真实的波特率范围是2 112 b/s~422 400 b/s。

USB 协议芯片选用CP2101,其支持RS232 协议转USB2.0 协议,支持的波特率范围是300 b/s~921.6 kb/s,有充足冗余,可以流畅地与上位机端通信[5]。

3 设计方案

FPGA 总体逻辑设计框图如图3 所示。在Quartus 软件上直接对FPGA 进行基于Verilog 语言的RTL 流程开发,配合JTAG 和SignalTap 进行程序在线调试[6],ModelSim软件作为验证仿真手段,可单独对SPORT 时序、FIFO、FSMC 接收时序和嵌套状态机进行仿真验证,经过严密的逻辑仿真,修订BUG 后下载FPGA 程序完成闭环设计。STM32 的程序开发在KEIL 软件上可以完成。

图3 FPGA 总体逻辑框图

MATLAB 中自带图形化用户界面功能,创建的图形界面可以调用M 语言编写的算法函数,可以实现USB 通信和FFT 运算,实现上位机功能。

3.1 FPGA 程序设计

3.1.1 SPORT 通信协议

AD73360 的SPORT 通信协议是由SCLK、SDO、SDOFS、SDI、SDIFS 和SE共6根信号组成的。SPORT协议有三种工作模式:控制模式、数据模式和混合控制数据模式,本文只用前两种模式。使用控制模式将ADC 配置成预期的工作状态,然后使用数据模式接收数据。

控制模式下,SE、SCLK、SDI、SDIFS四根信号工作,其他信号不工作;数据模式下,SE、SCLK、SDO、SDOFS 四根信号工作,其他信号处于空闲态。时序图如图4 所示[7]。

图4 SPORT 控制模式和数据模式时序

AD73360 具有6 个采样通道,数据采集是按照数字顺序依次进行的,根据SDOFS 的脉冲,采样数据依次通过SPORT 时序被读出。

3.1.2 嵌套式状态机

整个系统的逻辑是由一个三层嵌套式的状态机实现的[8]。

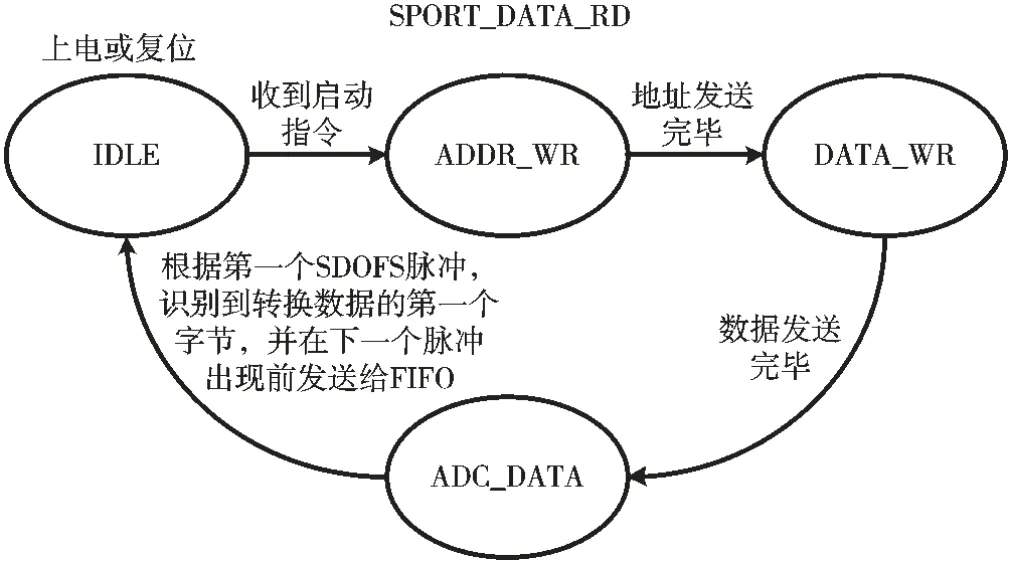

如图5 所示,第一层状态机逻辑具有4 个状态:空闲态(IDLE)、写地址(ADDR_WR)、写数据(DATA_WR)、ADC 数据接收(ADC_DATA)。其主要功能是实现SPORT逻辑实时。

图5 第一层状态机

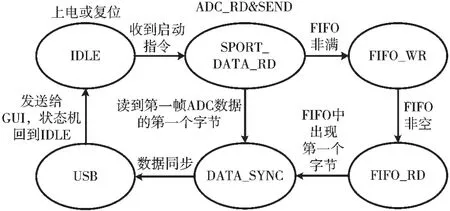

第二层状态机逻辑如图6 所示,具有6 个状态:空闲态(IDLE)、SPORT 读数据(SPORT_DATA_RD)、FIFO 写数据(FIFO_WR)、FIFO读数据(FIFO_RD)、RS232-USB 协议转换(USB)、SPORT 接收数据与FIFO 读出数据同步(DATA_SYNC)。其主要功能是实现FIFO 存取以及USB端的数据发送。

图6 第二层状态机

如图7 所示,第三层状态机逻辑具有7 个状态:空闲态(IDLE)、ADC 数据接收及发送(ADC_RD&SEND)、RS232发送给GUI 数据(GUI_TX)、RS232 接收来自GUI 的数据(GUI_RX)、FSMC发送数据(FSMC_TX)、FSMC接收数据(FSMC_RX)、通信速率同步(COM_SYNC)。

图7 第三层状态机

第三层状态机主要实现了GUI、FPGA 和STM32 三者之间的通信,实时更新第二层状态机中USB 端的通信速率,以及第一层状态机中SPORT 端口数据读取的时刻,确保与GUI 的通信不丢码。

3.1.3 FIFO 设计

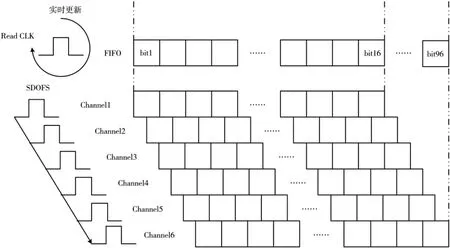

由于在数据模式下,ADC 会对6 个通道的信号依次采样,每个通道采样的数据是16 bit,因此每次采样的数据按照96 bit 为一个单位。所以,FIFO 的深度确定为96 bit,宽度为1 bit。设计中调用了FPGA 中FIFO 的IP 核,该IP 核可根据需要更改深度,并且可以配合其他模块完成RTL 级仿真。6 个通道数据全部采样完成后,下一帧数据的采样到来前会有约45 个SCLK 的总线空闲时间。而SCLK 是由主频16.384 MHz 分频得来的。这段空闲时间最短为45/16.384 MHz=2.746 μs。

在这段时间里,要完成FIFO 中6 个通道数据的写入和数据的同步。这里采用了FPGA 内部的PLL 倍频IP核,可以将内部时钟倍频到最高500 MHz,根据实际情况,选用了200 MHz 的内部工作频率,处理6 个通道16 bit数据 只需要96/200 MHz=0.48 μs。

由于数据是严格按照SDOFS 脉冲采样的,在SPORT控制模式配置完相关寄存器后,第一个SDOFS 脉冲对应着第一个通道的第一个数据,遵循这个规律存储数据,相位严格保持对齐。FIFO 的读取速率按照最近更新的STM32 计算出的数据波特率依次取出数据。FIFO 存取示意图如图8 所示。

图8 FIFO 存取示意图

3.2 ARM 程序设计

STM32 依托其可快速计算的DSP 内核和快速通信的总线,实时完成FPGA 和GUI 之间的速率更新,每一次计算完成后,询问FPGA 是否更新完毕,更新完毕后处于待机状态,等待下一次触发,否则重新发送再次询问直到波特率更新。程序设计流程图如图9 所示。

图9 STM32 程序设计流程图

3.3 上位机设计

上位机的主要功能是数据采集、处理、保存以及显示。MATLAB 中有一种图形化用户接口,采用图形方式显示计算机操作用户界面,底层调用了一些常用的驱动函数,方便进行人机交互操作[9]。

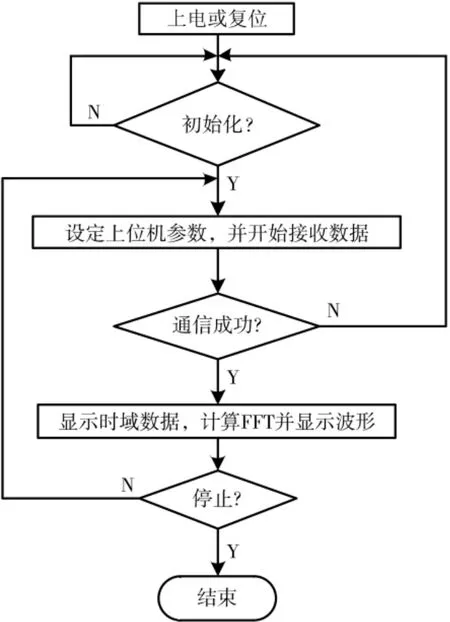

上位机的工作流程如图10 所示,首先输入信号频率数值(以赫兹为单位),选择串口通道、校验位、数据位和停止位,然后选择采样通道,点击打开端口,开始接收相应通道的数据。上位机有两块功能区:时域采样和频域处理,点击时域采样的打开按钮,采集到的原始数据会依次在右边的框图中显示;点击频域处理的开始按钮,内部快速傅里叶变换函数会开始对已有数据进行计算,以一定的数据量为基础,不断更新迭代,实时更新右边框图中的图形。

图10 上位机程序设计流程图

4 实验验证

系统完成后,首先进行硬件检查,软件调试和功能试运行,然后对SPORT 时序,FIFO 存取,以及上位机读取、处理数据的功能进行验证。

全部验证工作在测试实验间的实验平台中完成。实验平台如图11 所示。

图11 实验平台

4.1 SPORT 时序验证

验证SPORT 时序的主要方法是用Quartus 软件自带的逻辑分析仪SignalTap 去抓取,得到的波形与手册对比。

系统主要使用SPORT 的两个模式:控制模式和数据模式。前者用来配置寄存器,后者用来读取数据。能否正确回读数据是验证的重点所在,同时数据模式的时序正确也证明编写的SPORT 驱动是正确的。

系统参考电压是3 V,三通道输入1.5 V,回读的数字数据是0x7FFF,并结合各个信号的行为特征,证明SPORT时序正确。测试结果如图12 所示。

图12 SignalTap 抓取的SPORT 时序

4.2 FIFO 存取验证

FIFO 作为数据的缓冲,可以有效避免数据的错位和丢失,形成规则的数据流,利于数据处理。

FIFO 是队列形式的存储结构,逻辑规则是先入先出,FIFO 的写入时钟和读出时钟可以不一样,但也要遵循非满可写,非空可读的原则。

采用Modelsim 软件对FPGA 的FIFO 核进行仿真,按照顺序依次写入数据0xa5a5、0x0003、0x0005、0x0006、0x0015、0x0017。之后,再按照顺序依次读出,由图13 可知,FIFO 读出的顺序和写入时的顺序一致。

图13 Modelsim 仿真的FIFO 时序

4.3 上位机读取、处理数据的功能验证

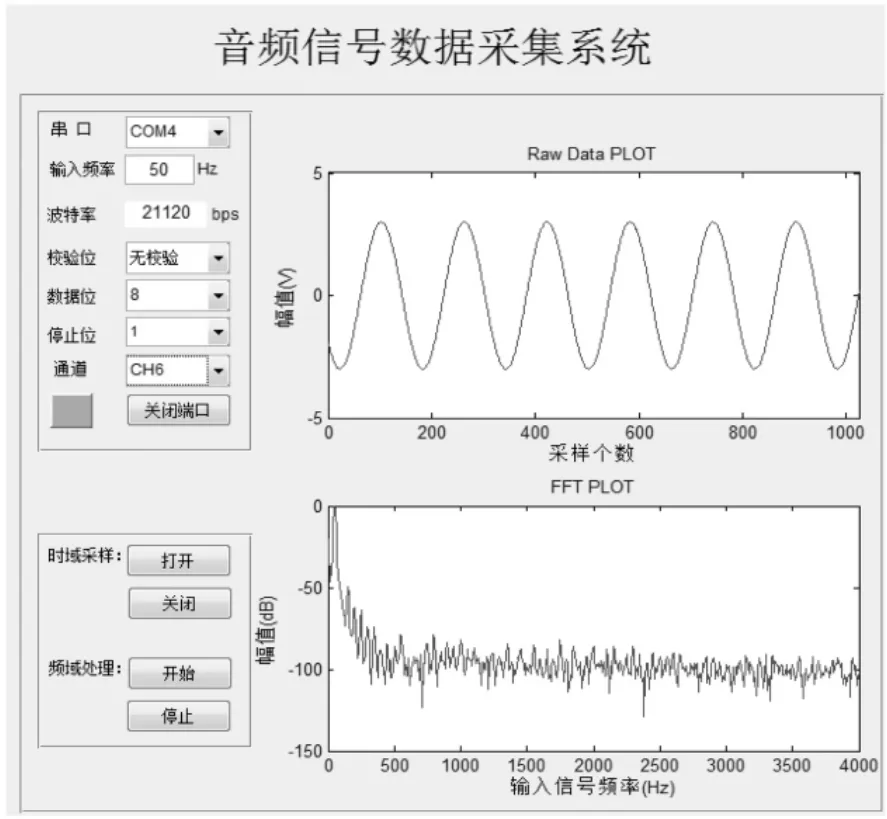

ADC 输入频率设定为50 Hz,根据理论,FPGA 会自动选择8 kHz 频率采样,每一个周期采样点是160 个点,波特率是160×6×22=21 120 b/s。由于窗口限制,考虑清晰度,数据只显示1 024 个点。

测试通道选择的是6 通道,串口是COM4,测试结果如图14 所示,FFT 处理结果是:SFDR=62 dB,SNR=80 dB。

图14 实测上位机界面

下面将ADC 的6 个通道按照50 Hz、200 Hz、1 kHz、4 kHz 四个频点分别采样,得到测试结果如表1 所示。

表1 6 通道音频信号测试结果(dB)

5 结论

由以上测试结果可知,多通道音频评估系统具有稳定的测试性能,低频输入下选择低频时钟采样,高频输入下选择较高的采样频率采样,保持数据量始终在一定的范围内波动。

最终测试结果显示低频的表现要比高频稍微好一些,符合数据手册参数。输入频率0~4 kHz,采样频率8 kHz 时,输出典型的SFDR 是73 dB,而采样频率是64 kHz时,只有62 dB。再加上仪器精密度限制和工艺制造误差,造成输出性能略逊于预期。但总体上满足对多通道音频信号采样评估的要求。