一种高速施密特触发器的设计

2022-03-07孙建民赵以诚

孙建民 ,闫 江 ,2,张 龙 ,赵以诚

(1.贵州大学 大数据与信息工程学院,贵州 贵阳 550025;2.北方工业大学 信息学院,北京 100144;3.北京中科格励微科技有限公司,北京 100089)

0 引言

在数字系统中,矩形脉冲信号经过传输后往往会发生畸变,因为信号在传输过程中会受到许多非理想因素的影响,如在PCB 板的寄生效应、封装过程的寄生电容电感、传输线上的寄生电容、接收端的阻抗不匹配以及其他信号线的噪声干扰等。这些不利因素会使信号的上升下降沿明显变缓,有时还会在信号的上升下降沿附近产生振荡,所以在数字系统中通常需要给输入信号进行滤波整形,以还原信号的完整性。施密特触发器是脉冲波形变换最常使用的一种电路,因为其在性能上有两个重要的特点:一是输入信号上升和下降过程中电路状态转换的阈值不同;二是电路内部存在正反馈过程使输出波形边沿变得很陡。利用这两个特点不仅可以加快信号边沿的变化,还可以有效地滤除叠加在脉冲信号上的噪声[1-2]。

传统的施密特触发器如图1[3]所示,由CMOS 反向器和TTL 门电路构成,基本结构是将两级反相器串接,通过电阻分压将输出端的电压反馈到输入端,通过改变分压电阻的比值可以调节阈值电压和滞回区间,电路结构简单,但是性能较差。

图1 传统施密特触发器

随着集成电路的发展,传统的施密特触发器不能满足数字系统高集成度、高可靠性、低延迟、低功耗的要求。文献[4]、文献[5]提出了基于电流模式的施密特触发器,采用差分跨导放大器模块,具有输入阻抗高、运算精度高的优点,适用于各种电流模式模拟信号处理应用,但不适用于大规模的数字系统。文献[4]提出了一种迟滞可调节的高速低压施密特触发器,通过体偏置电压的变化来调节阈值电压,与传统的结构相比,该结构具有可独立控制上升下降阈值电压的优点,但是该结构的传输延时受负载的影响较大,通用性较差[3-5]。

在数字隔离器系统中,信号与通道的匹配度和信号的传输延时是影响电路性能的重要因素,所以在电路设计时需要保证每个信号通道的翻转阈值完全一致,传输延时尽可能小,同时还需要考虑输入信号与供电电压的兼容性问题。基于以上考虑,本文提出一种电压—电流模式的高速比较器作为施密特触发器,以实现信号高速传输的功能。

1 高速施密特触发器的整体架构

本文提出的高速施密特触发器整体结构如图2 所示。Vin为输入信号,Vout为输出信号,Vth+和Vth-分别为上升和下降阈值电压基准。电流放大器(OCA)为比较器的翻转提供快速前馈通路以增加比较器的响应速度。电压比较器(COMP)采用差分式输入推挽式输出的跨导运算放大器(OTA),这是一种能够将输入的微小电压差信号放大为较大输出电流信号的结构,这种结构内部没有高阻节点,有较快的响应速度[6-9]。

图2 高速施密特触发器结构框图

图2 所示电路的具体工作过程如下:当输入电压变化时,电容C 和电阻R 将输入信号的变化转化为电流放大器的输入,即前馈电流。当输入电压从低到高变化时,前馈电路为比较器的翻转提供较大的灌电流,加速了比较器的翻转。比较器发生翻转后,Vout将信号反馈给阈值基准端,阈值基准切换为下降阈值Vth-。当输入信号从高到低变化时,前馈电路为比较器的翻转提供较大的拉电流,加速了比较器的翻转。比较器发生翻转后,阈值基准切换为上升阈值Vth+。

2 高速施密特触发器的电路设计

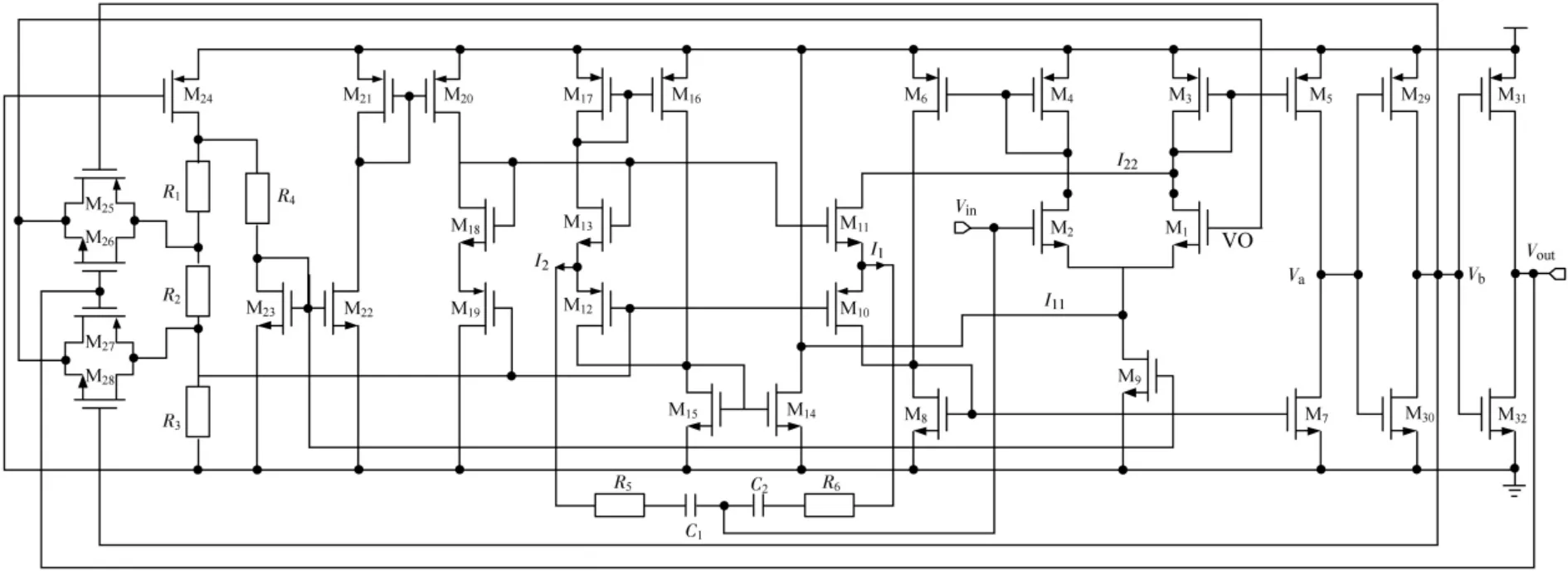

本文设计的高速施密特触发器如图3 所示。具体工作原理如下。

图3 高速施密特触发器电路结构

当Vin信号为低电平时,电路输出Vout为高电平,M25、M26 组成的传输门电路导通,阈值电压基准电路的输出VO为Vth+,连接跨导运算放大器的同相输入端。当输入电压Vin从低到高变化时,电容C1、C2将Vin的变化转化为M10、M12 的源端电流,作为电流放大器的输入电流。当Vin上升到Vth+时,OCA 输出电流达到最大值,为比较器的翻转瞬间提供了较大的下拉电流,加速了比较器的翻转。当比较器发生翻转,M25、M26 构成的传输门关断,M27、M28 构成的传输门导通,此时阈值电压切换为Vth-;同理当Vin从高到低变化时,发生与上述相反过程。

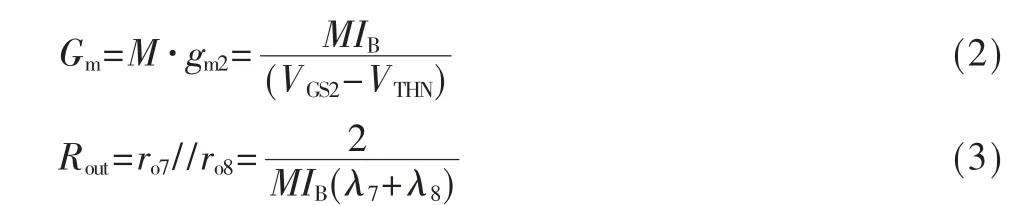

M1~M8 组成了跨导运算放大器(OTA)。与传统的电压比较器相比,跨导运算放大器具有结构简单、高频特性好的优点[8]。M1、M2 构成的差分输入端为电压电流转换级而非电压增压级,所以OTA 没有大摆幅电压信号和米勒电容效应,因此在使用时不需要进行频率补偿就有较好的频率特性[8]。M3~M8 为电流镜结构,电流传输比值决定了电流的放大倍数,OTA 增益表达式为:

其中Gm为OTA 的等效跨导,Rout为等效输出电阻。

其中M 为电流镜M3、M5 的电流传输比,IB为流过M9 的偏置尾电流,λi为第i 个晶体管的沟道调制系数。增大电流传输比M 和尾电流的大小IB可以增大输出电流,但是会降低电路的稳定性并增加电路的功耗。本文采用OTA与电流放大器相结合的结构,在保持M 不变的情况下增大电路的等效跨导,以加快OTA 输出的瞬态响应速度[7-9]。

M10~M13 和电容C1~C2、电阻R5~R6构成电流放大器作为OTA 的前馈通路。电容C1、C2和电阻R5、R6将输入电压的变化转化为电路放大器的输入电流I1、I2,经过M3、M5 电流放大器的输出电流I11流入比较器的尾电流,为比较器的翻转提供尾电流,加快比较速度。经过M16、M17 电流放大器输出电流I22流入比较器的输出级,加快了比较器的翻转速度。

M25~M28 组成两组传输门,通过电压Vout、Vb来控制传输门的输出电压VO,当Vout为高电平,Vb为低电平时,VO输出值为Vth+;Vout为低电平,Vb为高电平时,VO输出值为Vth-。Vth+和Vth-通过电阻R1、R2、R3分压产生,通过调节电阻阻值可以改变电压阈值和滞回区间[10-15]。

3 仿真结果

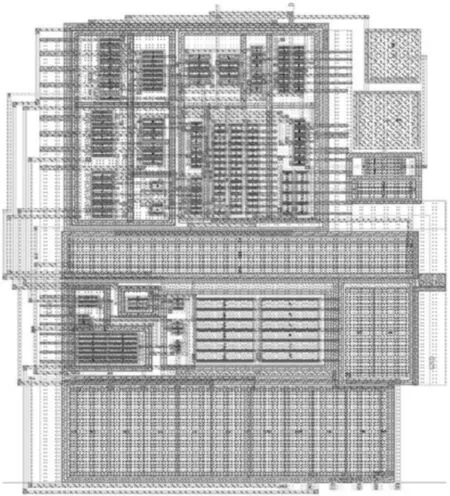

本设计采用GF_0.18 μm_BCD 工艺,电路的整体版图如图4 所示,利用Cadence ADE 仿真高速施密特触发器的动态特性,结果如图4 所示:图5 为阈值电压和滞回区间的仿真结果,本文设计的阈值电压为0.4 倍VCC和0.6 倍VCC,滞回区间为0.2 倍VCC,电源电压为3~5 V 时均能达到要求;从图6 中可以看出在比较器翻转瞬间,前馈通路为比较器提供了较大的拉灌电流,加速了比较器的翻转;图7 为比较器翻转时的阈值切换,在比较器发生翻转瞬间,Vth阈值电压切换,加速比较器恢复为稳定状态;图8 为高速施密特触发器工作在100 MHz 高频输入信号下的仿真结果,其电路延时为652 ps,信号的上升时间为54 ps,下降时间为65 ps。电路的整体性能如表1 所示。输入信号为100 MHz 时的整形结果如图9 所示,与其他文献性能比较如表2 所示。

表1 高速施密特触发器的整体性能

表2 施密特触发器的性能比较

图4 电路整体版图结构

图5 阈值电压仿真结果

图6 比较器瞬态响应

图7 阈值电压的切换

图8 传输延时仿真结果

图9 输入信号为100 MHz 时的整形结果

4 结论

通过仿真,本文设计的高速施密特触发器能够工作在电源为3~5 V 的系统中,输入信号和电源电压有较好的兼容性。同时电路本身的传输延时较小,能够对100 MHz的高速信号进整形滤波,当输入信号为100 MHz 时,上升时间为54 ps,下降时间为65 ps,电路的传输延时为652 ps,实现了高速度低传输延时的功能。