应用于有源相控阵的锁相环分频器设计

2022-03-05董飞翔陶小辉

董飞翔, 何 晴, 李 庄, 陶小辉, 曹 锐, 桑 磊

(1.合肥工业大学 电子科学与应用物理学院,安徽 合肥 230601; 2.中国电子科技集团公司 第三十八研究所,安徽 合肥 230088)

0 引 言

随着卫星通信、雷达和微波通信技术的发展,无线通信设备工作频率越来越高,高度集成的收发设备在移动设备无线通信领域受到广泛关注。高度集成相控阵系统用于各种通信、雷达和成像应用[1-2]。为使移动通信设备得到更广泛的应用,其硬件系统的成本必须大幅降低。生产高度集成的相控阵无需额外的外部元件,如昂贵的毫米波合成器、锁相环(phase locked loop,PLL)和开关,从而降低了整个系统的成本[3]。此外,消除外来的包装工艺和材料将进一步降低收发系统的成本。在有源相控阵收发系统中,需要用到高频的PLL为上行、下行转换器提供本地振荡信号。

本文采用130 nm SiGe BiCMOS工艺,使用异质结双极型晶体管(heterojunction bipolar transistor,HBT)[4]和CMOS实现了输出频率为20 GHz的PLL电路,可以用作W波段有源相控阵的本地振荡器。分频器作为PLL系统中功耗最大的模块,本文进行了特殊设计,以降低分频器链的功耗,并完成了分频器链的版图设计。

1 PLL环路设计

在电荷泵PLL电路[5]中,鉴频鉴相器(phase frequency detector,PFD)通过对比参考信号和分频器输出信号的频率相位差,使电荷泵(charge pump,CP)上拉或者下拉,经过环路滤波器(loop filter,LF)给压控振荡器(voltage controlled oscillator,VCO)提供偏压,进而产生高频振荡信号,该信号再通过分频器链反馈给PFD。当环路锁定后,VCO产生稳定的高频振荡信号。

PLL电路模块及仿真情况如图1所示。经过仿真实验,在156.25 MHz的参考信号下,400 ns以后PLL电路达到稳定状态,实现了20 GHz的信号输出。图1b所示为PLL双端输出结果的差值,摆幅为500 mV,且频率稳定在20 GHz。

2 分频器链的工作原理

2.1 二分频器工作原理

本文实现的分频器链基于二分频器进行设计。二分频器是通过将边沿控制D触发器的反相输出接到D端口。在时钟控制下,实现时钟1/2频率的信号输出[6],即Q*=D=Q′。其中:Q*为Q的次态;Q′为Q的反相。以此实现fout=fclk/2。

2.2 分频器链的实现机理

文中128分频器链路实现架构为7个二分频器的级联。基于130 nm BiCMOS工艺,前四级为HBT管的电流型逻辑(current mode logic,CML)实现[6-8],后三级则是以同工艺下的MOSFET的电压型逻辑(voltage mode logic,VML)实现。由于HBT管和MOSFET的启动条件不同,本文还设计了电平转换模块,用于连接前后不同的电路,提高HBT电路与CMOS电路的兼容性[9-10]。

3 二分频器电路

3.1 CML二分频器

鉴于HBT优异的高频性能[11],PLL电路采用HBT实现高频部分二分频电路。考虑到芯片常用的电源电压一般为3.3 、1.8 V,尾电流源结构通过镜像电流源实现。

文中电路采用3.3 V的电源电压,通过调整镜像电流源的电阻值,使得尾电流源结构的偏置电压为1.8 V。为方便各级的耦合,在CML二分频器电路后面加上射极跟随器结构,即采用射极耦合逻辑(emitter coupled logic,ECL),如图2所示。ECL结构可以提高电路的带负载能力,并有效提高了电路的工作速度,同时对晶体管还能起到一定的防击穿作用[12]。第1级二分频器工作在20 GHz的频率下,由于器件工作频率较高,尾电流源提供充足的电流才能保证其工作速度。在4.71 mA的偏置电流下,20 GHz单端摆幅为150 mV的差分时钟驱动(F-P和F-N)下,得到的单端输出摆幅为493 mV。

图2 ECL二分频器实现

文中采用的是1×4二分频器组,为满足低功耗的要求,可以适当地减小后三级ECL电路的功耗。在第1级的基础上,减小后三级ECL电路的尾电流的值来减小其电功率。在保证分频器功能的前提下,将后三级的尾电流调整为2.71 mA,并调整电路中HBT管尺寸以适应尾电流变化。并通过改变ECL电路负载电阻的大小,使得电路有足够的单端输出摆幅,此处调整为341 mV。

仿真结果显示,每级输出信号频率都是其输入信号频率的1/2,且双端信号具有很好的差分性。第4级单端输出的摆幅为341 mV(2.11~2.45 V),摆幅足够。

3.2 VML二分频器

因为采用差分时钟结构,所以在实现CMOS逻辑门D触发器时,采用差分时钟对。将D触发器电路进行简化,逻辑结构如图3所示,仅采用反相器和传输门实现,同时与ECL电路一相同,采用差分时钟对驱动,将输出反相接到输入端D,即可构成二分频器结构。

图3 实现的CMOS二分频器

将3个CMOS分频器级联,给第1级分频器一对差分时钟驱动,为保证CMOS管能够正常通断,输入时钟(IN-P和IN-N)的高低电平要满足低电平小于CMOS管的阈值电压,高电平要大于阈值电压,并且要有一定的裕度。

3.3 电平转换模块

由HBT管构成的ECL分频器,四级级联后的单端输出摆幅为341 mV(2.11~2.45 V),高低电平均在CMOS的阈值电压之上,因为用此信号驱动CMOS分频器电路,电路将无法正常工作,所以需要一个电平转换模块[6]将信号的电压转换到合适的范围。

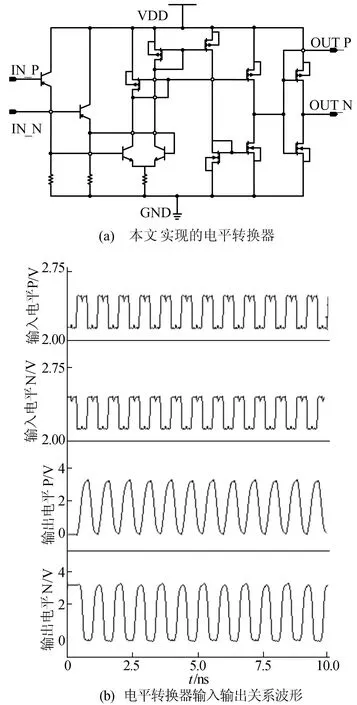

电平转换模块框图及仿真波形如图4所示。由如图4a可知,采用射极跟随器作为输入缓冲,提高电路应对输入信号电平变化的能力。输入信号进入HBT差分对管后,经过3个交叉耦合的镜像电流源,将信号的摆幅放大。再经过反相器得到差分的信号,可用于后面的CMOS分频器的驱动信号。由图4b可知,将 CML分频器链的差分输出IN-P和IN-N作为电平转换器的输入,得到摆幅为3.224 V(0.036~3.260 V)的输出结果。

图4 电平转换模块框图及仿真波形

4 级联电路的仿真结果

将四级ECL分频器与三级CMOS分频器通过电平转换模块进行级联,使ECL分频器的输出信号能够正常驱动CMOS分频器。

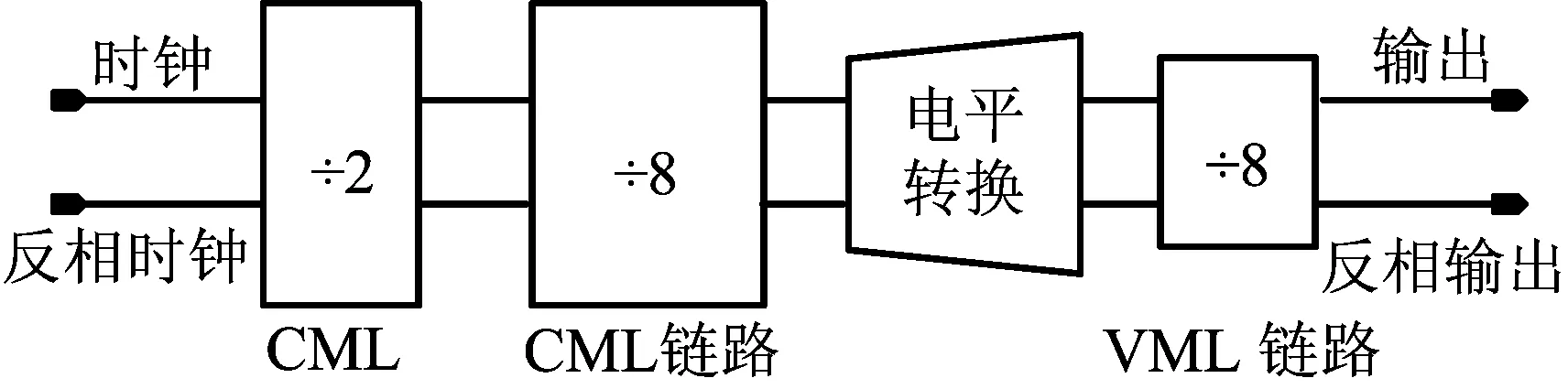

带电平转换模块的1×7分频器链如图5所示,即128分频。

图5 带电平转换模块的1×7分频器链

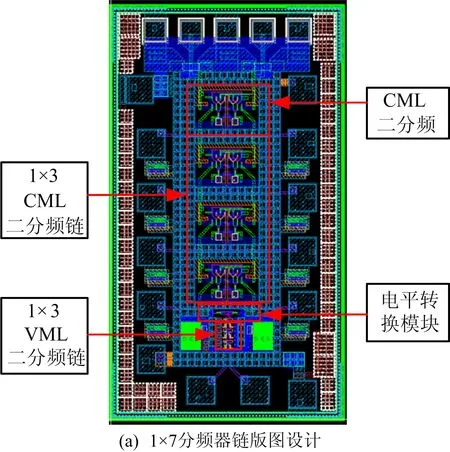

版图设计及仿真波形如图6所示。由图6a可知,版图尺寸为1 146 × 647 μm2。完成电路版图设计后,提取版图中的寄生参数,给施加分频器链如3.1节同样的驱动信号,提取寄生参数后的仿真结果。

由图6b可知,20 GHz的时钟信号经过分频器链之后得到156.25 MHz的输出结果,单端输出摆幅达到2.484 V,具有较强的带负载能力。寄生参数提取后仿真结果实现了预期功能。在第1节中,将本分频器链在PLL系统中,给PLL提供156.25 MHz的参考时钟信号,经过400 ns后PLL电路达到稳定状态,实现了20 GHz的信号输出。

5 对比与结论

本文指标与文献[6-7]指标对比结果见表1所列。

表1 指标对比

本文基于130 nm的SiGe BiCMOS工艺实现了工作频率为20 GHz的1×7二分频器链。前四级电路在D触发器经典CML结构基础上,根据本设计的需要进行了调整,使用镜像电流源和射极跟随器输出缓冲。为满足低功耗的需求,在满足性能要求的前提下,减小后三级ECL电路的偏置电流。

在更低的频率下,本文实现了CMOS二分频器,用于与ECL分频器级联提升分频比。同时,设计了电平转换模块,使HBT电路与CMOS电路兼容,实现了1×7二分频器链的级联,即128分频。完成了电路的版图设计,并提取了版图的寄生参数,仿真结果实现了预期功能,应用于PLL电路的反馈回路中,使得PLL系统成功地将156.25 MHz的时钟信号提高到20 GHz。