一种ADC电源方案设计与电源完整性分析

2022-03-03倪晓东赵家安肖永平马世娟

倪晓东,赵家安,肖永平,马世娟

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

随着半导体技术的迅猛发展,高集成度的现场可编程门阵列(Field-Programmable Gate Array,FPGA)、数字信号处理器(Digital Signal Processing,DSP)、ADC以及电源控制等芯片的功能越来越强大、体积越来越小[1-2]。除了无源模块外,其他所有模块均离不开电源供电以及电源转化。同时,随着集成电路产业的迅速发展,如何通过高效电源管理来延长使用寿命的问题随之而来,这就对电源芯片提出了更高的要求。

电源芯片根据应用和结构可分为AC/DC转换器、线性稳压器、DC/DC转换器等。直流电源中常用的两种结构为线性稳压器和DC/DC转换器。DC/DC转换器可实现降压、升压、反相功能,该类转换器具有效率高、输入电流大、静态电流小等优点,但噪声大、成本较高。低压差线性稳压器(Low Dropout Linear Regulator,LDO)主要包括带隙基准电压源、调整管、误差放大器、反馈电阻网络等,其自身结构中的调整管决定了该电源芯片具有损耗小、压降小的特点。LDO因功耗低、噪声小、电压纹波小、成本低、小型化、高性能等优点被广泛应用于功能模块的电源方案[3-8]。

为缩短模块设计周期,降低模块设计成本,减少可能出现的问题,信号完整性和电源完整性仿真已广泛应用到各项目中[9-11]。通过电源完整性分析与仿真,可以提前识别电源相关问题。在回板测试前,将优化手段加入方案原理图中,可更有效地改进电源,保证电源通路的稳定性和可靠性。

本文提供了一种2.5 V电源供电方案,并仿真了LDO芯片输出的2.5 V电压到达ADC芯片时的电压变化情况。

2 电源方案设计

本设计中共有20片ADC芯片,需1.25 V、1.8 V、2.5 V、3.3 V电源为其供电,以2.5 V为例说明电源供电方案实现方法。为20片ADC芯片供电的2.5 V LDO选用中科芯集成电路有限公司的JS74401电源芯片。

方案一:若每片ADC接收一个LDO供电,本设计中共有20片ADC芯片,则需要20片LDO。该方案为最常规的电源方案,电源稳定性和可靠性将得到保证。但是,该方案使用的LDO较多,无疑将增大模块面积,也将加大模块开发成本。

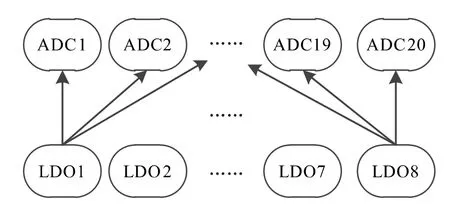

方案二:JS74401电源芯片LDO的输出电压范围为Vref~3.6 V,其中Vref为芯片内部参考电压,其值为0.796~0.804 V。该LDO输出电流最大值为3 A,根据ADC芯片输入2.5 V管脚的最大电流为0.780 A,可计算出一片LDO可给3片ADC芯片供电。20片ADC芯片包括16片工作频率为F1和4片工作频率为F2的ADC芯片。为减小不同工作频段ADC芯片因输入同一路电源造成信号干扰的可能,将工作频率为F1和F2的ADC芯片分开供电,则分别需要6片工作频率为F1和2片工作频率为F2的LDO芯片为ADC芯片供电,其供电方案原理如图1所示。

图1 本文采用的供电方案

两个方案使用相同的LDO芯片,每个LDO外围电路相同,版图设计时采用正、反两面布局,布局面积为80 mm2。供电方案一中使用20片LDO芯片,布局总面积为1600 mm2。供电方案二中使用8片LDO芯片,总布局面积为640 mm2。供电方案二版图设计时电源芯片减少12片,布局面积减小960 mm2,缩小了60%。第二种方案与第一种方案相比具有明显优势,可充分利用电源芯片的供电能力,在考虑减小不同工作频率ADC芯片可能因输入同一路电源造成信号干扰的前提下,减少了LDO的数量,降低了模块开发成本。

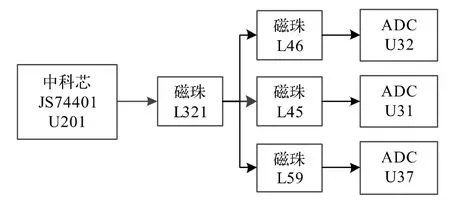

本文以一片2.5 V LDO为例进行详细分析,其电源方案如图2所示。2.5 V电源经U201输出,经磁珠L321后分成3路,经过磁珠L46、L45、L59后分别到达ADC U32、ADC U31、ADC U37。

图2 2.5 V电源方案

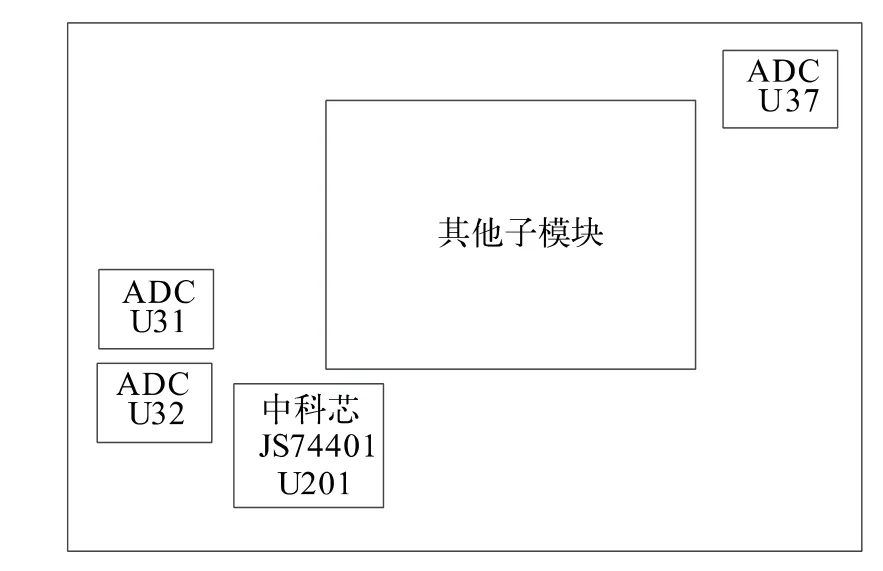

该模块进行布局设计后,一路2.5 V LDO电源布局布线设计如图3所示。因U31、U32芯片输出信号接口位于版图左下方,U37芯片输出信号接口位于版图右上角,故U201、U31、U32布局位置在版图左下角,U37位于版图右上角。

图3 2.5 V电源布局

3 仿真与优化

3.1 仿真

电阻性压降对于微小尺寸(微米级别及以下)的电源网络已不容忽略,故芯片内的静态IR压降已被广泛研究,但板级的静态IR压降并没有得到广泛关注。

对于功能模块中的电源尤其是模拟电源,在方案已定的情况下,后期设计主要关注电源完整性的阻抗、静态IR压降以及动态IR压降是否达到芯片要求。本文重点介绍通过静态IR压降的仿真与优化判断电源是否符合ADC芯片要求。

根据设计规范及经验对该模块的版图进行检查,发现该路LDO输出的3路2.5 V电源中的一路电源经过很长一段路径到达ADC芯片。该路2.5 V电源压降将比其他两路电源压降大,存在超出ADC芯片电源要求的风险。

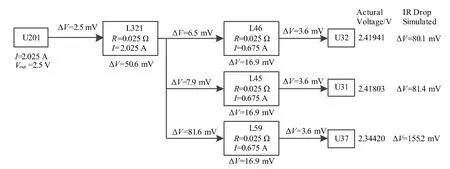

一路2.5 V LDO电源版图设计如图4所示,U201为LDO芯片,U31、U32、U37为ADC芯片。U201输出电压Vout为2.5 V,输出总电流为2.025 A,经过磁珠L321分成3路,分别给U31、U32、U37供电,每路电流典型值为0.675 A。对2.5 V电源U31、U32、U37 3个芯片的输入电压要求为2.44~2.56 V。

图4 2.5 V电源版图设计

本模块采用Power DC软件进行静态IR压降仿真,选用磁珠的直流电阻(Direct Current Resistance,DCR)最大值为0.025Ω,仿真采用磁珠DCR值为0.025Ω,经过每个器件的电流为I,ΔV为对应部分的电压差。仿真结果如图5所示,由仿真结果可以看出,U31、U32、U37 3个芯片接收到的电源电压分别为2.42 V、2.42 V、2.34 V。对比器件资料可知,该LDO输出的2.5 V电源均不满足ADC芯片的输入电源电压要求。

图5 静态IR压降仿真结果

3.2 优化

若ADC芯片输入电压大于芯片要求的最大电压,芯片发热量增大、性能指标受到影响。如果芯片输入电压超过最大输入电压而长时间工作,芯片寿命将降低,甚至造成烧片。相反,若ADC芯片输入电压小于芯片要求的最小电压,芯片将存在不能正常工作的风险,影响程序写入。结合公式U=IR分析解决该问题的方案,该2.5 V电源优化有3种方法。

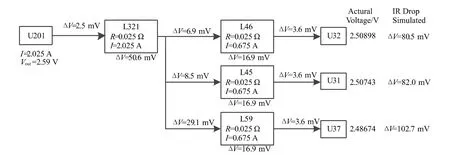

在第1种优化方案中,U31、U32、U37 3路在接收端的最大电源电压之差为0.07521 V,可考虑采用提高LDO输出电源电压的方法解决该问题,即将LDO芯片输出的电源电压由2.5 V提高为2.61 V。仿真结果如图6所示,由仿真结果可以看出,U31、U32、U37 3个芯片接收到的电源电压分别为2.53 V、2.52 V、2.45 V,均满足ADC芯片的输入电源电压要求。

图6 第1种优化方案仿真结果

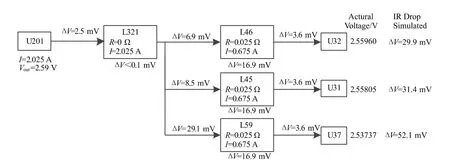

在第2种优化方案中,根据静态IR压降计算公式U=IR,将磁珠L321与L59之间的电源平面加宽至少1倍,它们之间的电源压降至少减少40.8 mV。U37与U32在输入端的电压之差为0.04 V。综上分析,电源平面优化后,可考虑采用提高LDO输出电源电压的方法解决该问题,即将LDO芯片输出电源电压由2.5 V提高为2.59 V。仿真后的结果如图7所示,由仿真结果可以看出,U31、U32、U37 3个芯片接收到的电源电压分别为2.50 V、2.50 V、2.48 V,均满足ADC芯片的输入电源电压要求;3个芯片接收到的电源电压差值为0.2 V,调试时可采用统一提高电源电压的方法来达到ADC芯片的输入电源电压要求。

图7 第2种优化方案仿真结果

第3种优化方案与以上2种方法不同,第3种方法考虑将磁珠L321去掉,则U31、U32、U37 3个芯片接收到的电源电压分别为2.47 V、2.47 V、2.39 V,U31、U32 2个芯片的输入电压可满足芯片输入电压要求,但U37芯片未能满足芯片输入电压要求。可考虑将磁珠L321与L59之间的电源平面加宽至少一倍,它们之间的静态IR压降至少减少40.8 mV,从而计算出U37的输入电压为2.43 V,此时可将LDO芯片输出2.5 V电压提高为2.52 V。仿真结果如图8所示,由以上仿真结果可以看出,U31、U32、U37 3个芯片接收到的电压分别为2.55 V、2.55 V、2.53 V,均满足ADC芯片的输入电压要求。

图8 第3种优化方案仿真结果

4 测试结果

本设计采用第2种优化方案后,回板测试U201输出电压为2.44 V,在U32、U31、U37 3个芯片输入端测得的电压分别为2.43 V、2.44 V、2.41 V。

经进一步测试,在磁珠L321前、后的电压均为2.44 V,即L321上产生的压降为0 V。在磁珠L46前、后的电压均为2.44 V、2.43 V,即L321上产生的压降为0.01 V。在磁珠L45、L59前、后测得的电压分别为2.43 V、2.42 V。实际测试中发现磁珠实际的DCR远小于其最大值25 mΩ,可忽略不计,所以该电源链路上产生的压降值比仿真结果值小。3个芯片接收到的电源电压差值为0.3 V,与仿真结果一致。实际应用该2.5 V电源时,可将U201输出电压调整为2.52 V,在U32、U31、U37 3个芯片输入端的电压分别可达到2.51 V、2.52 V、2.49 V。

5 结论

本文提供了一种高效的20片ADC芯片供电方案,同时通过仿真手段提前识别出其中一路LDO芯片输出的2.5 V电压在到达ADC芯片时未能达到ADC芯片输入的最小电压要求。结合静态压降公式,提供了3种优化方法,均可达到ADC芯片输入的最小电压要求。采用第2种优化方法,回板实测结果显示3个芯片接收到的电源电压差值为0.3 V,与仿真结果一致。综上可见,仿真可保证方案的完整性、可行性,大大提高模块调试、测试效率。