一种抗辐射LVDS驱动电路IP设计*

2022-03-03马艺珂汪逸垚花正勇殷亚楠周昕杰颜元凯

马艺珂,汪逸垚,姚 进,花正勇,殷亚楠,周昕杰,颜元凯

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

随着集成电路的持续发展,高速率宽带信道和高速互连信号的使用日益增多,传送的数据需求量愈来愈大,信号传输速率愈来愈快,近年乃至未来数十年,航空、航天、军事、电子通信等领域相关部门对灵活的高速率通信系统的应用量都会不断增长,低压差分信号(Low Voltage Differential Signaling,LVDS)作为一种低功耗、低误码率、低串扰和低辐射的差分信号技术得到了越来越广泛的应用[1]。

在航天飞行器运行的太空环境中存在诸多高能粒子,这部分高能粒子对在太空环境中使用的电子电路模块会产生多种多样的辐射,引起诸多次级效应,导致电路性能降低,甚至引起逻辑功能误差乃至完全损坏,因此对于应用于太空环境的电子电路,在发射升空之前都要进行抗辐射加固设计[2]。本文通过改进LVDS驱动器的电路,设计了一种具有低温度漂移系数和抗辐射的带隙基准,可以保证电路在标准规定的范围内正常工作,还可以避免额外的抗辐射电路设计,降低成本,提高电路的抗辐照可靠性。

2 传统的LVDS电路结构

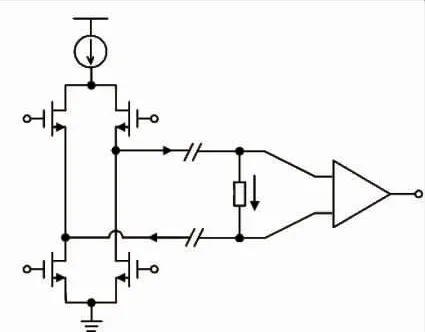

传统的LVDS接口电路由驱动器、传输线以及终端电阻和接收器组成(见图1)。LVDS驱动电路的功能是将数字电路处理过的数字信息转变为满足LVDS协议的差分信号。当Vin+端为高电平、Vin-端为低电平时,M2管子的栅控端为高电位,对称结构开启半边,M2管子开启,M1管子关断;M3管子的栅控端为高电位,对称结构开启半边,M3管子开启,M4管子关断。恒定电流源提供3.5 mA的稳定电流,输出端Out1与输出端Out2在芯片外部端接100Ω的电阻,这样M2管子、M3管子与外部端接的100Ω电阻形成完整的闭环电路,电流从输出端Out1流入输出端Out2,在外部端接电阻上产生350 mV的电压差。相反,当Vin+端为低电平、Vin-端为高电平,M1管子与M4管子开启,M2管子与M3管子关断,电流从输出端Out2流入输出端Out1,在外部端接电阻上产生350 mV的低电压差。共模电平反馈端采用2个大小一致的电阻来对驱动器进行反馈,使得最终共模电平约为1.2 V[3],这样,驱动器的输入TTL信号就可以转换成满足LVDS协议标准的低压差分信号[4-6]。其中传输线可实现不同IC模块互联,实现一对一或者一对多的应用,以简单地将LVDS接收器理解为一个比较器,将350 mV摆幅的差分信号转变为数字电路所能处理的波形[7-8]。

图1 典型的LVDS系统

2.1 带隙基准电路改进设计

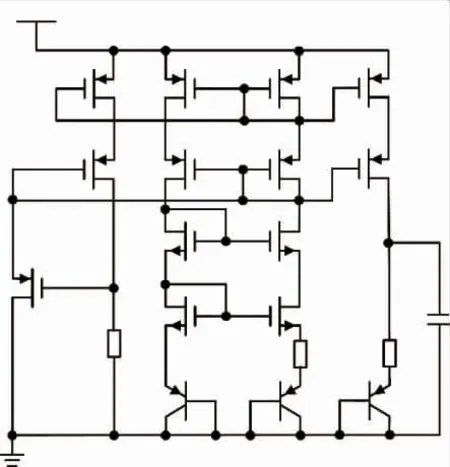

LVDS驱动电路中带隙基准源电路结构如图2所示。M1~M3与电阻Ron组成带隙基准电路的启动电路,该电路在电源上电过程中可以快速响应,促使电流镜电路脱离简并偏置点,电路正常工作后启动电路关闭。M4~M11组成共源共栅电流镜电路,M12和M13由前级提供偏置,通过调整双极型晶体管(Bipolar Junction Transistor,BJT),使其工作在不相同的电流密度环境下,可以实现BJT的基极—发射极电压的差值(ΔVbe)与绝对温度成正相关[9],再通过调整正温度系数电阻R1和R2的比值,最终可以使基准电压(Vref)在温度和电源电压波动时变化很小。当电压源电压下降到3 V或者更低时,在没有使用低开启电压器件的情况下,共源共栅电流镜的NMOS管将会处于线性区,影响电路正常工作。

图2 带隙基准电路源电路结构

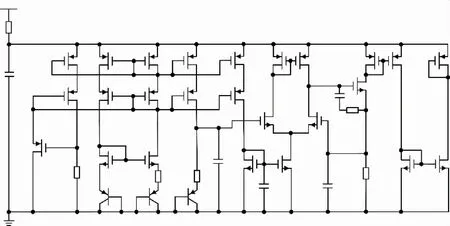

本文提出的带隙基准电路结构如图3所示,在不使用低开启电压器件的情况下依然能够在电路的电源电压低于3 V或者波动下正常工作。在电源端口增加Rf和Cf构成滤波电路,在电源输入端滤波;将原共源共栅电流镜电路结构中的NMOS管M8和M9省去,可以满足在电源电压较低的情况下电流镜中所有的MOS管都工作在饱和区且不影响电路原功能;由M16~M21管组成运算放大器,运放的正输入端接带隙基准电路输出的基准电压,运放采用单端输出,经过源跟随器由电阻Rz1反馈到运放的负输入端,形成负反馈,产生稳定的输出电压。由于M24管的栅压不随温度变化,流经M24管的电流也不随温度变化,流过M22管的电流为基准电流,M23、M25、M26和M27管镜像M22管的电流,为后级电路提供偏置电流。

图3 本文提出的带隙基准电路

2.2 驱动电路整体设计

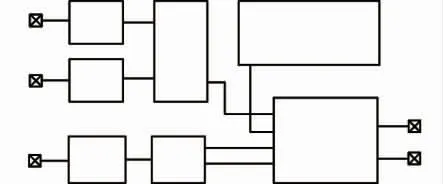

LVDS驱动电路的顶层结构如图4所示。G_IN模块的内部输入端口采用施密特触发器结构,增加了使能控制信号的迟滞效果。A_IN模块数据输入端口A为不确定状态时,LVDS驱动器输出端Y和Z输出高阻态,数据输入端口A为开路时,LVDS驱动器的数据输入端口A的电平将会被拉到地,防止输出错误信号。DATA IN模块将输入信号通过数字单元变成两路脉冲相反的方波信号控制LVDS输出端的4个NMOS开关管。DATA OUT模块中的共模电压反馈结构可以将LVDS驱动器的输出共模电压箝位在1.20 V。

图4 本文提出的驱动电路顶层结构

3 抗辐射加固设计

在空间辐射环境中,CMOS集成电路会遭到总剂量效应、单粒子闩锁和单粒子翻转效应的影响,造成LVDS驱动电路静态漏电流变大、工作时电路内部支路电流较大,甚至导致驱动电路内部元器件烧毁等现象[10-11],因此不仅要采用电路结构上的抗辐射加固技术,同时还要在版图设计上采用具有抗辐射功能的特殊结构[12-13]。

在电路结构中,带隙基准电压和基准电流易受高能粒子的影响产生较大的扰动,当单粒子注入到基准电压输出端的MOS管漏极时,会引起脉冲,影响后级栅控电压,造成MOS管的电流波动,实际设计时经过仿真单粒子脉冲轰击敏感节点,再根据输出端波动大小来确定在电路结构中增加适当的电容值进行抗辐射加固。LVDS驱动电路中的数字模块采用经过辐照试验验证的抗辐射单元进行替换,该工艺下的抗辐射单元库已经经过辐照试验验证,对总剂量效应、单粒子翻转以及单粒子闩锁均满足抗辐射性能指标。大尺寸器件在版图上采用环形栅结构,并在外围增加保护环。保护环可以吸收相邻MOS器件之间由于总剂量效应在场氧化层下产生的反型电荷,减小漏电。倒比例或小比例的器件在版图上采用大头条形栅结构,吸收由总剂量辐射下场氧反型产生的电荷,防止器件之间漏电。利用上述抗辐射版图加固结构,不但能够有效实现抗辐射总剂量效应加固,而且也可以使MOS器件的宽长比例调整更为灵活,可以设计成小比例器件,并且比环形栅器件结构占用的版图面积更小。

以上3种抗辐射加固电路和版图设计,目前已经在某型号宇航用抗辐射加固发射与接收集成电路产品中得到应用与验证,经粒子辐射试验检验,该集成电路性能指标都已达到抗辐射要求。

4 仿真结果

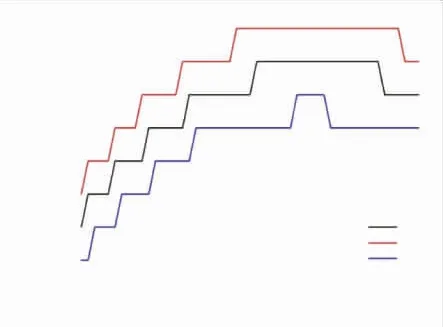

采用0.18μm CMOS工艺模型库进行Hspice仿真。LVDS驱动电路输出的共模电压如图5所示,在-55~125℃温度范围内,TT、FF、SS 3种MOS管工艺角下得到的仿真结果显示,驱动电路输出共模电压均满足标准规定。

图5 3个工艺角下基准电压随温度的变化曲线

驱动器电路内部运算放大器环路增益和相位裕度的仿真结果如图6所示,运放的环路增益最大为44.18 dB,当增益降为0 dB时,相位为85.4541°,此时对应的频率为14.678 MHz,仿真结果表明运算放大器性能指标满足设计需求。

图6 运算放大器的环路增益和相位裕度

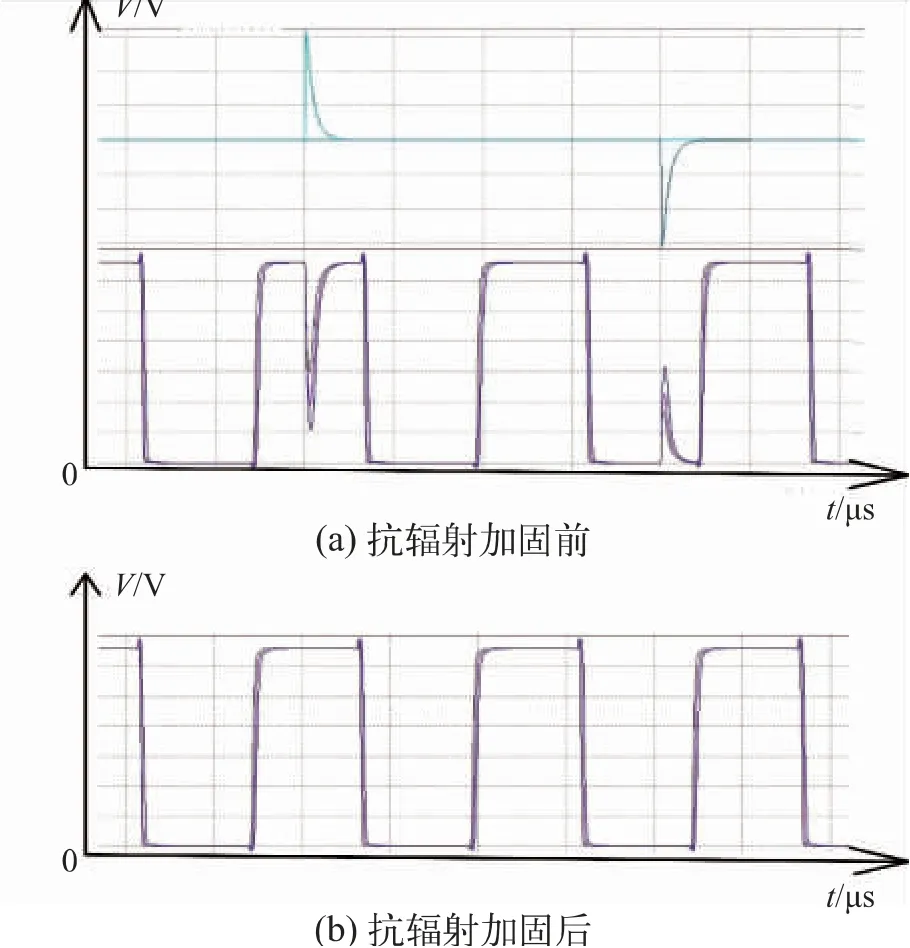

驱动器电路抗辐射加固技术前后的仿真结果如图7所示,可以看到,LVDS驱动器电路在进行抗辐射加固之前,当高能粒子穿过器件时,在其路径上激发出密度较高的电荷,使器件电学特性或工作状态产生扰动,造成该入射电路的节点产生尖脉冲或者位翻转,这种波动经传输、放大或诱发其他潜在的寄生效应,可引起驱动器输出的信号产生错误。采用本文提出的抗辐射加固技术之后,LVDS驱动器电路未受到单粒子的影响,输出结果正确。

图7 驱动器电路抗辐射加固前后仿真结果对比

5 结论

本文设计了一种具有抗辐射功能的LVDS驱动器电路,利用RC滤波电路减小电源波动的影响,采用改进的电流镜电路保证了低电源电压下电路的正常工作,用抗辐射单元库替换驱动电路的数字单元,模拟电路采用版图上抗辐射加固技术和电路敏感节点加固技术,减小了电路结构上的改动,降低了成本,提高了电路的可靠性,不仅电路版图面积未产生大规模增加,而且加固后的电路传输速率等性能未发生退化,从而更好地满足航空航天领域对抗辐射LVDS驱动电路的要求,为抗辐射IP的设计提供技术支撑。