考虑寄生参数影响的芯片RC-HBM静电测试模型

2022-03-02熊素琴李求洋肖志强

熊素琴,李求洋,肖志强

考虑寄生参数影响的芯片RC-HBM静电测试模型

熊素琴1,李求洋1,肖志强2

(1.中国电力科学研究院有限公司,北京 100192;2.湖南大学电气与信息工程学院,湖南 长沙 410082)

采用常规的人体模型(Human Body Model, HBM)进行静电释放(Electro-Static Discharge, ESD)测试时往往容易受到寄生参数的影响,使得电源芯片抗静电能力测量值与实际抗静电能力存在偏差,导致劣质产品通过HBM ESD测试,影响电源芯片产品良品率的提升。为此,提出了一种RC-HBM模型,通过引入RC并联支路,校正因寄生参数引起的静电放电电流的偏差,满足电源芯片静电可靠性测试的要求。首先阐述了静电对电源芯片的损坏机理。其次,分析了寄生参数对ESD电流的影响,阐述了常规HBM ESD测试的局限性。并提出了一种新型的RC-HBM模型,给出了RC并联支路参数的设计依据。最后,通过批量实验验证了所提RC-HBM模型的准确性和合理性。

电源芯片;HBM模型;ESD;寄生参数;静电放电电流

0 引言

电源芯片是发电厂、变电站中众多电子设备中不可或缺的能量转换部分,尤其是控制、保护和自动化等装置,对电源芯片供电质量要求更高[1-5]。电源芯片的质量和可靠性在很大程度上影响着整个设备的可靠性、失效率及维修率[6-8]。电源芯片作为许多设备内部核心元器件,其失效常常导致控制、继电保护等装置失效,从而导致设备瘫痪,给电力系统带来重大损失,威胁电网安全[9-12]。因而,可靠的电源芯片对电网来说至关重要。

然而,随着芯片制造工艺的不断提升,电源芯片的尺寸越来越小,栅氧化层也越来越薄[13],使得电源芯片产品在生产、运输、使用等过程中越来越容易受到静电的损坏。据报道,全球芯片行业每年由于静电问题造成的损失高达50亿美元[14]。因而,电源芯片在设计时多采用ESD静电防护电路来保护芯片[15]。同时,芯片出厂时还需进行ESD可靠性测试,确保芯片抗静电能力达到指标要求[16]。

目前对于芯片ESD测试主要通过人体放电模型、机器放电模型、充电器件放电模型来模拟芯片受到不同类型的静电打击[17-19]。其中,人体模型放电是引起电源芯片失效的重要原因,为便于芯片静电可靠性测试,国际电子工业以及国际电工委员会对人体模型制定了相关的工业标准(EIA/JEDEC STANDARD、IEC/TC 47)[20]。但实际上在进行人体模型静电测试时,往往由于测试电路中的寄生参数造成测试设备放电波形偏离标准波形,导致芯片抗静电能力实测值与实际值存在偏差,造成部分芯片产品在未满足静电指标的情况下通过静电释放测试,严重影响芯片产品良品率的提升[21]。

针对此问题,文献[22]建立了含寄生参数的HBM等效电路模型,给出了寄生参数的取值范围。文献[23]建立了含寄生参数的四阶HBM 模型数学模型,从时域的角度分析了寄生参数对ESD测试的影响。文献[24]建立了含寄生参数下的HBM模型的频率模型,从频域的角度分析了寄生参数对HBM模型测试结果的影响。但上述研究仅分析了寄生参数对ESD测试结果的影响,并未给出消除寄生参数影响的方法。此外,电子工业联盟协会提出了改进的HBM ESD测试标准,即JEDEC JESD22-A114_B[25],汽车电子协会也提出了AEC-Q100-002测试标准等[26],但实际的寄生参数与测量电路密切相关,该类标准仍无法完全解决寄生效应带来的影响。

为此,本文提出了一种RC-HBM模型,通过引入RC并联支路,消除HBM模型寄生参数带来的影响,使得芯片静电测试结果更加精确。本文首先阐述了静电释放对电源芯片损伤的机理;其次分析了常规HBM模型的局限性,阐述了RC-HBM模型的基本原理,并给出了RC的设计依据;最后通过批量实验验证了本文所提RC-HBM模型的准确性和合理性。

1 电源芯片静电损伤的原理

静电对电源芯片的损坏主要可分为两种:一种是强电场导致芯片栅氧击穿或MOS管电容击穿,即电失效;另一种是电流发热导致多晶电阻或PN结区硅烧毁、金属间电弧等,即热致失效。电源芯片多为开关电源,转化效率可达到90%以上,但其多采用MOS器件进行电源变换,容易受到静电损伤而失效。

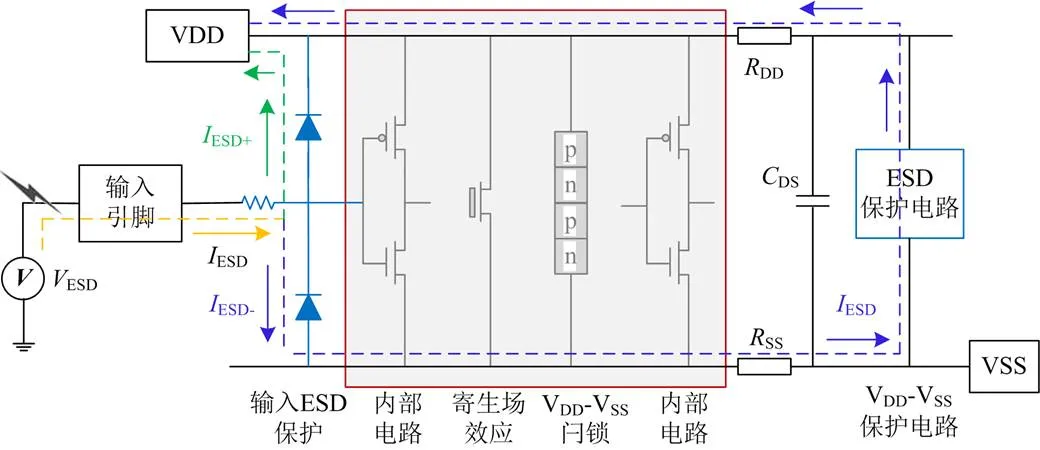

静电放电可能出现在电源芯片的任意两只管脚之间,当ESD发生在不相干的两支管脚之间时,静电放电电流会先经芯片进入VDD/VSS电源管脚,再由VDD/VSS电源管脚进入另一支管脚。如图1所示为在ESD保护电路作用下,静电释放电流通过芯片I/O输入管脚进入,从VDD电源管脚流出的过程。

图1 芯片输入管脚对VDD静电放电电流通道

图1中电源芯片包括输入ESD保护电路、芯片内部电路、VDD-VSSESD保护电路等。当静电积累的电荷为负电荷时,负电荷经输入管脚、输入ESD保护电路、DD-SSESD保护电路流入VDD电源管脚,形成ESD电流ESD-N(实际方向为VDD流向输入管脚);当所积累电荷为正电荷时,形成的ESD电流ESD-P直接从输入ESD电路流向VDD电源管脚。当静电释放通道按照上述两种方式流过芯片时,在ESD保护电路中形成放电回路,将不会造成芯片损坏。但实际上ESD保护电路存在损坏或未及时响应的情况,此时ESD电流可能流入芯片内部,引起芯片损伤,如图2所示。

图2 输入管脚对VDD静电放电电流通道(经芯片内部)

图2中,当ESD保护电路失效或未及时响应时,ESD电流ESD将经芯片内部电路流入VDD电源管脚,从而造成芯片内部发热或电击穿,引起芯片损伤。

因此,当静电电流未及时通过ESD保护电路进行泄放而流入芯片内部时将造成芯片损伤,导致芯片功能失效。

2 RC-HBM模型ESD测试原理分析

本节建立了常规HBM模型测试电路的数学模型,阐述了常规HBM模型测试的局限性,并从时域角度分析了寄生参数对HBM ESD测试结果的影响。

2.1 基于HBM模型的ESD测试局限性

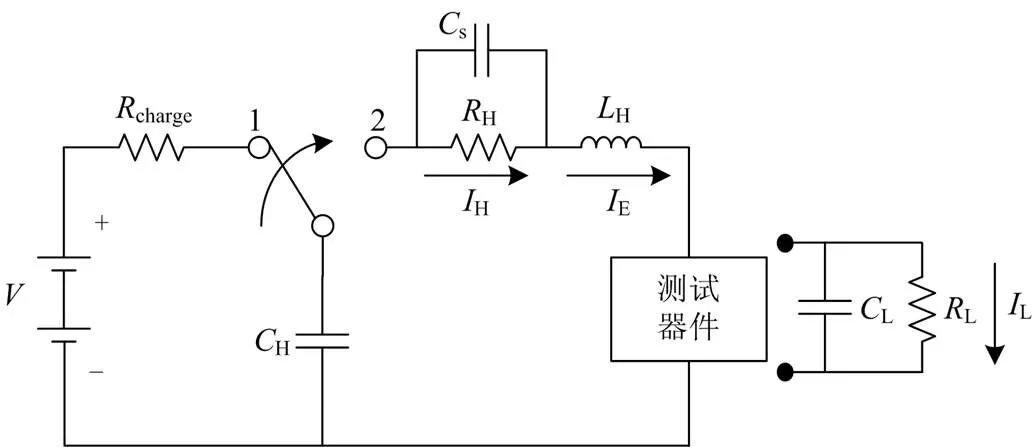

图3为常规HBM模型等效电路,用于模拟人体积累电荷后,通过直接接触的方式将电荷传递至芯片管脚的过程。其中,为高压脉冲发生器,charge为充电电阻,H为人体等效电容,约100 pF,H为人体等效放电电阻,约为1.5 kΩ,L为测试板和测试器件的寄生电容,L为被测器件等效电阻,H为人体等效放电电阻。当开关处于1时,高压脉冲发生器通过charge给人体等效电容H充电;当开关处于2时,人体积累的静电电荷通过H向测试器件放电。

图3 HBM模型等效电路

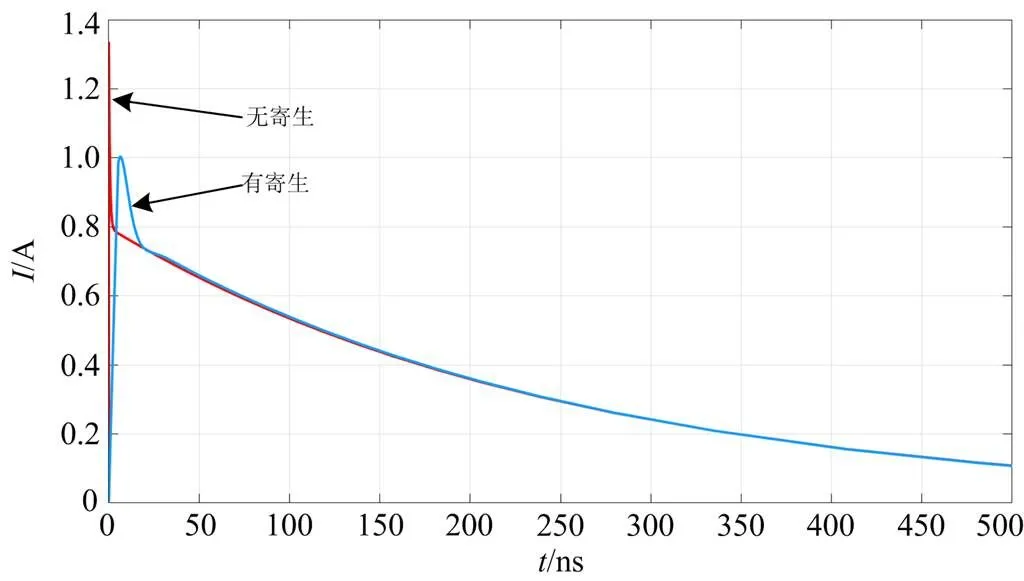

由于寄生参数的影响,采用常规HBM模型进行测试往往与实际测试标准存在偏差。图4为考虑寄生参数的HBM仿真对比图,图中红色曲线为标准的HBM ESD放电曲线(无寄生参数影响),静电放电电流的峰值达1.33 A,蓝色曲线为实际ESD测试电路中(有寄生参数)ESD放电曲线,静电释放放电峰值出现明显下降,放电波形偏离标准波形。

图4 有无寄生参数对放电电流的影响

根据上述分析可知,由于实际电路中寄生参数的影响,测试的静电释放放电波形偏离标准的放电电流,这很可能导致ESD耐压能力未达标的芯片由于测试电路中寄生参数的影响而通过测试,使得劣质产品通过测试而进入市场,从而降低产品的良品率。

2.2 HBM模型寄生参数影响分析

图5为考虑寄生参数下的HBM模型等效电路。其中,H为寄生电感,s为与H互联的寄生杂散电容。

图5 含寄生参数的HBM模型等效电路

根据图5所示的HBM模型等效电路,可建立如式(1)所示微分方程组。

对上述方程组进行求解及化简可得HBM模型电流波形计算式,其表达式如式(2)。

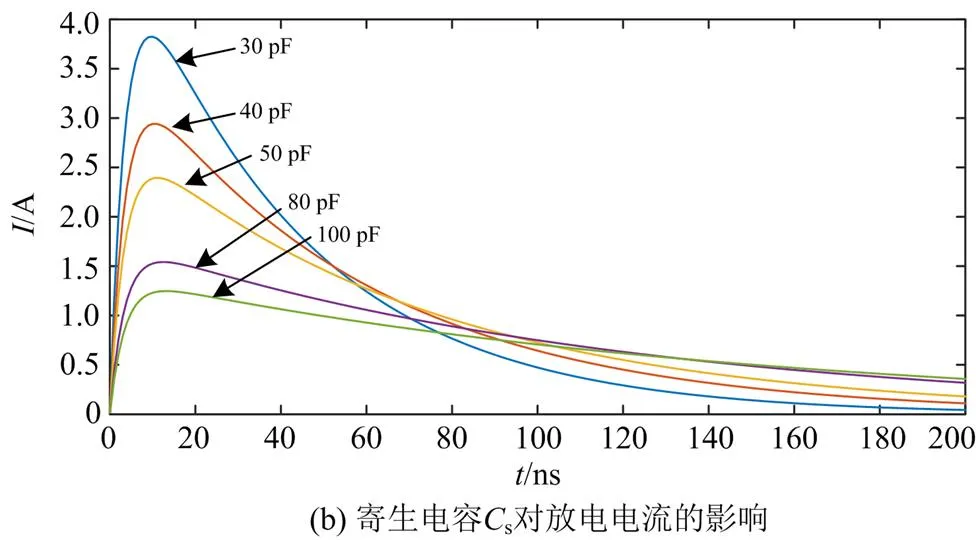

根据式(4)可知,当寄生电感H达到7.5 μH时,ESD放电上升时间约为10 ns,但由于电路中寄生参数的存在,实际的ESD放电上升时间与标准的时间存在偏差,放电电流波形也偏离标准波形。图6为考虑寄生电感H、寄生电容s影响下的放电电流曲线。

图6 寄生参数LH、Cs对放电电流的影响

如图6(a)所示,随着寄生电感H的值不断增大,HBM模型放电峰值电流逐渐减小,达到放电峰值电流的上升时间逐渐增加,但衰减时间几乎不变,不同寄生电感参数下的具体放电电流峰值和达到峰值的上升时间如表1所示。

表1 寄生电感LH对放电电流峰值、达到峰值时间的影响

如图6(b)所示,随着寄生电容s的值不断增大,HBM模型放电电流峰值逐渐减小,达到放电峰值电流的上升时间略微增加,衰减时间显著增加,具体数值如表2所示。

表2 寄生电容Cs对放电电流峰值、达到峰值时间的影响

根据上述分析可知,寄生电感和寄生电容均会影响ESD静电放电峰值电流,寄生电感对放电峰值电流的上升时间影响较大,对衰减时间影响较小,而寄生电容对达到放电峰值电流的上升时间影响较小,对衰减时间影响较大。

3 RC-HBM模型校正原理分析

为减少寄生参数对ESD放电电流的影响,本文提出了一种RC型HBM模型,通过引入RC并联支路来调节ESD放电电流峰值和放电时间,减少电路中寄生参数的影响,使ESD放电电流曲线逼近标准HBM ESD放电电流波形。

图7为本文所提RC-HBM模型,图中阴影部分为引进的RC并联补偿支路。在等效人体电容H放电时提供ESD放电电流支路,使得ESD放电电流曲线逼近标准的HBM 模型ESD放电电流曲线。

图7 改进HBM模型电路

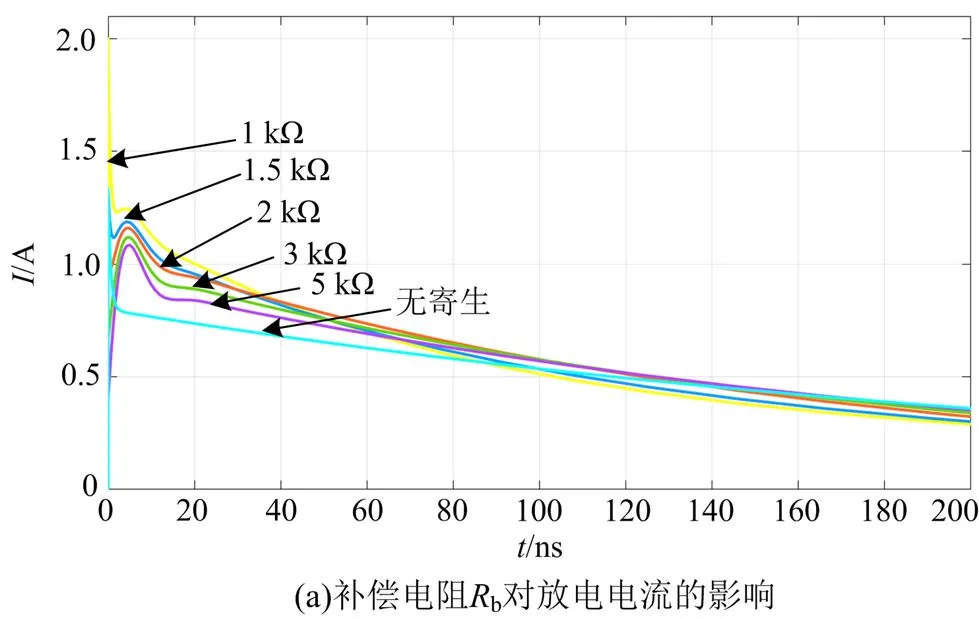

为研究并联RC支路不同参数对HBM模型下静电释放电流的影响,分别对不同补偿电阻b和补偿电容b的ESD放电电流峰值和放电时间进行仿真分析。图8为不同补偿电阻b和补偿电容b参数下的ESD电流仿真波形。

如图8(a)所示,随着补偿电阻b的不断增大,ESD电流峰值不断减少,当b接近1 500 Ω时,其放电电流峰值与标准ESD放电电流峰值较为接近,但存在较大的电流振荡,放电曲线与标准HBM ESD曲线还存在差距。表3为不同b参数下,ESD放电电流峰值具体数值。

表3 补偿器件Rb对放电电流峰值的影响

表4 补偿器件Cb对放电电流振荡峰值的影响

图8(b)为b固定在1 500 Ω,补偿电容b不断变化时的ESD电流波形图,随着补偿电容b不断增大,ESD电流振荡峰值也不断增大,ESD放电速度不断减慢。表4为不同b参数下,ESD放电电流振荡峰值具体数值。

由上述分析可知,可以通过不断调节b和b的取值来调节ESD电流峰值和放电时间,使校正后的ESD电流逐步逼近标准HBM模型ESD放电电流曲线,从而消除寄生参数对HBM静电可靠性测试的影响。如图8(b)所示,当b为1 500 Ω,b为1.5 pF时,ESD电流与标准HBM 模型ESD放电电流较为接近,可作为本文测试电路下的补偿参数。

4 电源芯片ESD测试对比实验

图9为本文采用的电源芯片ESD现场测试平台,脉冲发生器采用普锐马电子触摸式全智能脉冲群发生器(型号为EFT61004TB),输出电压0.2~ ± 4.8 kV,脉冲频率在1~1 200 kHz 连续可调。

图9 ESD现场试验平台

为验证本文所提RC型HBM模型的正确性,分别对一批电源芯片进行了ESD可靠性测试分析。图10为电源芯片HBM ESD静电可靠性测试方案,包括外观检测、电性测试、HBM模型静电测试等。

图10 静电可靠性双模式测试流程图

HBM模型静电可靠性测试具体测试步骤和内容如下:

① 外观检测:通过显微镜或者扫描设备判断电源芯片是否有外部损毁,筛选出正常芯片。

② 电性测试:检查芯片功能等是否正常,筛选出正常芯片。

③ 设置环境温度为25 ℃,湿度55% RH(饱和空气含水量)。

④ HBM静电测试:所有的芯片管脚对地打上±2 kV电压,对cc打上±2 kV电压,I/O对I/O打上±2 kV电压,循环3次,间隔1 min。

⑤ 与数据手册IV曲线进行对比,判断芯片是否损伤。

⑥ 再次通过外观检测和电性测试判断是否有损伤,从而完成芯片静电可靠性测试,生成静电可靠性测试报告。

同时,在HBM静电可靠性测试时,需要注意如下事项:

① 避免造成管脚间短路:电压测量或用示波器探头测试波形时,避免造成管脚间短路,最好在与管脚直接连通的外围印刷电路上进行测量。

② 勿轻断芯片的好坏:芯片绝大多数为直接耦合,一旦某一电路不正常,可能造成多处电压变化,这些变化不一定是由芯片损坏引起的;同时有些情况下测得芯片各管脚电压与正常值相符或接近,也不能说明芯片是完好的,因为部分软故障并不会直接引起芯片管脚直流电压的变化。

③ 芯片散热:芯片HBM静电测试时应保持散热良好,不允许不带散热器而处于大功率的状态下工作。

对于上述测试步骤④中的芯片管脚的静电测试,其管脚的静电测试共有ALL-DD,IO-SS,IO-IO三种组合,其中,ALL-DD表示所有管脚与VDD电源管脚的连接组合,IO-SS表示I/O端口管脚与VSS电源管脚连接组合,IO-IO则表示I/O端口对I/O端口管脚连接组合。表5为上述三种组合的具体连接方式,其中,D1、D2等表示DD管脚,S1、S2等表示SS管脚,a1、a2、b1、b2等是普通IO管脚;1代表对应管脚组合需要进行ESD测试。

如表5所示,在HBM模型测试中管脚组合的方式主要分为电源管脚和非电源管脚两种,其测试过程总结如下:

1) 对于电源管脚,当其接地时,芯片所有其他管脚依次接正负极性的静电电压进行放电测试。

2) 对于非电源管脚,依次接受正负极性的放电测试,芯片所有其他非被测的非电源管脚全部接地。

采用上述测试方案,分别对常规HBM模型和本文所提的RC-HBM模型进行对比测试。芯片样品数为1 000,分为A1、A2两批(各包含500个样品),其中样品A1采用常规HBM模型进行ESD测试,样品A2采用本文所提RC-HBM模型进行ESD测试,采用常规HBM模型样品A2再采用RC-HBM模型进行ESD测试,称为批次A3。测试结果如表6所示,A1批次基本可以通过ESD测试,仅2个样品未通过测试,A2批次有10个、A3批次有12个样品未通过测试。由此可说明,A1中部分芯片ESD耐压能力未达标,却通过了测试,降低了产品的良品率。

表5 HBM模型测试管脚组合

Table 5 Test pin combination of HBM model

表6 ESD测试结果

图11为IO-IO管脚组合下分别采用常规HBM模型和本文所提RC-HBM模型电源芯片内部放大图。如图11(a)所示,当采用常规HBM模型,被测芯片未出现明显损伤;而采用本文所提RC-HBM模型,被测芯片出现明显损伤,如图11(b)所示。

图12为All-VDD管脚组合下分别采用常规HBM模型和本文所提RC-HBM模型电源芯片图。如图12(a)所示,采用常规HBM模型,电源芯片并未损坏;而采用本文所提RC-HBM模型ESD测试,如图12(b)所示,被测芯片受损严重,被测芯片VDD和地管脚出现烧毁,说明部分芯片并未通过本文所提HBM模型ESD测试。

图11 电源芯片HBM ESD测试后芯片内部图

图12 电源芯片IO-IO管脚ESD测试图

可见,采用本文所提RC-HBM模型相比于常规HBM模型提高了HBM模型ESD放电电流,消除了ESD测试时寄生元件的影响,使得实际放电电流波形逼近标准的HBM 放电电流曲线,在一定程度上提高了芯片HBM模型ESD测试精度和可靠性,同时也说明了本文所提RC-HBM改进模型在实际ESD测试过程中更加精确和可靠。

5 总结

本文研究了电源芯片ESD测试的HBM模型,针对常规HBM模型测试电路因寄生参数对芯片ESD测试结果的影响,提出了一种可有效消除寄生参数影响的RC-HBM模型。

1) 阐述了静电对电源芯片的损坏机理,以芯片输入管脚对VDD的静电释放为例,分析了电源芯片静电保护与损伤的基本原理。

2) 详细阐述常规HBM模型的局限性,进一步分析了寄生参数对HBM模型ESD放电电流的影响;同时,提出了一种RC-HBM模型,可校正因寄生参数引起的ESD放电电流误差,提高静电可靠性测试精度。

3) 给出了一种电源芯片HBM模型ESD测试方法,并对常规HBM模型与RC-HBM模型进行了对比测试,通过批量实验验证了RC-HBM模型正确性。

[1] 潘晴宇.考虑分布式电源接入的变电站规划关键技术研究[J].电力系统保护与控制, 2021, 49(6): 98-104.

PAN Qingyu.Research on key technologies of substation planning considering distributed power access[J].Power System Protection and Control, 2021, 49(6): 98-104.

[2] 孙立明, 杨博.蓄电池/超导混合储能系统非线性鲁棒分数阶控制[J].电力系统保护与控制, 2020, 48(22): 76-83.

SUN Liming, YANG Bo.Nonlinear robust fractional-order control of battery/superconducting hybrid energy storage system[J].Power System Protection and Control, 2020, 48(22): 76-83.

[3] WANG F, WANG Q, FAN Z, et al.A coordinated control scheme to realize uninterruptible power supply for AC-side system in AC/DC hybrid distribution grid[C] // 2019 IEEE 8th International Conference on Advanced Power System Automation and Protection (APAP), October 21-24, 2019, Xi'an, China: 517-520.

[4] 陈喜峰, 任玮蒙, 武侠.适用于低频振荡分析的电力电子接口电源模型研究[J].电力科学与技术学报, 2020, 35(6): 61-67.

CHEN Xifeng, REN Weimeng, WU Xia.Research on power supply model with a power electronic interface for low frequency oscillation analysis[J].Journal of Electric Power Science and Technology, 2020, 35(6): 61-67.

[5] 李斌, 王晨阳, 何佳伟, 等.自适应限流型固态断路器的直流电源设计[J].电力系统自动化, 2020, 44(5): 30-37.

LI Bin, WANG Chenyang, HE Jiawei, et al.Design of DC power supply for self-adaptive current-limiting solid-state circuit breaker[J].Automation of Electric Power Systems, 2020, 44(5): 30-37.

[6] 宋文强.集成电路ESD静电防护设计及闩锁免疫研究[D].成都: 电子科技大学, 2020.

SONG Wenqiang.Research on ESD protection design and latch-up immunity of integrated circuits[D].Chengdu: University of Electronic Science and Technology, 2020.

[7] ZHANG B, HAO Z, BO Z.New development in relay protection for smart grid[J].Protection and Control of Modern Power Systems, 2016, 1(2): 121-127.

[8] 黄吉涛, 周媛奉, 梁飞, 等.以IR46电表测试为例的硬件检测综述[J].电力系统保护与控制, 2020, 48(3): 99-105.

HUANG Jitao, ZHOU Yuanfeng, LIANG Fei, et al.Overview of hardware detection taking IR46 meter test as an example[J].Power System Protection and Control, 2020, 48(3): 99-105.

[9] LI R, WONG P, WANG K, et al.Power quality enhancement and engineering application with high permeability distributed photovoltaic access to low-voltage distribution networks in Australia[J].Protection and Control of Modern Power Systems, 2020, 5(3): 183-189.

[10] 张蓬鹤, 薛阳, 张起豪.智能电能表用计量芯片失效分析研究[J].电子测试, 2013(17): 95-96.

ZHANG Penghe, XUE Yang, ZHANG Qihao.Research on failure analysis of metering chip for smart electric energy meter[J].Electronic Testing, 2013(17): 95-96.

[11] 赵东元, 胡楠, 傅靖, 等.提升新能源电力系统灵活性的中国实践及发展路径研究[J].电力系统保护与控制, 2020, 48(24): 1-8.

ZHAO Dongyuan, HU Nan, FU Jing, et al.Research on China's practice and development path to improve the flexibility of new energy power system[J].Power System Protection and Control, 2020, 48(24): 1-8.

[12] 陈磊, 何慧雯, 王磊, 等.基于限流器与断路器协调的混合直流输电系统故障隔离方法[J].电力系统保护与控制, 2020, 48(19): 119-127.

CHEN Lei, HE Huiwen, WANG Lei, et al.Hybrid DC transmission system fault isolation method based on coordination of current limiter and circuit breaker[J].Power System Protection and Control, 2020, 48(19): 119-127.

[13] 成周杰.双界面卡芯片静电放电防护设计研究[D].北京: 中国科学院大学, 2020.

CHENG Zhoujie.Research on the electrostatic discharge protection design of dual-interface card chips[D].Beijing: University of Chinese Academy of Sciences, 2020.

[14] 张启辰.静电放电对混合集成DC/DC变换器影响的研究[J].电子质量, 2020(8): 91-96.

ZHANG Qichen.Research on the influence of electrostatic discharge on hybrid integrated DC/DC converter[J].Electronic Quality, 2020(8): 91-96.

[15] 米丹, 周昕杰, 周晓彬.基于130nm SOI工艺数字ASIC ESD防护设计[J].半导体技术, 2021, 46(4): 279-285.

MI Dan, ZHOU Xinjie, ZHOU Xiaobin.Digital ASIC ESD protection design based on 130nm SOI process[J].Semiconductor Technology, 2021, 46(4): 279-285.

[16] 李盛.集成电路ESD 保护及其可靠性检测研究[D].西安: 西安电子科技大学, 2017.

LI Sheng.Research on integrated circuit ESD protection and reliability detection[D].Xi'an: Xidian University, 2017.

[17] Human body model electrostatic discharge test: AEC- Q100-002Rev-C[S].Automotive Electronics Council, 2001.

[18] Electrostatic discharge (ESD) sensitivity testing machine model (MM): JESD22-A115-A[S].JEDEC Solid State Technology Association, 1997.

[19] Standard test method for electrostatic discharge sensitivity testing-charged device model (CDM) component level: ESD STM5.3.1—1999[S].ESD Association, 1999.

[20] Mechanical and climatic test methods, part 26: electrostatic discharge susceptibility (ESD) testing-human body model (HBM)[S].Semiconductor Devices, 2013.

[21] 鹿祥宾, 陈燕宁, 张海峰, 等.DOE方法在ESD及LU测试故障定位方面的应用研究[J].固体电子学研究与进展, 2020, 40(3): 226-232.

LU Xiangbin, CHEN Yanning, ZHANG Haifeng, et al.Study on the application of DOE method in ESD and LU testing failure localization[J].Research & Progress of SSE, 2020, 40(3): 226-232.

[22]陈志钧.CMOS集成电路ESD保护技术的研究和设计[D].成都: 电子科技大学, 2012.

CHEN Zhijun.Research and design of CMOS integrated circuit ESD protection technology[D].Chengdu: University of Electronic Science and Technology of China, 2012.

[23] VERHAEGE K, ROUSSEL P J, GROCSENEKEN G, et al.Analysis of HBM testers and specifications using a 4"' order lumped element model[J].Quality and Reliability Engineering International, 1994, 10(4): 325-334.

[24] MALONEY T J.HBM tester waveforms, equivalent circuits, and socket capacitance[J].Microelectronics Reliability, 2013, 53(2): 184-189.

[25] ESD Association WG 5.1.Standard test method for electrostatic discharge sensitivity testing-human body model (HBM) component level: ESD STM5.1—2001[S].

[26] JEDEC Solid State Technology Association.Electrostatic discharge (ESD) sensitivity testing human body model (HBM): JESD22-A114-B[S].2000.

RC-HBM electrostatic test model of chip considering the influence of parasitic parameters

XIONG Suqin1, LI Qiuyang1, XIAO Zhiqiang2

(1.China Electric Power Research Institute Co., Ltd., Beijing 100192, China; 2.School of Electrical and Information Engineering, Hunan University, Changsha 410082, China)

When the conventional human body model (HBM) is used for electro-static discharge (ESD) testing, the measured value of the power chip's antistatic ability deviates from the actual antistatic ability because of a parasitic effect, resulting in inferior products passing the HBM ESD test.This affects the improvement of the yield rate of power chip products.To this end, an improved HBM model is proposed, one which corrects the deviation of the electrostatic discharge current caused by parasitic parameters by introducing an RC parallel branch to meet the requirements of the electrostatic reliability test of the power chip.First, the mechanism of how static electricity causes damage to the power chip is described.Secondly, the influence of parasitic parameters on the ESD current is analyzed, and the limitations of the conventional HBM ESD test are elaborated.Then a new RC-HBM model is proposed, and the design basis of the RC parallel branch parameters is presented.Finally, batch experiments verify the accuracy and rationality of the HBM model proposed.This work is supported by the Science and Technology Project of State Grid Corporation of China (No.5100-201946434A-0-0-00).

power chip; HBM model; ESD; parasitic parameters;electrostatic discharge current

10.19783/j.cnki.pspc.210450

2021-04-21;

2021-08-21

熊素琴(1979—),女,硕士研究生,高级工程师,研究方向为元器件测试分析技术;E-mail: 13778029@qq.com

李求洋(1988—),女,博士研究生,工程师,研究方向为传感量测技术;E-mail: 1243395671@qq.com

肖志强(1998—),男,通信作者,硕士研究生,研究方向为芯片ESD保护和DC-DC电源研制。E-mail: x1609680106@ 126.com

国网公司科技项目资助“继电保护装置成熟国产存储和隔离电源替代技术研究”(5100-201946434A-0-0-00)

(编辑 葛艳娜)