一种低信噪比下的宽带扩频信号捕获跟踪方法

2022-02-22梁中英张少侃

梁中英 张少侃

(广州海格通信集团股份有限公司,广东 广州 510663)

0 引言

扩频系统具备隐蔽性好、截获概率低和保密性强等特点,被广泛应用于卫星通信、移动通信、导航系统等领域[1]。扩频系统通常应用于极低信噪比下,所以接收端对扩频信号的捕获跟踪是系统的关键。扩频信号常用的捕获方法包括串行搜索法、并行码相位搜索法、并行频率搜索法等[2],随着卫星通信领域业务需求的增大,传统的扩频信号捕获方法已不适用于宽带系统。

在实际应用中,低信噪比下的多普勒频率偏移对扩频信号的捕获性能影响很大。为解决这一问题,通常需要通过额外的频偏估计和跟踪模块如锁频环、锁相环或其他的辅助算法等进行处理[3],增加了实现复杂度和硬件资源占用情况。而设备的低功耗需求越来越明显,在保证通信性能的前提下,降低算法复杂度和减少硬件资源至关重要。

该文针对短周期连续扩频信号提出了一种分段频域相关峰搜索联合频域定时跟踪的解决方案,并基于Xilinx的FPGA开发平台,采用并行处理方式进行了工程实现,具备实现简单、资源占用少和在极低信噪比下捕获跟踪性能稳定的优点。

1 系统模型分析

假设信道为加性高斯信道,则N个扩频周期的接收信号模型如公式(1)所示[4]。

式中:A为信号幅度;b(i)为发送的序列信息;N0为N个扩频周期包括的信息符号数;Ts为信息符号周期;T为扩频码周期;fc为信号的载波频率;θc为信号的载波初始相位;vn为高斯白噪声。

该文所描述的扩频系统模型存在连续导频序列,采用周期为128的短周期扩频码,用户序列扩频因子为2048,导频序列与用户序列同时传输。由于用户序列扩频因子为2048,带来了较高的扩频增益,因此对扩频周期为128的导频序列来说,工作在极低的信噪比下时,为了提升抗干扰和抗截获性能,系统通信指标要求为信噪比小于等于-33 dB。

2 扩频信号捕获跟踪实现方法

由于导频序列为连续信号,在系统中持续存在,因此该文设计了一个捕获机制,确保一定能够捕获到导频序列,且只需要运算一次。为解决接收端和发射端的频率偏差问题[5],需要设置定时同步模块,对最佳采样点和扩频序列的起始位置进行跟踪。

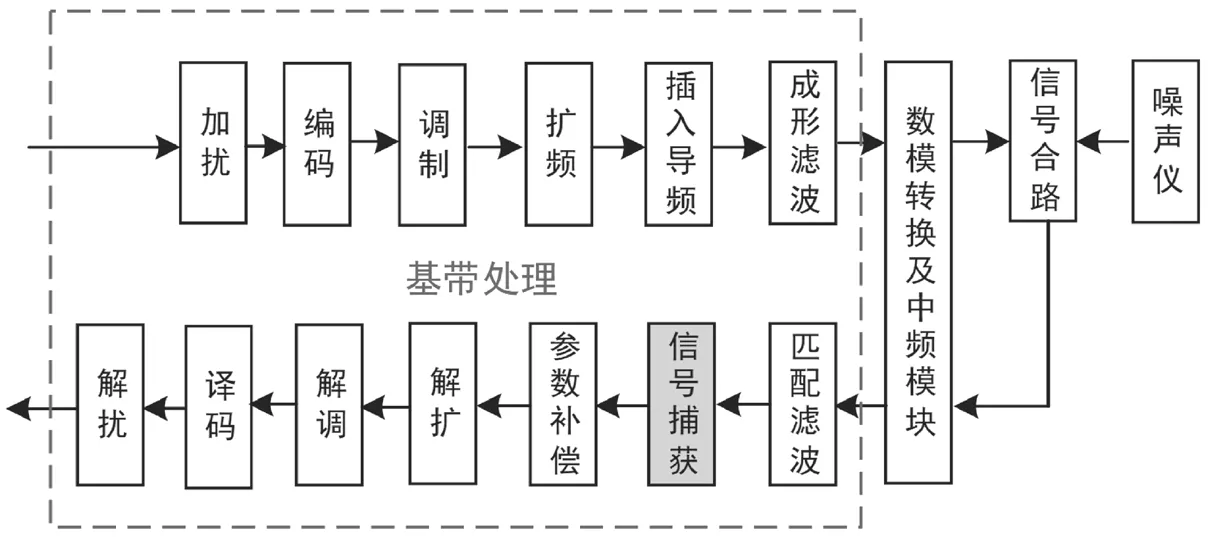

搭建如图1所示的验证系统进行测试验证,发送链路中的用户序列经过加扰、编码、调制和扩频等处理后与导频序列组合,经DAC转换为模拟信号,再通过中频模块发送出去。发射信号与噪声仪产生的高斯白噪声合路后送给接收端,接收端对信号进行捕获、解扩、解调、译码和解扰等处理。

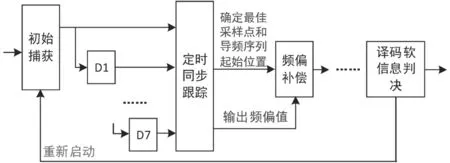

图1中的信号捕获是该文研究的重点,实现框图如图2所示。其中初始捕获没有异常情况时只在开机时运行一次,但为了保证系统稳定运行,仍需要设置重新启动控制机制。接收链路的译码模块可以计算出当前数据的软信息能量值,根据当前编码块长度和信噪比给出合适的门限值进行判断,如果低于门限值,则认为该帧数据存在大量误码,就需要重新启动初始捕获模块。

图1 验证系统框图

图2 扩频信号捕获实现框图

定时同步跟踪模式随系统实时运行,跟踪最佳采样点的同时计算出当前存在的频偏值,对信号进行频偏补偿,不需要额外的频率跟踪模块。

2.1 初始捕获

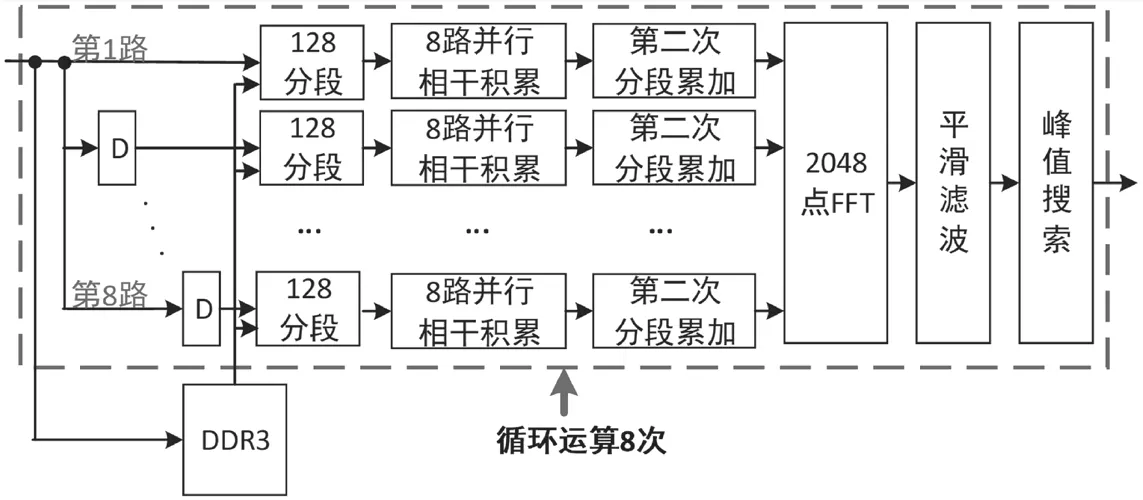

接收端采用高速并行ADC器件对56 Mcps的宽带信号进行4倍采样,初始捕获需要对采样的样本数据进行处理,由于导频序列的扩频周期为128,所以每次移动一个样点一共计算512次,一定能够搜索到导频序列的起始位置。为减少捕获时间,采用并行方式处理,但是全并行处理所占用的资源太多,综合考虑后,所有步骤都采用64路并行处理,计算8次可完成运算。采用多次分段频域运算,实现框图如图3所示。初始捕获的数据量比较大,需要存储在DDR3中,按需读取。由于系统运行在极低信噪比下,且扩频码周期较短,因此需要取多段数据进行相干积累和峰值检测。数据量增大会导致FFT的资源占用增多和延迟增加,因此对数据进行二次分段累加以解决这个问题,具体步骤如下:1)对接收到的信号以128为周期分段,与已知扩频码进行相关累加,每个分支调用8路并行相干积累器,共8个分支,实现64路并行处理。2)对上一步相干积累的结果每L段再进行二次累加,计算K次。3)对获得的K点数据进行补零后进行2048点FFT运算,计算信号能量。4)对信号能量进行平滑滤波,在计算结果中搜索最大值。5)循环运算8次,获得512个最大能量值,再对其进行最大值搜索,并进行门限判断。如果超过门限,则认为捕获到扩频信号。

图3 初始捕获实现框图

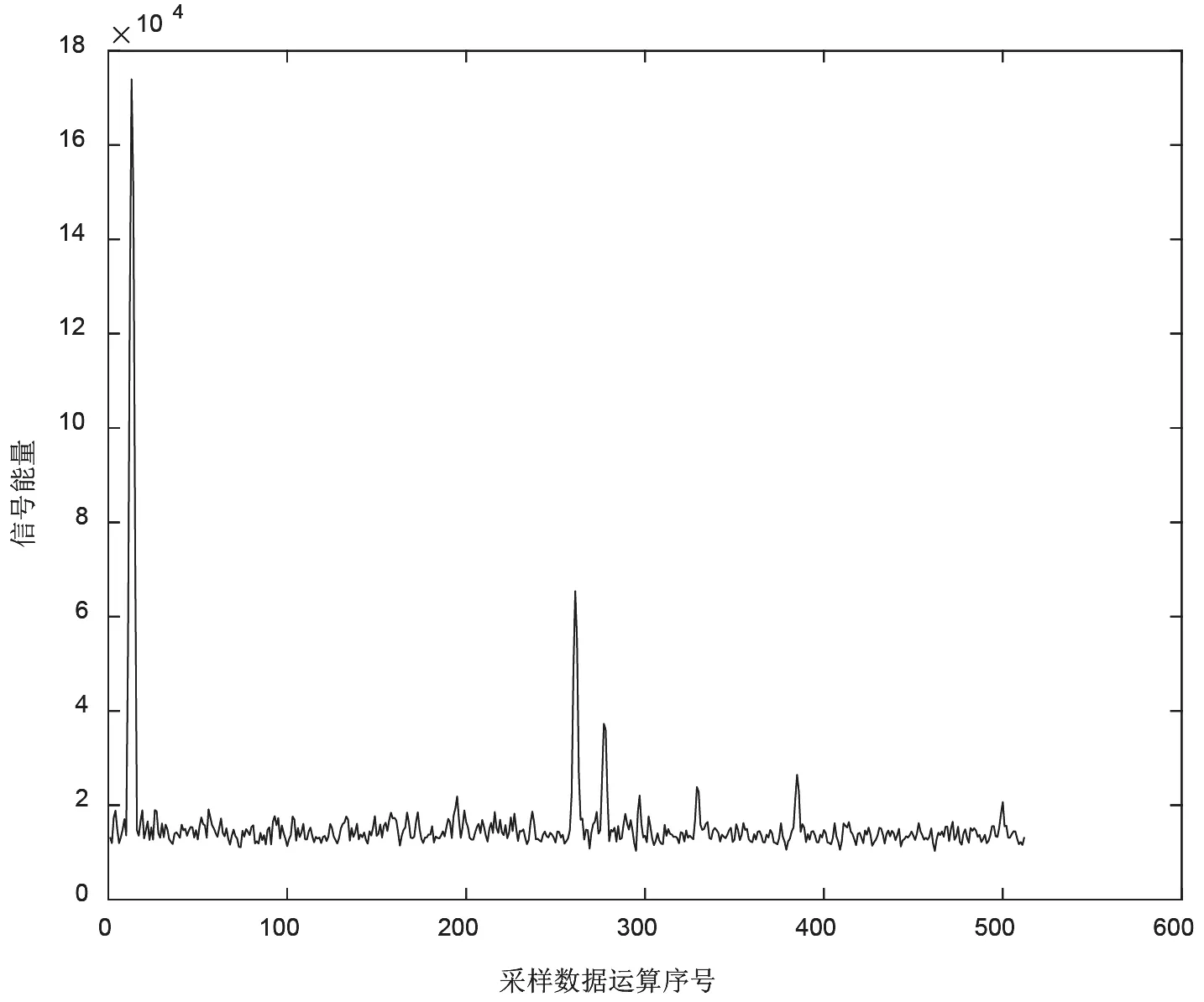

在信噪比-35 dB的情况下,L取值16,K取值1280,进行初始捕获性能仿真。由于采用16段分段运算,经过128扩频后的码片速率为56 Mcps,因此可容忍的频偏降为[-13.67 kHz,13.67 kHz],但仍能满足现有移动卫星通信终端的通信需求。在仿真时增加-13.67 kHz~+13.67 kHz的随机频偏,仿真结果如图4所示。图4给出了计算512次的信号能量值,从图4中可以看出峰值非常明显,频偏对该方案影响不明显。

图4 初始捕获仿真图

2.2 定时同步跟踪

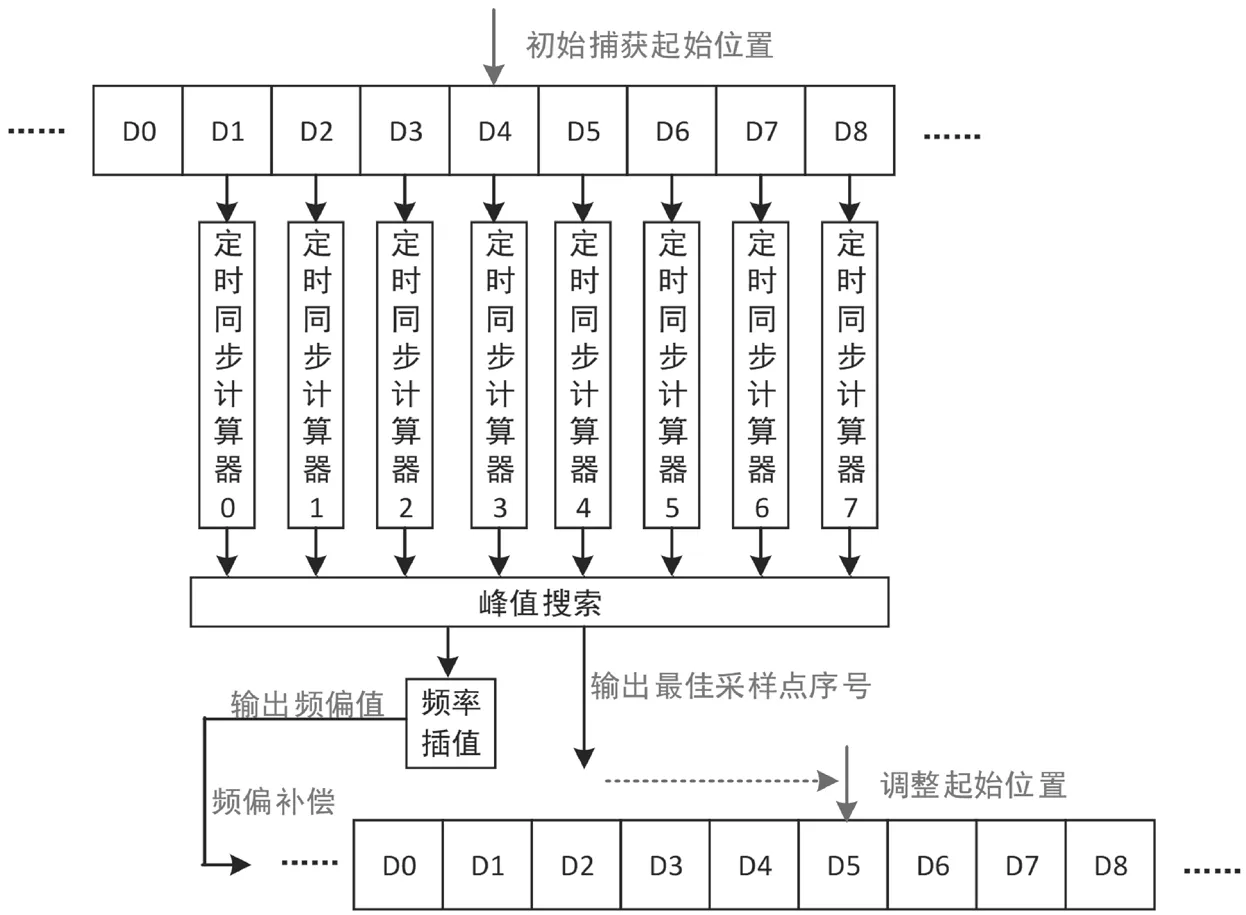

在初始捕获获得导频序列的起始位置后,考虑捕获时间、系统收发两端存在的频率偏差,同时考虑应用在移动终端时带来的多普勒偏移需要进行定时同步跟踪,实时调整最佳采样点的位置,以保证后续的解调性能[6]。实现框图如图5所示。

图5 定时跟踪实现框图

接收端对信号进行4倍采样,即1个符号包括4个样本数据。为了防止初始捕获采样点偏差,需要将定时同步计算的样点前移3个样点,以保证不会偏差1个符号。

取2个符号共8个样点分支进行并行分段频域计算,搜索出最佳采样点位置,每个定时同步计算器的计算步骤与初始捕获相同,如图3的一路分支所示,区别在于只计算8次,不需要计算512次。

搜索获得最大能量分支数后,按照该分支最大能量对应的2048点FFT横坐标序号,将其换算为频率值,进行频率插值,获得频偏结果。频率插值的基本思想是在利用基带去调制信号频谱图峰值并进行频偏粗估计的基础上,根据三次样条插值公式,利用峰值及其左、右2条谱线的幅度进行细估[7]。

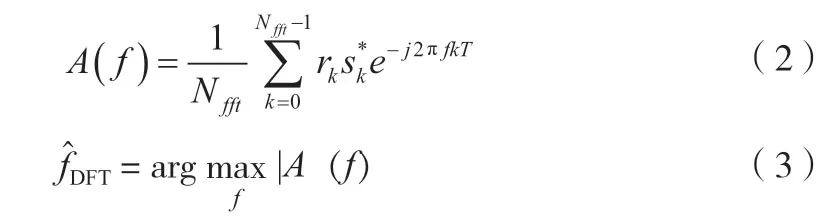

DFT频域估计算法如公式(2)所示,频率估计公式如公式(3)所示。

式中:Nfft为DFT变换点数;为所要估计的频偏值。

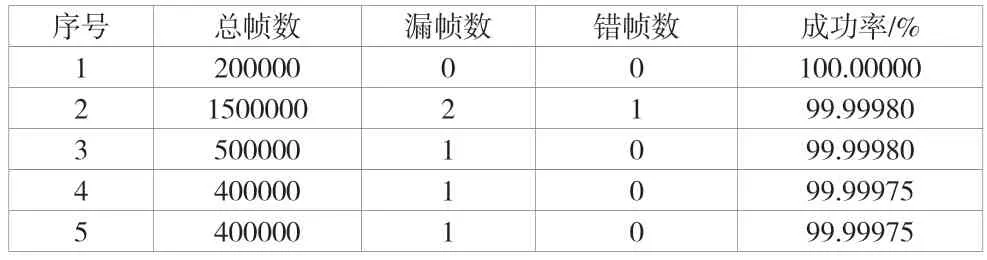

三次样条插值算法的频域频偏估计算法的具体步骤如下。1)对接收到的基带去调制信号进行快速傅里叶变换,找到频域峰值坐标点(km,A(km))及其左、右2点(km-1,A(km-1))与(km+1,A(km+1))。2)判断A(km-1)与A(km+1)的大小,如果A(km-1)>A(km+1),则转入步骤);如果A(km-1) 计算出频偏值后,将其补偿到捕获到的信号上,需要注意根据处理时延调整导频序列的起始位置。 定时同步跟踪模块需要给出128导频的起始位置和最佳采样点的指示位置。其中128导频起始位置用于简化用户序列的扩频码起始位置搜索运算,由于2048是128的16倍,因此利用此信息只需要进行16次搜索就可以找到2048扩频码的起始位置,进而直接进行解扩,后续进行跟踪,与导频序列同样需要保留重新启动的控制机制。最佳采样点的指示位置用于用户数据帧的帧头捕获,由于采样数据为1个符号4个样本数,因此直接利用最佳采样点这一路样本数据进行帧头捕获运算,降低了4倍运算量。 对验证该实现方法的硬件平台,该文选择Xilinx型号为XC7K410T的FPGA,并结合型号为MT41K256M16TW的DDR3芯片进行实现,AD芯片选用AD9680。 由于运算数据量较大,如果存储在FPGA内部的Block RAM中,资源占用太多,功耗太大,因此选择外挂DDR3作为初始捕获模块中的数据存储单元,设计支持并行128位数据在200 MHz时钟下的快速数据读取。DDR3接口采用FPGA内部的IP核MIG和AXI控制器实现。 为降低使用资源,根据初始捕获模块只工作一次的特性,后续定时同步跟踪模块复用初始捕获模块的资源,对资源占用最多的BRAM缓存组与FFT IP核进行复用。最终XC7K410T中的LUT占用9%,BRAM占用10%左右,乘法器占用1%,占用的资源非常少。在信噪比-35 dB的条件下,在图1所示的验证系统中进行测试验证,捕获成功率结果见表1,频偏估计偏差结果见表2。从2个表的实测结果可以看出漏帧率为10-6,错帧率为10-7,频偏估计偏差在10Hz以内,满足系统性能指标要求。 表1 捕获成功率 表2 频偏估计偏差 宽带扩频信号运算量大,速率高,通常采用并行频域处理,但硬件实现资源消耗太大。该文提出了一种抗频偏的分段频域并行捕获及跟踪方法,不需要额外的频偏估计模块。通过工程实际验证,该方法可以在极低信噪比下稳定可靠工作,实现简单且资源只占用了中规模FPGA K410T的10%,具有实际应用价值。3 工程实现

4 结语