一种报文离散性可控的标准数字功率源

2022-02-18李恺雷浩楠卜文彬谭海波黄红桥李红斌

李恺,雷浩楠,卜文彬,谭海波,黄红桥,李红斌

(1. 国网湖南省电力有限公司供电服务中心(计量中心)智能电气量测与应用技术湖南省重点实验室,长沙 410001;2. 华中科技大学 电气与电子工程学院, 武汉 430074)

0 引 言

随着数字化电能计量的快速发展,对数字化电能计量设备的要求也越来越高。数字化电能表作为数字化计量中贸易结算的关键设备,其准确性、可靠性直接关系到电能计量的公平性[1-7]。为保证数字化电能表的性能,必须对其进行严格的校验。

标准数字功率源是校验数字化电能表的关键设备,按照GB/T 17215.303-2013 《交流电测量设备 特殊要求 第三部分:数字化电能表》、DL/T 1955-2018 《计量用合并单元测试仪通用技术条件》等标准,标准数字功率源除了需要满足电压电流等基本影响量校验功能之外,还需要满足采样频率、采样值数据丢失等特殊影响量要求[8-9],特别是标准数字功率源需要能够模拟现场特殊工况下的各种采样值数据丢失,即应满足能够产生随机性报文数据丢失(以下简称“丢包”)的要求[10]。

现在许多企业和高校对标准数字功率源进行了研究,并研制出了能够定量模拟功率波动功能的数字功率源,其报文发布时间离散度降低至500 ns以内,但在丢包的随机性上仍存在不足[11-13]。

针对上述问题,根据相关国家及行业标准提出了一种报文离散性可控的数字功率源方案,通过基于混沌映射的随机序列生成算法和高性能光口以太网芯片相结合,既保证了报文数据丢失的随机性的要求,也满足了报文发布时间离散值可控的要求。测试结果表明,所研制的数字功率源生成的随机序列信息熵较大,丢包概率可控;报文发布时间离散值最低降至20 ns,最大离散值不超过200 ns。

1 随机性报文数据丢失的实现原理

1.1 传统硬件随机数生成方法

标准GB/T 17215.303-2013《交流电测量设备 特殊要求 第三部分:数字化电能表》中明确规定数字化电能表的校验项目涉及丢包试验以及异常事件通信试验,这要求数字功率源必须能够产生随机报文数据丢失,且丢包概率可控。

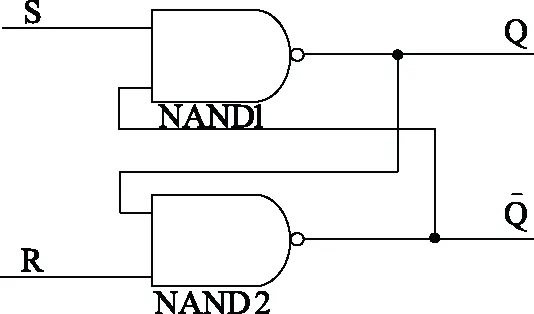

传统数字功率源随机性报文数据丢失的生成方法基于FPGA本身所拥有的特性,通过人为的逻辑编程使得FPGA内部产生竞争冒险,根据该现象的不确定性生成相应的随机序列,以此控制报文数据随机丢失,RS触发器为硬件随机数产生的基本元(见图1)。

图1 RS触发器Fig.1 RS trigger

当S、R同时为0,RS触发器输出稳定为(Q, ¯Q)=(1,1),当S与R同时置1时,触发器进入亚稳态,输出量Q具有随机性,取决于与非门的瞬时电平及其内部的噪声。故而每当系统需要随机数时,先把S、R同时置0,再将S、R同时置1产生随机数。由于内部电路相互关联,使用竞争冒险等不利条件产生随机数可能会使FPGA的状态机跑飞,且同时利用多个与非门电路增加了FPGA的功耗。此外,FPGA内部的布局布线通过编译已经确定,这种依靠逻辑竞争产生的随机数在时间上的概率分布不均(相关系数大于0.3),统计上无法认定其具有良好的随机性。

1.2 基于混沌映射的伪随机序列产生算法

混沌映射所构成的信源是等概率无记忆信源, 满足随机数产生器条件,由于混沌映射体现出随机性的实质是由初始值的精度有限性所提供的,所以可以构建基于随机种子方式实现随机数产生器[14-15]。

具体方案如下:首先FPGA上电时即在内部生成内部循环计时器,由0计数至255,当接收到关于随机数控制指令时,循环计数器停止,取此时记录的数值作为随机序列生成的种子(FPGA的主控时钟频率为50 MHz,循环计数一个周期所用的时间为167 ms,而接收随机数控制命令的时间远超167 ms,可以认为种子在0~255的范围内服从随机分布),再根据选取的种子,通过常用的混沌映射生成混沌随机序列。

一般来说,当系统满足式(1)所示的条件时,生成的系统为混沌系统:

(1)

式中f(x)为U上的连续函数;U为任意闭合区间,且不包含周期点。

常见的混沌序列映射方式有以下四种[16-18]:

(1)Logistic映射

xn+1=kxn(1-xn)

(2)

当3.5996≤k≤4时,Logistic映射满足混沌映射条件。

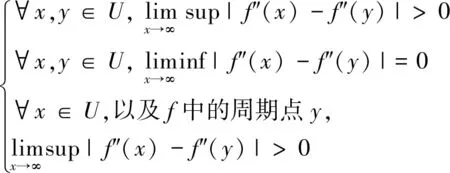

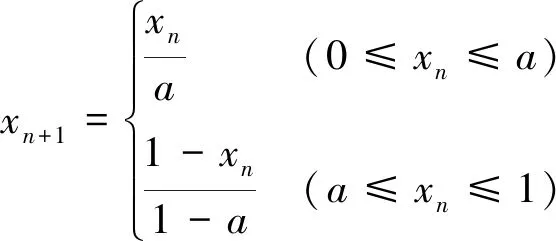

(2)Tent映射

(3)

当初始值x0∈[0,1]时,该序列映射出的xn∈[0,1],此时若xn经过有限次数据迭代,就会进入混沌状态。

(3)Chebyshev映射

xn+1=cos(k×arcos(xn))

(4)

当k≥2时,Chebyshev映射进入混沌状态。

(4)改进型Logistic映射

xn+1=1-k×xn×xn

(5)

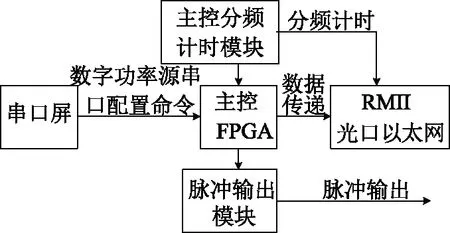

当1.4 其中Tent映射的映射函数本身需要分段,且涉及除法,对于FPGA硬件计算能力要求较高,需要较多的计算资源,不利于计算实时性。 当输出序列的长度N=10 000时,改进Logistic映射、Logistic映射以及Chebyshev映射的信息熵分别为12.165 5、12.141 6、12.150 5,因此采用改进Logistic映射作为混沌序列产生的映射算法。quartus中有专门针对乘法的ip核,只需循环调用即可生成混沌序列,根据浮点数的计算法则,丢包的概率为: (6) 式中k为概率线。系统概率可控,此外,每次配置丢包概率时,由于种子会发生变化,整个混沌序列也会随之改变。 基于FPGA自身特性以及quartus计算资源设计的随机数产生算法,不会产生竞争与冒险等不利因素,且不会因为误码而进入循环态,在随机概率可控的情况下,生成的伪随机序列熵值较大。 通过FPGA配置光口以太网芯片输出IEC 61850-9-2序列,同时将芯片配置为时间离散度最小的RMII接口输出,保证报文发布时间离散度可控。数字功率源主要结构如图2所示。 图2 标准数字功率源主要结构Fig.2 Main structure of standard digital power source 标准数字功率源主控通信部分通过串口屏配置功率源生成相应的输出波形,采用某公司生产的EP4CE15F17C8作为主控FPGA芯片,采用RS232作为主控芯片与控制界面的通信媒介,并通过50 MHz温补晶振配置计时模块实时测量光口以太网的包离散度,采用兼容IEEE.802.3以太网协议的物理层芯片DP83848IFVS作为光口以太网的控制芯片,将FPGA温补晶振的输出接入芯片的时钟控制管脚,并通过50 MHz的RMII接口传输IEC 61850-9-2数据,速率可达100 Mbps,进一步减小报文发布时间离散度误差。 光口以太网DP83848IFVS芯片通过RMII的接口实现芯片的上电初始化,同时实现主控与PHY之间的数据通信,RMII接口的基本通信方式如图3所示。 图3 通信接口Fig.3 Communication interface RMII数据传输通信线为RXD[1:0],TXD[1:0],2路信号并行传输,数据控制时钟为CLK_REF,数据上升沿有效,时钟频率为50 MHz,因此RMII接口的通信速率为100 Mbps,数据以低位在后,高位在前的方式传输,与FPGA刚好相反,FPGA读取波表数据后需先经过倒位赋值再输入RMII接口中。TX_EN,RX_ER为发送接收使能信号,发送数据时需先主动拉低TX_EN,再将数据传到TXD[1:0]上,数据发送完毕需上拉TX_EN,RX_ER与TX_EN相似。MDC/MDIO属于MDIO接口的2根数据线,FPGA通过该接口实现对芯片的初始化,从而使芯片能够正常地发送接收数据。 目前国内外关于数字量溯源的标准较少,无法满足相关功能的验证,文中以数字化电能表的检测项目为准,参考标准中对应的参数指标,设计了准确度较高的数字量验证平台,对标准数字功率源的随机性报文数据丢失以及报文发布时间离散度可控等基本功能进行验证。 参考GB/T17215.303-2013《交流电测量设备 特殊要求 第三部分:数字化电能表》、DL/T《1955-2018 计量用合并单元测试仪通用技术条件》等标准规定,设计了图4所示的数字量验证平台。 图4 数字量验证平台Fig.4 Verification platform for digital quantity 将标准数字功率源的光口以太网报文输入硬件解码装置,通过以太网芯片DM9000A的接收中断信号判断采样频率以及丢包数,并将结果传输至上位机。通过高频时钟记录相邻片选信号的下降沿确定报文发布时间离散值。其中硬件解码装置含有标准的光口以太网接收模块,采用RMII接口接收光口数据,该接口时间不确定度为20 ns,远小于3 μs的误差线。 分别将丢包率设置为1个/s,4个/s,10个/s,各测10 min数据,统计每秒的丢包数以及丢包总数,设置为1个/s时的丢包数据如图5所示。 图5 1个/s丢包实验结果Fig.5 Results in package losing test (1/s) 根据解得的丢包结果,计算每秒丢包数与时间的相关系数r及显著性水平p,结果如表1所示。 表1 相关系数及显著性水平Tab.1 Correlation coefficient and significance level 从表1可见,置信水平(1-p)均小于50%,可认定其分布与时间变量相关性极不显著,随机性较强,与实际情况相符。根据上述结果得到丢包累积曲线,如图6所示。 图6 累积丢包Fig.6 Cumulative package loss 10 min测得丢包累积量与时间变量的相关系数分别为:0.996 4(1个/1 s),0.999 4(4个/1 s), 0.999 8(10个/1 s),可认为丢包累计与时间呈线性相关。由于在初始时刻丢包数为零,故丢包累计值可视作时间的正比例函数,使用y=kx模型对个点进行拟合,则直线斜率即为每秒丢包数。拟合直线斜率即分别为:0.991 5(1个/1 s),3.999 1(4个/1 s),10.000 2(10个/1 s),与设置值相符,满足丢包概率可控。 Q/GDW 11111-2013《数字化电能表校准规范》以及Q/GDW 11015-2013《模拟量输入式合并单元检检测规范》均规定输入数字表的合并单元光口数据时间离散值不得超过10 μs,而标准DL/T 1955-2018 《计量用合并单元测试仪通用技术条件》在此基础上明确地提出了采样值发布离散值的检测标准。 为校验这一功能,分别设置数字功率源报文发布时间离散值为250±0 μs、0.4 μs、1 μs、2 μs、5 μs和10 μs, 每次测试10 min,同时要求标准源的检测误差不得大于3 μs。报文发布时间离散值为250±0 μs的实验数据如图7所示。 图7 报文发布时间离散值测量系统Fig.7 Measurement system for discrete value of message release time 由图7可知,在报文发布时间离散值设定为250±0 μs的情况下,功率源的报文发布时间离散值误差最大不超过200 ns。 功率源具备报文发布时间离散值可调功能,设置离散值在250+0.4 μs、250+1 μs、250+2 μs、250+5 μs和250+10 μs, 进行实验,每次测试10 min,由于篇幅所限,其余各测试点的实验数据不在单独列出,将离散值误差记录在表2中。 从表2实验数据可以看出,功率源的报文发布时间离散值误差不超过200 ns,在离散值为250+2 μs时,离散值误差最大不超过20 ns,小于3 μs的误差要求,满足标准数字源的设计需求。 表2 实验结果(单位:μs)Tab.2 Experimental results (μs) 设计了一种报文发布时间离散性可控的数字功率源方案。通过基于混沌映射的随机序列生成算法和高性能光口以太网芯片相结合,解决了传统数字功率源报文数据丢失随机性不足的问题,并控制报文发布时间离散值误差至200 ns。所研制的标准数字功率源满足标准GB/T 17215.303-2013 《交流电测量设备 特殊要求 第三部分:数字化电能表》中提出的关于数字化电能表的异常通信影响试验,以及DL/T 1955-2018 《计量用合并单元测试仪通用技术条件》规定的采样值发布离散值的测试要求。可以用作数字化电能表的检定工作,已地南方电网公司数字电能表校验项目中推广应用。2 基于高性能光口以太网芯片的系统设计

2.1 标准数字功率源主要结构

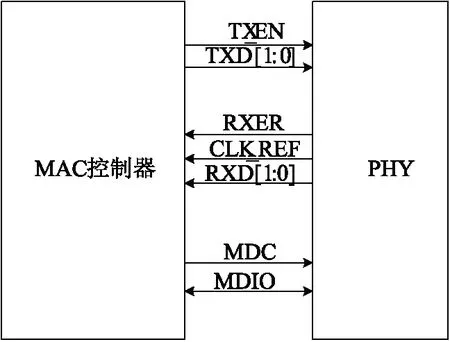

2.2 高性能光口以太网接口设计

3 数字输出影响量和报文发布时间离散度功能验证

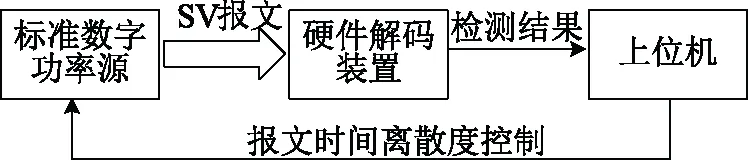

3.1 数字量验证平台设计

3.2 报文数据丢失测试

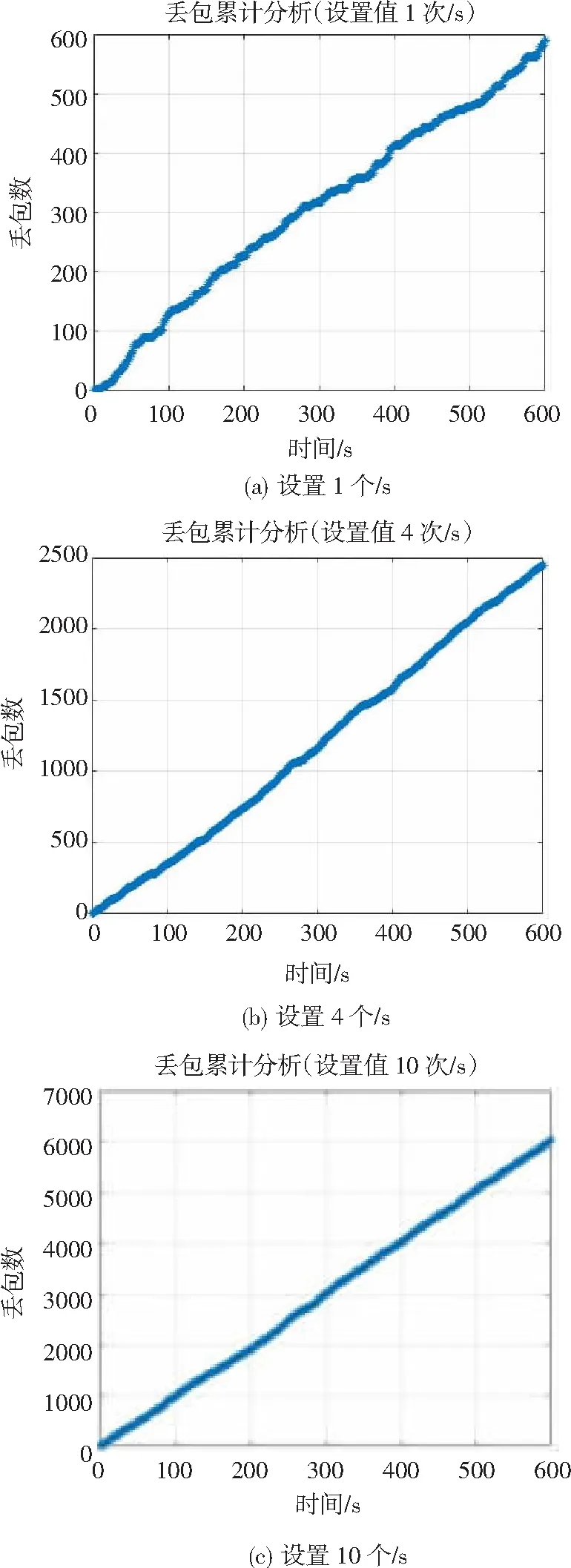

3.3 报文发布时间离散值可控功能测试

4 结束语