负压DC-DC 变换器中新型功率管驱动电路

2022-02-08苏东来韦孟宇高跃明阴亚东

苏东来 ,韦孟宇 ,高跃明 ,阴亚东

(1.福州大学 物理与信息工程学院,福建 福州 350108;2.澳门大学 科技学院电机及电脑工程系,澳门 SAR 999078;3.福州大学 专用芯片与智能微系统研发中心,福建 福州 350108)

负压直流-直流(DC-DC)变换器芯片能够将输入的直流正电压(VDD)转换为直流负电压,为有机发光显示器件(OLEDs)、微发光显示器件(MicroLEDs)等提供负压供电[1-4],因其具有重要学术及产业价值而受到重视和青睐。

常规负压DC-DC 变换器芯片,如反向buckboost 型结构[5-6],需要使用负压来控制功率管的通断,因此其功率管及驱动电路需要耐受较高电压。当前参考设计中的驱动电路主要是通过电平转移电路来直接产生功率管驱动所需负电压[7-8],因而其耐压值需达到输入电源电压的两倍左右(≈2VIN)。为避免晶体管击穿损坏,往往需要采用成本较高的BCD 工艺[9-11]进行设计实现,造成了相对较高的制造成本。

反向降压(Inverting Buck,InvBuck)型电路利用飞电容(Flying Capacitor)电压的翻转能够产生负压脉冲,这为负压DC-DC 变换器中驱动功率管所需直流负压的产生提供了一种替代方案。鉴于此,本文提出了一种可用于InvBuck 型负压DC-DC 变换器的功率管驱动电路。该驱动电路利用InvBuck 型变换器飞电容产生的负压脉冲生成功率管负压驱动信号,其所有MOS 管器件只需承受较低电压(≈VIN),因而可使用标准CMOS 工艺进行设计实现。

1 总体结构

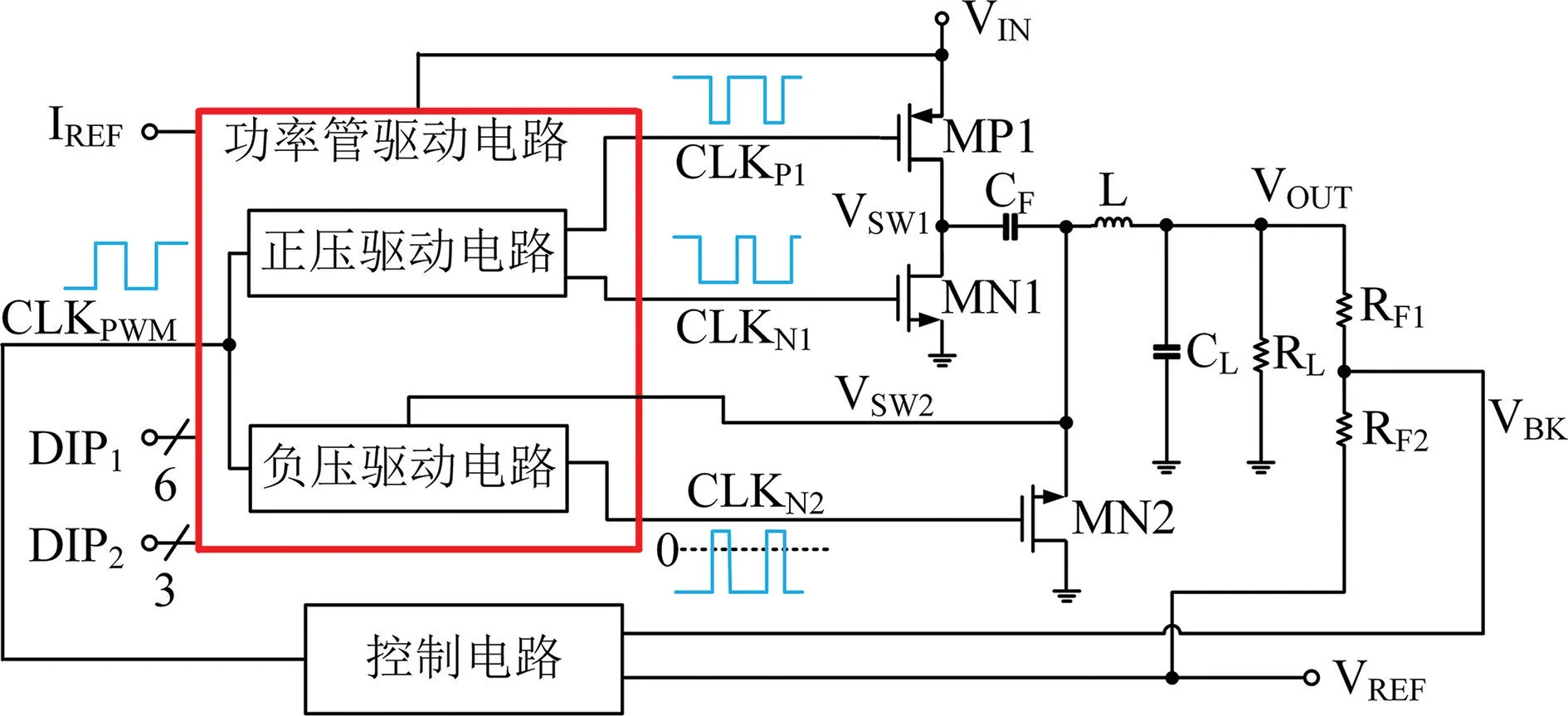

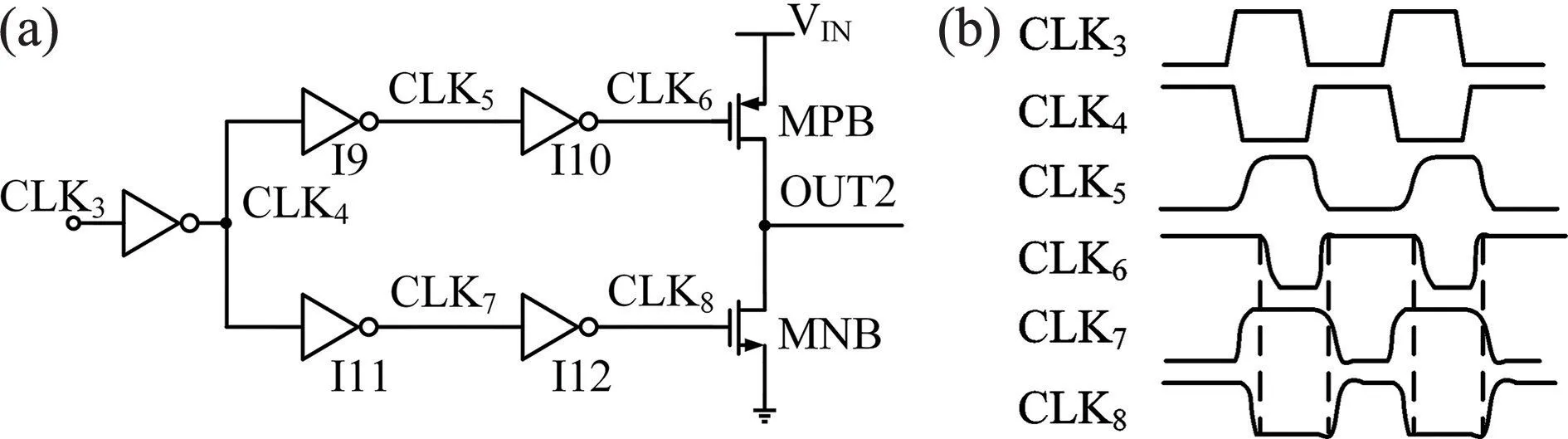

图1 显示了使用本文所述功率管驱动电路的InvBuck 型负压DC-DC 变换器的总体结构。其中实线框所示部分为功率管驱动电路,主要包括正压驱动电路和负压驱动电路模块。图2 为该变换器正常工作时关键信号的时序示意图。

如图1 所示,变换器输出电压VOUT经过采样生成反馈电压VBK后与参考电压VREF进行比较,产生对应的脉宽调制(PWM)信号CLKPWM;CLKPWM输入功率管驱动电路中的正压驱动电路和负压驱动电路生成正压驱动信号CLKP1和CLKN1以及负压驱动信号CLKN2;三路驱动信号分别对PMOS 功率开关管MP1、NMOS功率开关管MN1 和MN2 进行驱动。如图2 所示,CLKN1与CLKP1或CLKN2边沿具有非重叠特性,以防止MN1 与MP1 或MN2 同时导通而造成功率损耗。当CLKP1、CLKN1为0 而CLKN2大于0 时,MP1 和MN2导通而MN1 关断,节点电压VSW1上拉至输入电压VIN,VSW2下拉至地,飞电容CF将进行正向充电而电感L 进行续流。当CLKP1、CLKN1大于0 而CLKN2小于0 时,MP1 和MN2 关断而MN1 导通,VSW1降至接近0 而VSW2反转为-VIN,飞电容CF将对电感L 进行充电。通过以上操作,使电流持续由输出端VOUT流入电感L;最终经电容CL滤波后在输出端VOUT上产生对应的负电压。

图1 InvBuck 型负压DC-DC 变换器总体结构Fig.1 The overall structure of InvBuck negative pressure DC-DC converter

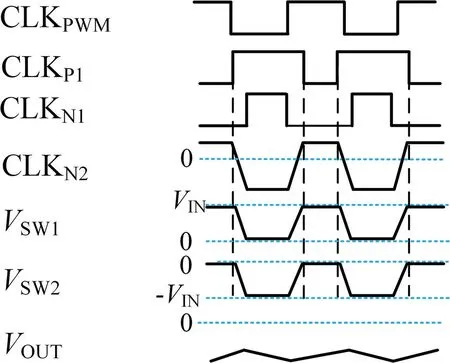

图2 InvBuck 型变换器中关键信号的时序Fig.2 The sequence of key signals in InvBuck converter

由上述分析可知,该InvBuck 型变换器中功率管MP1、MN1 和MN2 关断时其漏源电压(VDS)均可不超过电源电压VIN,因此无需使用耐高压的特殊器件进行设计。如何保证功率管驱动电路中MOS 管器件亦无需承受高电压成为了InvBuck 型变换器设计关键,下文将详细分析。

2 驱动电路子模块电路设计

2.1 正压驱动电路

为降低开关管同时导通造成的能量损耗,需要对开关管驱动信号的时钟边沿进行非重叠[12]处理,以保证飞电容翻转时能先关闭开关管MP1 和MN2,然后再开启开关管MN1,飞电容充电时则相反。该操作是由正压驱动电路实现的。

正压驱动电路如图3(a)所示,其可视为由或非门I3 和I6 构成的锁存器,通过可编程延时单元PDC1 和PDC2 以及其他逻辑门产生延时,以此形成边沿非重叠的效果。同时缓冲器B1 和B2 用于驱动变换器的功率管。正压驱动电路的工作原理如图3(b)所示,由或非门型锁存器结构可知,CLKPWM的上升沿将先传递至CLK2产生下降沿,之后CLK2的下降沿传递至CLK1产生上升沿;反之,CLKPWM的下降沿将先传递至CLK1产生下降沿,之后CLK1的下降沿传递至CLK2产生上升沿,从而使CLK1和CLK2的时钟边沿产生非重叠效果。采用如图3(c)所示的可编程延时单元(PDC)可增强非重叠效果;通过DIP1可修改PDC 中的电容CP进而调整其延时。最终实现CLKN1的上升沿比CLKP1晚tNOV1,而其下降沿比CLKP1早tNOV2。根据上述原理,图3(b)中的非重叠时间tNOV1和tNOV2分别表示为:

图3 正压驱动电路及其工作时序。(a)正压驱动电路;(b) 工作时序;(c) 可编程延时单元(PDC)Fig.3 The positive voltage driving circuit and its working sequence.(a) Positive voltage driving circuit;(b) Working sequence;(c) Programmable delay unit (PDC)

式中:tPDC为可编程延时单元产生的延时;tG为逻辑门延时。由于PDC 延时远大于逻辑延时,所以驱动信号时钟边沿非重叠延时由tPDC决定。非重叠时间对变换器性能具有重要影响,其太短则可能因为工艺的偏差而产生重叠,过长则会降低变换器的转换效率[13-14]。本文中tPDC通过DIP1可对非重叠时间进行精确设置。

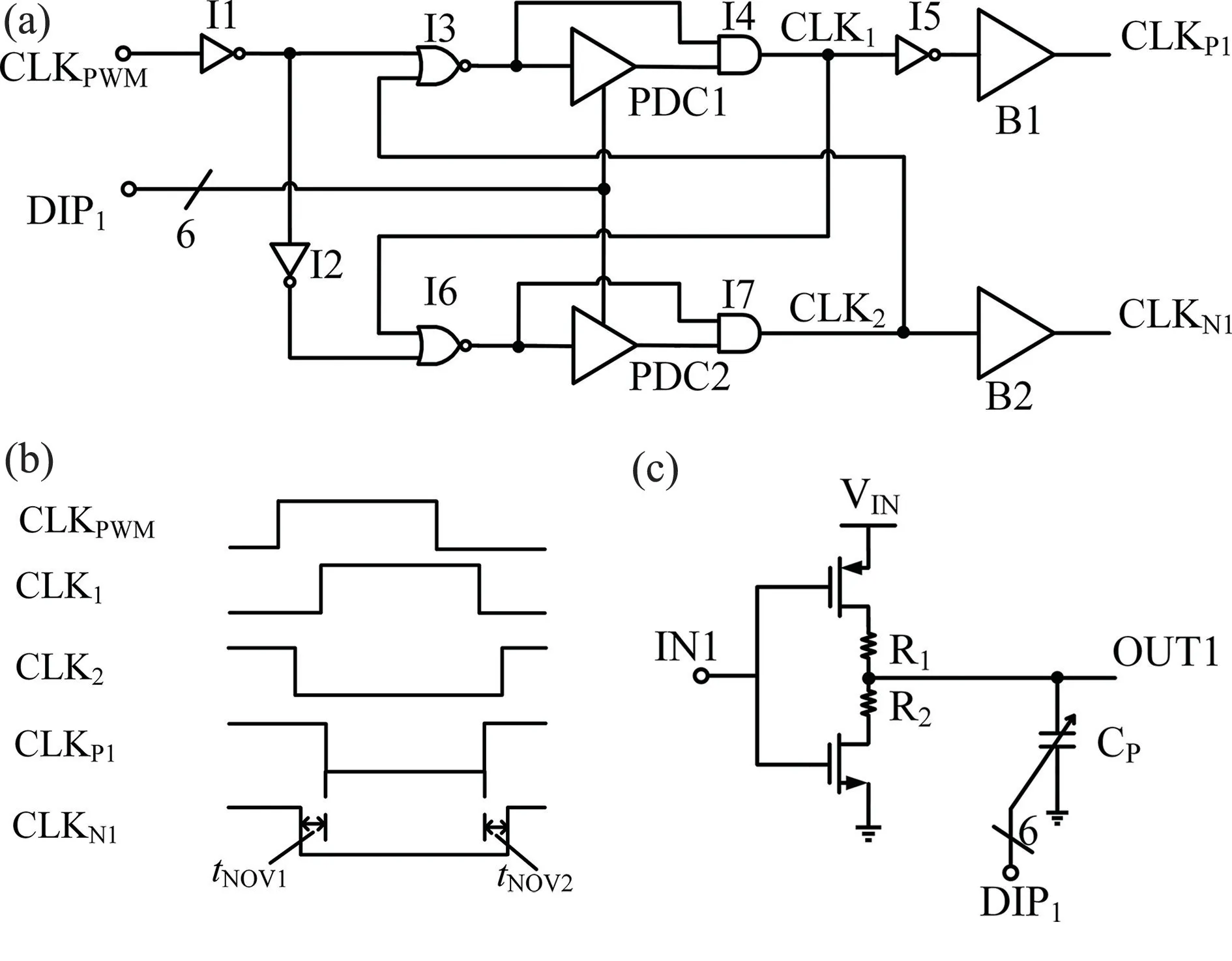

由于功率管存在较大栅极寄生电容,驱动电路输出信号需要进行缓冲以保证足够驱动能力而实现功率管导通和关断的快速切换。图4(a)为驱动电路中缓冲器B1 和B2 的电路结构,图4(b)为缓冲器电路中主要信号的工作时序。为了产生足够的驱动能力,其输出级MOS 管MPB 和MNB 具有较宽的沟道长度,因此MPB 和MNB 的驱动信号也应当具有一定非重叠特性,以减少MPB 和MNB 导通/关闭过程中电流对冲而造成能量损耗。为实现一定的非重叠特性,考虑到反相器MOS 管的尺寸对信号上升/下降延时有影响,电路中I9 和I12 的NMOS 管具有比PMOS 更大的宽长比,而I10 和I11 则相反。其效果如图4(b)所示,当CLK3从低电平转变成高电平时,CLK5上升延时将大于CLK7上升延时,使CLK6下降沿慢于CLK8;反之,CLK5下降延时小于CLK7下降延时,使CLK6上升沿先于CLK8;最终CLK6与CLK8之间边沿产生非重叠。

图4 缓冲器电路及其时序图。(a) 缓冲器电路;(b) 时序图Fig.4 The buffer circuit and sequence diagram.(a) Buffer circuit;(b) Sequence diagram

2.2 负压驱动电路

由第1 节分析可知,当InvBuck 型变换器中的飞电容CF反转时,功率管MN2 源端将变为-VIN负电压。如需关闭MN2,则此时CLKN2应当不高于(VTHN-VIN),其中VTHN为NMOS 阈值电压。为满足该要求,本文所述负压驱动电路将利用飞电容反转时VSW2≈-VIN从而产生相应驱动电平CLKN2;而当开启MN2 时,则使CLKN2高于VTHN。

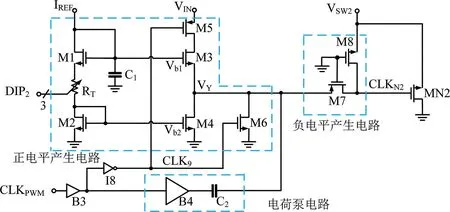

本文设计的负压驱动电路如图5 所示,其由正电平产生电路、负电平产生电路和电荷泵电路等构成。其中正电平产生电路包括由参考电流IREF、NMOS 管M1 与M2、电容C1以及可编程电阻RT构成的偏置电路、NMOS 管M3 与M4 构成的源跟随器和开关管M5与M6。M1和M2分别为M3和M4提供偏置。CLKPWM通过M5 和M6 控制源跟随器工作。负电平产生电路由PMOS 管M7 和NMOS 管M8 构成,栅极都接地。电荷泵电路由缓存器B4 和电容C2构成。

图5 负压驱动电路Fig.5 The negative pressure drive circuit

由前文可知,当CLKPWM为低电平时,变换器飞电容产生反转,VSW2≈-VIN,M5 截止而源跟随器关闭,M6 导通VY将被拉低至地。由于M7 栅源电压为0,因此将截止;同时,由于VSW2≈-VIN,M8 导通,CLKN2电平下降直至接近-VIN,最终造成功率管MN2 截止。反之,当CLKPWM为高电平时,M5 导通使源跟随器工作,而M6 截止;M7 栅源电压小于0 而导通,CLKN2电平上升;另一方面,此时飞电容正端电压VSW2≈0,M8 栅源电压小于VTHN而截止。最终MN2 的过驱动电压可表示为:

式中:IREF为输入参考电流;RT为可编程电阻值;β1和β2分别为M1 和M2 的沟道参数。通过DIP2可改变RT大小,从而调整MN2 导通电阻。由于源跟随器M4 对M3 进行分流,将造成输出电压VY上升缓慢;采用电荷泵可以在CLKPWM变为高电平时对MN2 栅端进行电荷注入,以加快CLKN2的电压上升。

根据上述原理可知,负压驱动电路中所有MOS 管漏源电压均不超过VIN,因此无需采用高压管实现。

3 电路仿真与验证

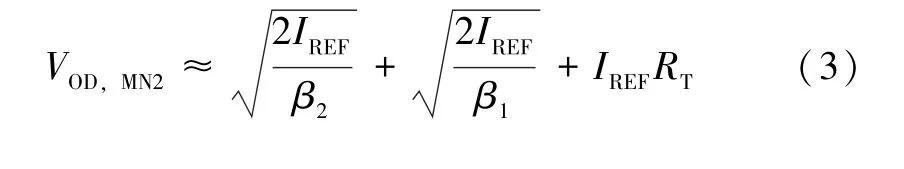

本文基于SMIC 0.18 μm Standard CMOS 工艺进行电路设计、版图绘制和仿真验证。其版图如图6 所示,芯片尺寸为460 μm×190 μm(不包括功率管)。

图6 功率管驱动电路版图Fig.6 The layout of power tube driving circuit

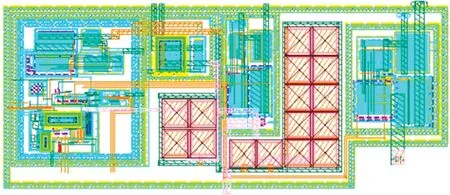

仿真过程中,电源电压设置为VIN=5 V,变换器的功率管开关频率设置为900 kHz。图7 显示了工艺和温度发生变化时CLKP1和CLKN1之间的时钟边沿非重叠特性仿真结果。由图7 可知,在三种典型环境下,CLKP1和CLKN1之间上升沿的非重叠时间为(5.64±0.78) ns;下降沿的非重叠时间为(5.18±0.49) ns。进一步地,在这三种典型环境下,200 次蒙特卡罗的仿真结果显示,CLKP1和CLKN1之间上升沿的非重叠时间范围分别为4.20~7.76 ns,4.71~8.81 ns 和3.56~6.36 ns;下降沿非重叠时间的范围分别为3.64~7.08 ns,4.08~8.04ns和3.14~5.88ns。可以看到,CLKP1和CLKN1之间表现出了良好的时钟边沿非重叠特性。

图7 时钟信号非重叠电路输出波形。(a)上升沿TT;(b)上升沿SS;(c)上升沿FF;(d)下降沿TT;(e)下降沿SS;(f)下降沿FFFig.7 The output waveform of clock signal non-overlapping circuit.(a) Rising edge TT;(b) Rising edge SS;(c) Rising edge FF;(d) Falling edge TT;(e) Falling edge SS;(f) Falling edge FF

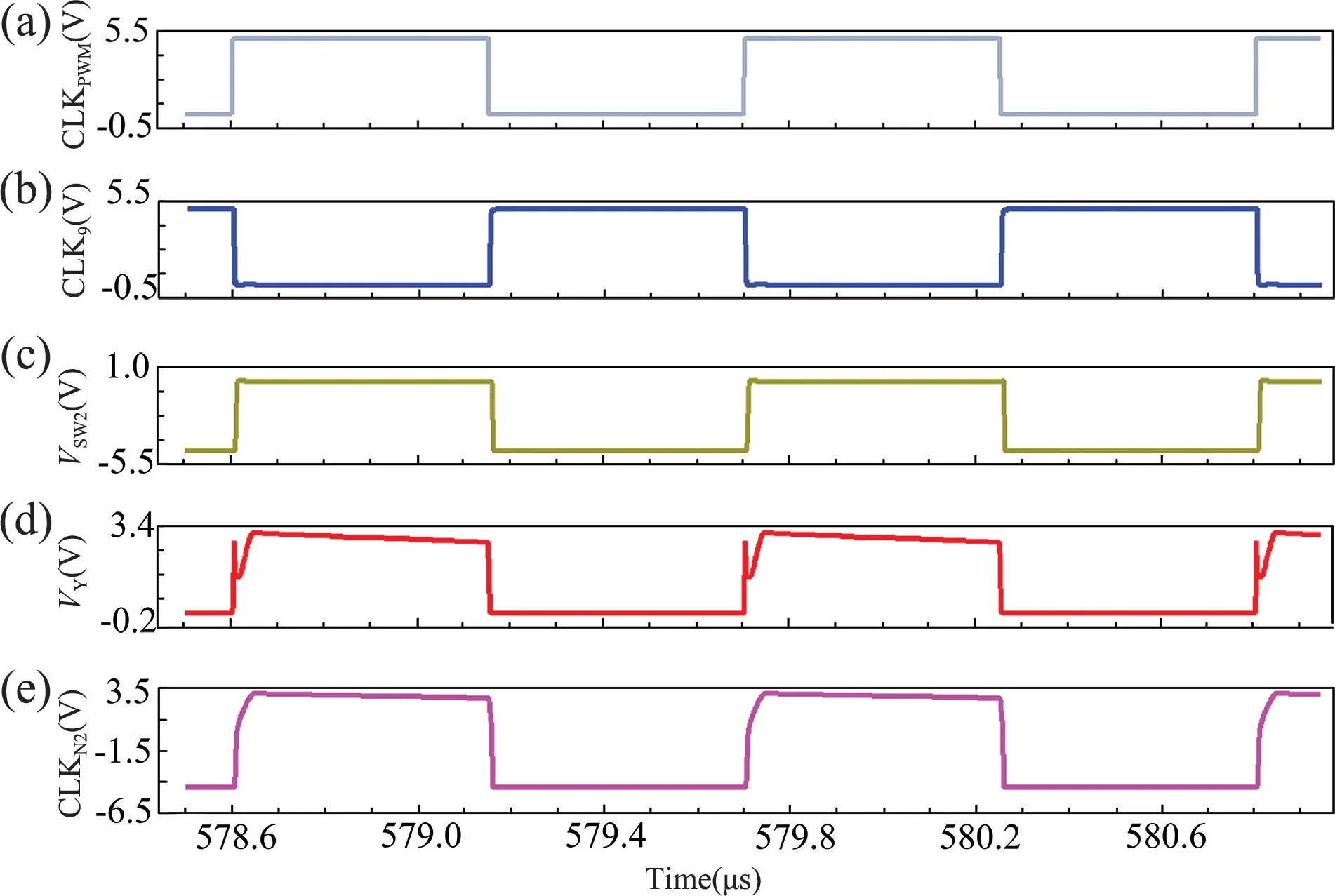

图8 为负压驱动电路中关键信号的仿真波形。仿真过程中控制时钟CLKPWM占空比设置为50%。由图8可知,CLKN2的高电平为2.83 V,低电平为-4.96 V,满足设计要求。

图8 负压驱动整体电路的仿真波形Fig.8 The simulation waveform of the whole circuit of negative pressure drive

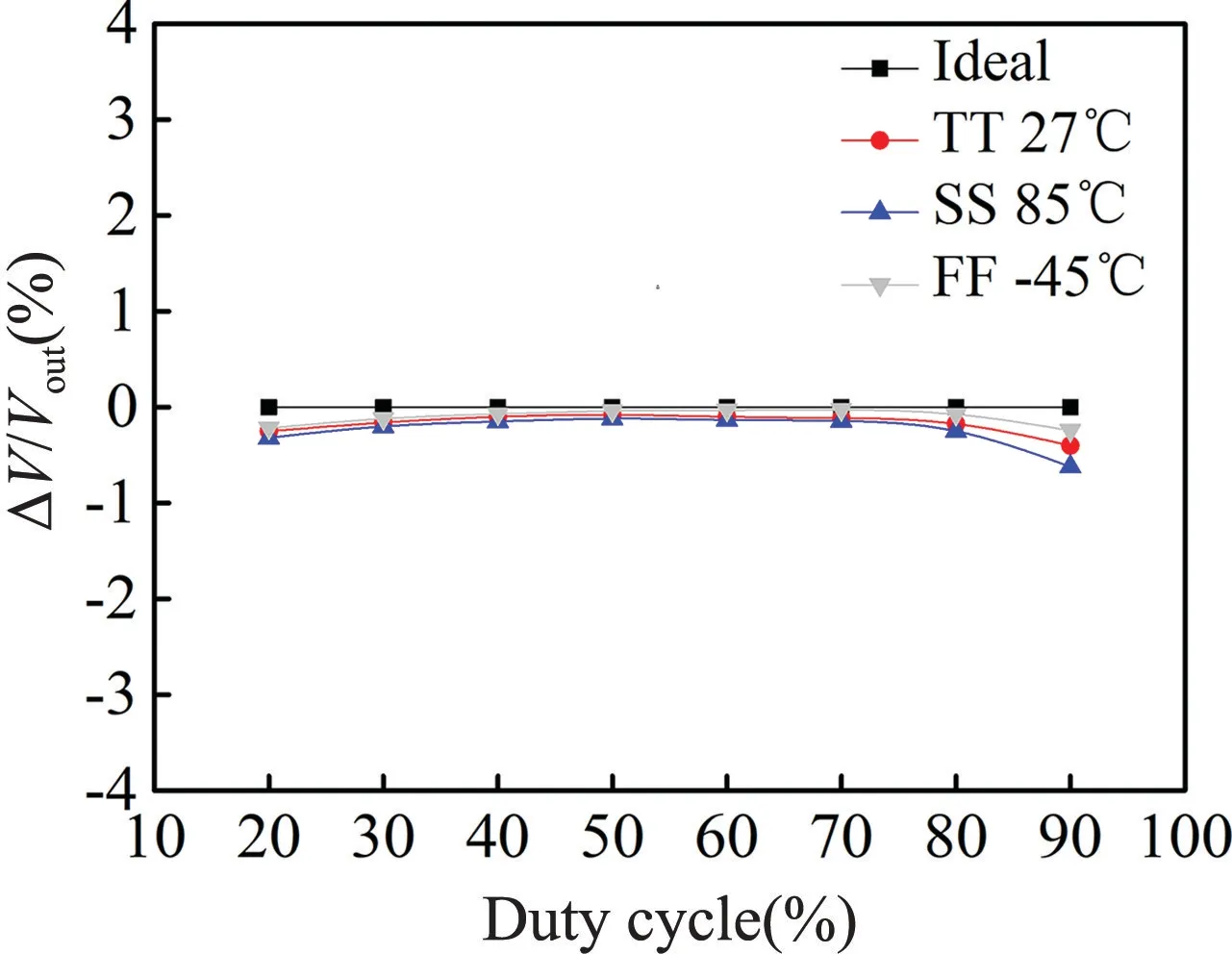

图9 为变换器驱动电路结合功率管联合仿真得到的输出电压结果。可以看到,当工艺和温度发生变化时,各种占空比下变换器实际输出电压与理论计算值之间的相对误差在0.7%内。

图9 输出电压与理想值的相对误差统计图Fig.9 The statistical diagram of relative error between the output voltage and ideal value

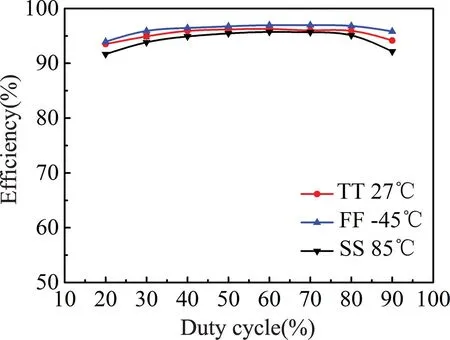

图10 为变换器输出最大电流100 mA,工艺和温度变化时,驱动电路结合功率管联合仿真得到的转换效率仿真结果。其轻载时转换效率主要取决于功率管功耗和驱动电路功耗。可以看出,通过采用本文所述功率管驱动电路,最终输出电压转换效率可以保持在91%以上。

图10 输出效率仿真结果Fig.10 The simulation results of output efficiency

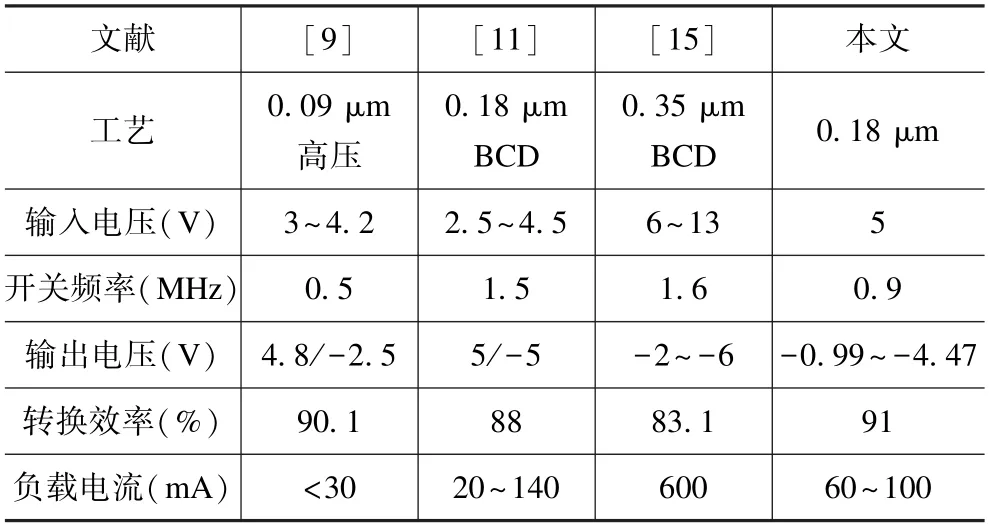

表1 将本文变换器驱动电路结合功率管的性能参数与其他文献的参数进行对比。与采用BCD 或者高压工艺的功率管驱动电路的DC-DC 变换器相比,本文设计在输出电压和转换效率上基本与参考设计持平,但由于采用标准CMOS 工艺进行实现,本设计在芯片工艺和成本上存在明显优势。

表1 与其他文献电路性能对比Tab.1 Performance comparison with references

4 结论

本文设计出一种可用于InvBuck 型负压DC-DC 变换器的新型功率管驱动电路。分别介绍了正压驱动电路和负压驱动电路的工作原理和实现方式,进而分析了功率管驱动电路的整体功能。不同工艺角下的整体仿真结果表明,该功率管驱动电路可以驱动功率管在20%~90%的占空比下产生-0.99~-4.47 V 的输出电压,当输出电流达100 mA 时转换效率依然不低于91%。相比采用BCD 工艺的负压功率管驱动电路,本设计采用普通COMS 工艺实现,显著地降低了芯片面积和制造成本,可应用于反向降压型负压DC-DC 变换器。