一种兼容LPDDR4 内存条和DDR4 内存条的方法

2022-01-06邱文清

邱文清

(福建星网锐捷通讯股份有限公司,福建 福州 350000)

0 引言

目前笔记本的内存条主要采用DDR4 颗粒来生产,极少采用LPDDR4 颗粒来生产内存条,LPDDR4 颗粒由于功耗低、体积小,主要采用贴片的工艺应用于主板上。由于DDR4 颗粒和LPDDR4颗粒的物料价格是随市场行情波动的,经常存在相同容量的DDR4 颗粒和LPDDR4 颗粒的价格不同,因此产生了使用成本更低的颗粒来生成内存条的需求

但是,LPDDR4 内存条和DDR4 内存条的供电需求不同,LPDDR4 内存条的VDDQ 引脚需要1.1V 电压,VPP 引脚需要1.8V 电压,DDR4 内存条的VDDQ 引脚需要1.2V 电压,VPP 引脚需要2.5V 电压;传统的主板内存槽并不能自适应匹配两种内存条。因此,如何提供一种自适应匹配LPDDR4 内存条和DDR4 内存条的装置,实现自适应匹配LPDDR4 内存条和DDR4 内存条,成为一个亟待解决的问题。

1 设计总体思路

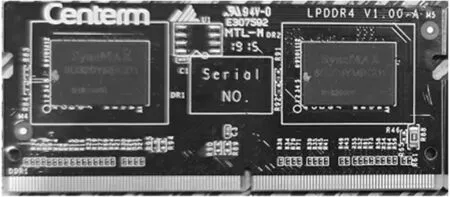

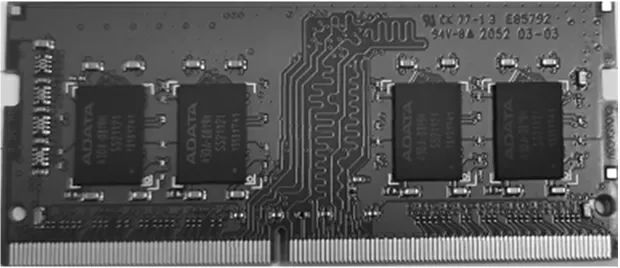

该设计要解决的技术问题,在于提供一种自适应匹配LPDDR4 内存条和DDR4 内存条的装置主板,实现自适应匹配LPDDR4 内存条(见图1)和DDR4 内存条(见图2)。

图1 LPDDR4 SODIMM 条

图2 DDR4 SODIMM 条

1.1 总体思路

主板装置内存槽由260pin 组成,其中第87pin 和第100pin来识别插入的内存条类型,LPDDR4 内存条的第87pin 和第100pin 设计置低,DDR4 内存条第87pin 和第100pin 设计为NC;当LPDDR4 内存条接入时,主板SODIMM01 的一侧第87pin 和第100pin 拉低,信号DDR_SEL0 及LPD4-DET0 置低,这两根信号主要来控制VDDQ 和VPP 电平的切换。①DDR_SEL0 信号置低,PMIC(U27)会把VDDQ 设置1.1V,满足LPDDR4 供电;②LPD4-DET0 置低,通过MOS 管外围供电切换电路,使VPP 的供电源头+VSWIN 会切换为+V1.8A,此时PMIC(U27)会输出VPP切换为1.8V,满足LPDDR4 时序要求。

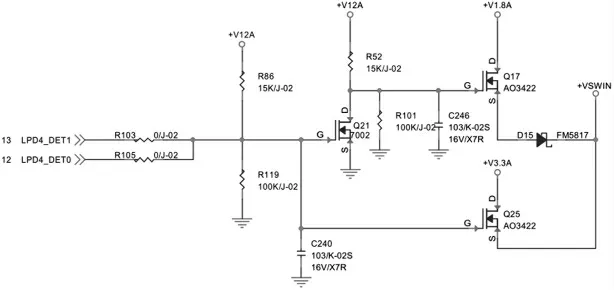

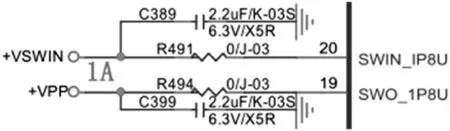

当DDR4 内存条接入时,DDR_SEL0 及LPD4-DET0 此时为NC,PMIC 会把VDDQ 设置1.2V,满足DDR4 供电,同时外围供电切换电路,使VPP 的供电源头+VSWIN 会切换为+V3.3A,此时PIMC(U27)会输出VPP 切换为2.5V,满足DDR4 时序要求,从而实现不管接入的是哪一种类型内存条都可自适应。目前设计的逻辑只要有一个SODIMM 槽上插入LPDDR4 内存条,供电即会切换为LPDDR4 模式,设计为双槽应用(见图3)。

图3 新型外围供电电路的电路

1.2 具体实施方法

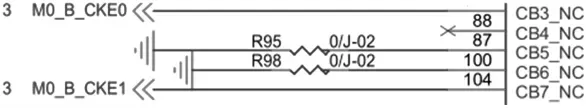

该设计有几部分组成:首先主板内存槽第87pin 和第100pin来判断接入内存条这两个pin 的状态是置低(见图4)还是空闲(见图5),置低说明接入时LPDDR4 条,空闲说明接入是DDR4条;其次外围电路控制VPP 的输出电压原理设计见图6、图7;满足供电和时序要求,具体实施方式:

图4 LPDDR4 内存条第87pin 和第100pin 设置置低

图5 DDR4 内存条第87pin 和第100pin 设置空闲

图6 新型电源管理电路的电路图(一)

内存条(DDR4 颗粒)金手指87pin 和100pin 设计NC,内存条(LPDDR4 颗粒)金手指87pin 和100pin 设计置低。

LPDDR4 内存条接入时,主板内存槽一侧87pin 及100pin 拉低,此时DDR_SEL0 及LPD4-DET0 两根信号置低,当DDR_SEL0 置低,PMIC(U27)会把VDDQ 设置为1.1V;当LPD4-DET0 置低,通过电路设计图7 Q21 Q25 不导通,Q17 导通,输出+VSWIN 为+V1.8A,故VPP 输出1.8V。

DDR4 内存条接入时,主板内存槽一侧87pin 及100pin NC,定义此时DDR_SEL0 及LPD4-DET0 两根信号置高,当DDR_SEL0 置高,PMIC(U27)会把VDDQ 设置为1.2V(见图7),当LPD4-DET0 置高,通过电路设计(见图7)Q21 Q25 导通,Q17不导通,输出+VSWIN 为+V3.3A,VPP 输出2.5V,最终实物(见图1)。

图7 新型电源管理电路的电路图(二)

1.3 技术点

主板端实现LPDDR4 SODIMM 内存及DDR4 SODIMM 内存兼容,首先技术上满足如下2 点。

(1)每个SODIMM 增加4 根SOC 引出的LPDDR4 内存控制信号,原为NC。

MEM_CH0_CKE1B(SOC BG54)CONNECT TO SODIMM0 PIN104

MEM_CH0_CKE0B(SOC BH54)CONNECT TO SODIMM0 PIN105

MEM_CH0_CS1A (SOC BL44)CONNECT TO SODIMM0 PIN162

MEM_CH0_CS0B (SOC BJ42) CONNECT TO SODIMM0 PIN165

MEM_CH1_CKE1B(SOC BL12) CONNECT TO SODIMM1 PIN104

MEM_CH1_CKE0B (SOC BJ13) CONNECT TO SODIMM1 PIN105

MEM_CH1_CS1A (SOC BG2) CONNECT TO SODIMM1 PIN162

MEM_CH1_CS0B (SOC BF1) CONNECT TO SODIMM1 PIN165

(2)LPDDR4 与DDR4 在供电电压(VDDQ)及时序电压(VPP)上不一样,需要解决主板上电源电压可以自适应切换。

2 改善

改善主要在BIOS 的SPD 设置上,LPDDR4 内存条不能做到像DDR4 内存条那样,SPD 信息自适配能力,LPDDR4 内存条在不同颗粒容量大小设置不同且单一设置,已验证使用的是单颗2GB,一根内存条贴2 片颗粒,总容量4GB,主要设置信息如下:

RankSize = 1024, DQBusWidth = 32, DeviceWidth = 2, Dram-Density[2] = 8 |

DIMM0 Memory Size: 2048, System Mem 2048 in MB

windy_debug_memory glk BxtSeries=3

RankSize = 1024, DQBusWidth = 32, DeviceWidth = 2, Dram-Density[2] = 8 |

DIMM1 Memory Size: 2048, System Mem 4096 in MB

不足为BIOS 部分,使用DDR4 内存条的主板如果要使用LPDDR4 不同容量的内存,BIOS 要重新配置烧录否则无法开机。

后续完善可以让BIOS 工程师做开发兼容,解决手动烧录问题。

3 结论

该设计可产出的效益:半导体内存颗粒是行情物料,根据市场行情调整价格,经常出现两种不同颗粒同容量存在差价,该设计可以应用及平衡在不同行情时期选择最低成本方案。如某企业一年用30 万条DDR4 内存条,两种不同颗粒组成价格相差3美元(约19.10 元人民币),一年原材料成本可节省90 万美元(约573.126 万元人民币),直接带来企业的成本效益,使产品更具有市场竞争力。