基于国产FPGA 的网络平台跨时钟域设计方法*

2021-12-23贾永兴刘文慧

贾永兴,杨 宏,刘文慧,陈 明,滕 杰

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

目前,关键电子元器件“卡脖子”问题已严重阻碍我国电子信息产业的发展,因此研发国产元器件和系统显得极为迫切。作为路由器、交换机以及网关等通信设备的核心部件,网络平台国产化的重要性显而易见。作为一种高速可编程逻辑器件,现场可编程逻辑门阵列(Field-Programmable Gate Array,FPGA)器件应用领域极为广泛,国内厂商(如上海安路科技、深圳紫光同创)也推出了各种规格的产品。此外,FPGA 在网络平台的设计中也是不可或缺的核心器件。在网络平台FPGA 的具体设计实施过程中,因平台的功能要求多、FPGA 外围芯片多以及工作频率高等,跨时钟域同步问题作为其中的一个关键技术问题被提出。结合工程实践,本文就该问题给出合理的解决方法和测试结果。

1 网络平台硬件原理

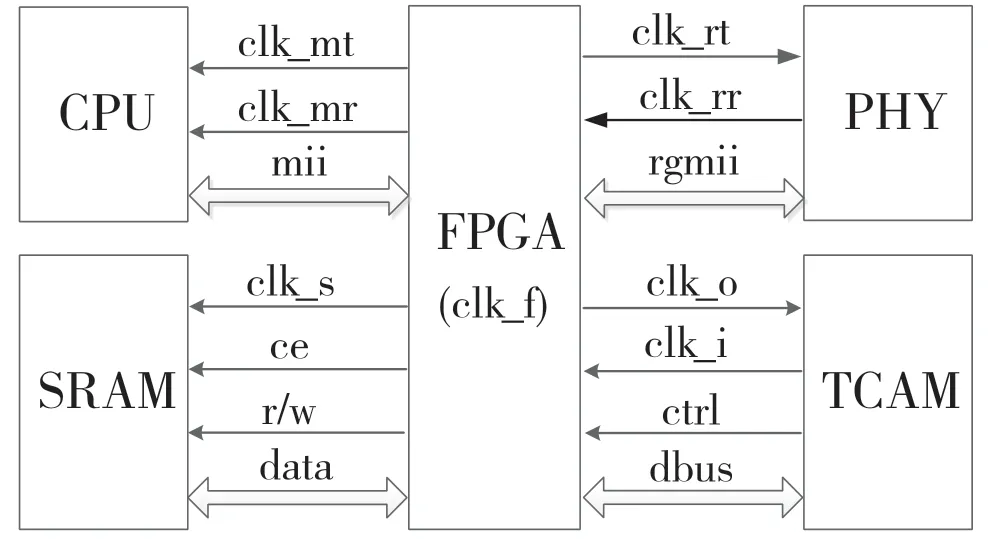

网络平台的硬件原理如图1 所示。FPGA 是平台的核心器件,采用上海安路科技的PH1 系列芯片,负责和外围各种芯片的连接、接口适配、跨时钟域同步、数据流调度等功能;CPU 通过MII 接口和FPGA 连接,负责路由表项配置和平台的管理功能;搜索引擎芯片TCAM 通过数据/控制总线和FPGA连接,负责路由表项的快速查找,存储器SRAM 通过控制/数据总线和FPGA 连接,负责存储路由表项的匹配结果。

图1 网络平台硬件原理框图

从图1 可以看出,FPGA 和各器件之间存在多种时钟信号连接关系,同时FPGA 内部也有多种工作时钟,各时钟的频率如表1 所示。不论是FPGA外围器件的数据进入FPGA,还是FPGA 的数据输出到外围器件,因为时钟频率不同,需要在FPGA内部做时钟域同步设计。

表1 网络平台时钟表

对比进口FPGA,国产FPGA 在功能和性能上仍存在一定的差距。因网络平台数据处理功能复杂,逻辑资源占用多,布局布线复杂,加上工作频率较高,跨时钟域同步的实现上就需要更多的关注,否则会带来功能上的缺陷,甚至不能正常工作。

对网络平台FPGA 跨时钟域的信号可以分为两类:一类是单比特的控制信号,如图1 中和TCAM连接的ctrl 信号,定义为tcam_ctrl_in;另一类是多比特的并行总线信号,如和TCAM 连接的dbus 信号,定义为tcam_dbus_in。下面就这两种类型的信号分别给出跨时钟域方法。

2 国产FPGA 跨时钟域方法

2.1 IOB 的使用

各类数据通过IO 口进入FPGA 后,在进行跨时钟域同步之前,先要确保数据时序的正确性,防止数据亚稳态的发生[1]。为此使用FPGA的IOB资源。IOB 是FPGA 内部距离IO 口最近的寄存器资源,同时IOB 的位置相对固定。使用IOB 能够保证外部信号进入FPGA 以后到寄存器的布线最短,延迟最低,不同条件下的编译结果也不会出现较大的差异[2]。

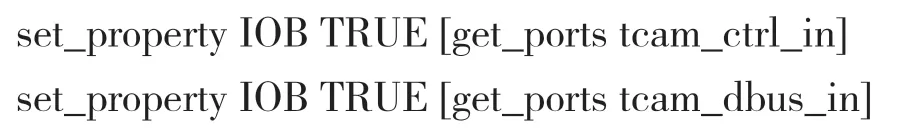

IO 口的具体使用方法如下。

(1)在FPGA 约束文件中增加对输入信号的IOB 约束。

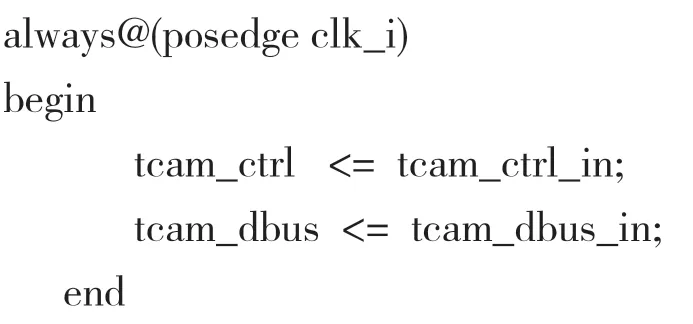

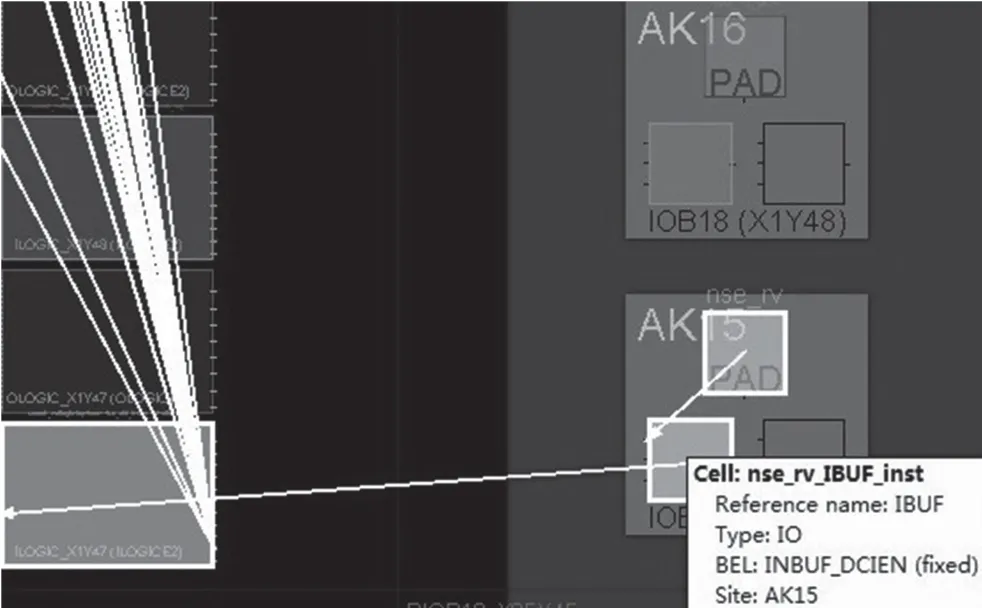

(2)在FPGA 设计中用时钟clk_i 对输入信号打一拍,保证信号进入FPGA 后就进入IOB 的触发器中。图2和图3分别给出了使用IOB前后的布线结果。

图2 没有使用IOB 的布线结果

图3 使用IOB 的布线结果

可以看出,使用了IOB 以后,外部信号进入FPGA 通过IBUF 后,直接进入离IO 口最近的IOB寄存器,确保这段布线的时延小、布线结果相对固定。同时,因为该信号可能在FPGA内部有多个连接关系,也保证了信号在FPGA 内部时序的正确性[3]。

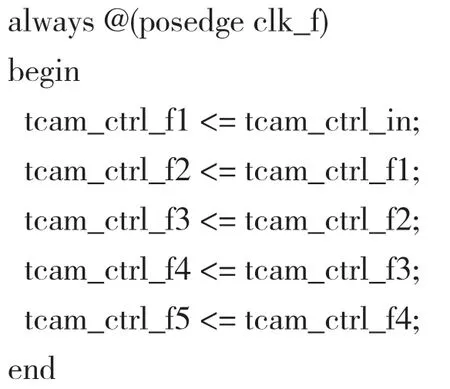

2.2 控制信号跨时钟域同步

对网络平台的控制信号tcam_ctrl_in,在FPGA中跨时钟域同步方法如下。

控制信号tcam_ctrl_in 进入FPGA 之后,使FPGA 用内部时钟通过五级触发器得到同步信号tcam_ctrl_f5。在布局上要求触发器放置在相同的slice 中,确保触发器之间的布线最短,延迟最小。

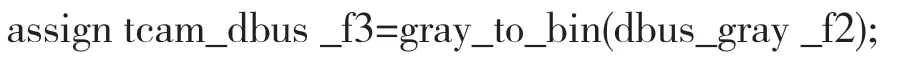

2.3 并行总线信号跨时钟域同步

对网络平台的并行总线信号tcam_dbus_in,在FPGA 中跨时钟域同步方法如下[4]。

(1)在clk_i 时钟域,将并行总线信号tcam_dbus_in 转换为格雷码dbus _gray。

(2)通过两级触发器将dbus_gray 同步到clk_f 时钟域。

(3)在clk_f 时钟域,将总线信号由格雷码数据转换为二进制数据tcam_dbus _f3。

这里使用了格雷码。格雷码是一种错误最小化编码,特点是相邻码组的码距为一,也就是任意相邻码组之间仅有一位不同,可以有效提高电路的抗干扰能力。因为网络平台的并行总线信号多为地址指针,地址指针变化一次,格雷码只有一位发生变化,大大降低了数据亚稳态的概率。

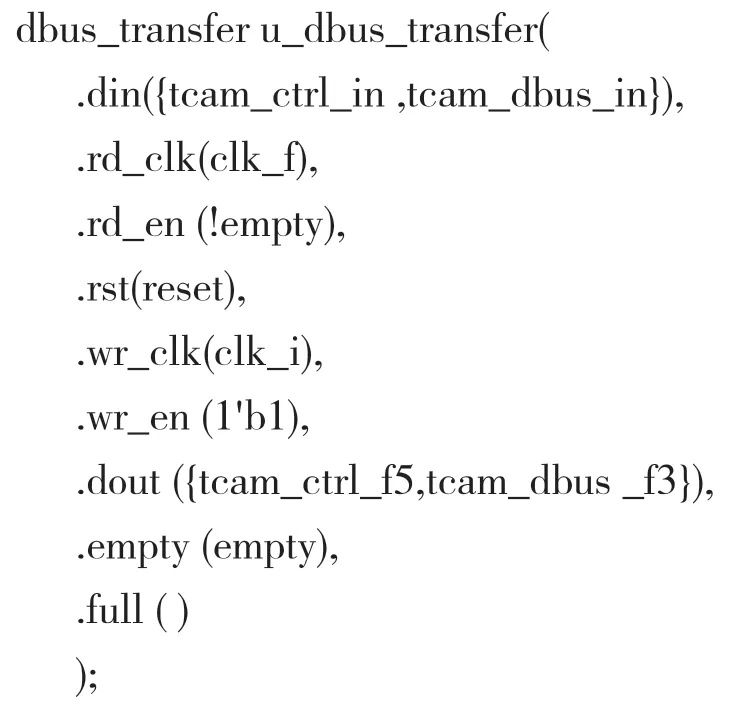

2.4 异步fifo 跨时钟域同步

上面采用多级触发器的方式实现跨时钟域同步,但是这种方法对于突发数据会存在一些缺陷。采用异步fifo 作数据跨时钟域同步是一种更有效的解决方案[5]。异步fifo 即先进先出电路,数据的读写采用不同的时钟。它既可用作控制信号,也可用作并行总线信号的跨时钟域同步。

它的具体实现方法如下:

该方法仅适用于读时钟频率大于或者等于写时钟频率的情况。这种情况下不会有fifo 溢出的情况发生,采用fifo 的非空信号作为fifo 的读信号,很简便地完成了数据跨时钟域同步。对于读时钟频率小于时钟频率的情况,则对fifo 的读写控制信号要做相应判定。当fifo 满了的时候,确保不能有数据的写入,以防止数据溢出导致数据流程异常。该流程最好采用状态机完成,以确保读写信号的正确性。

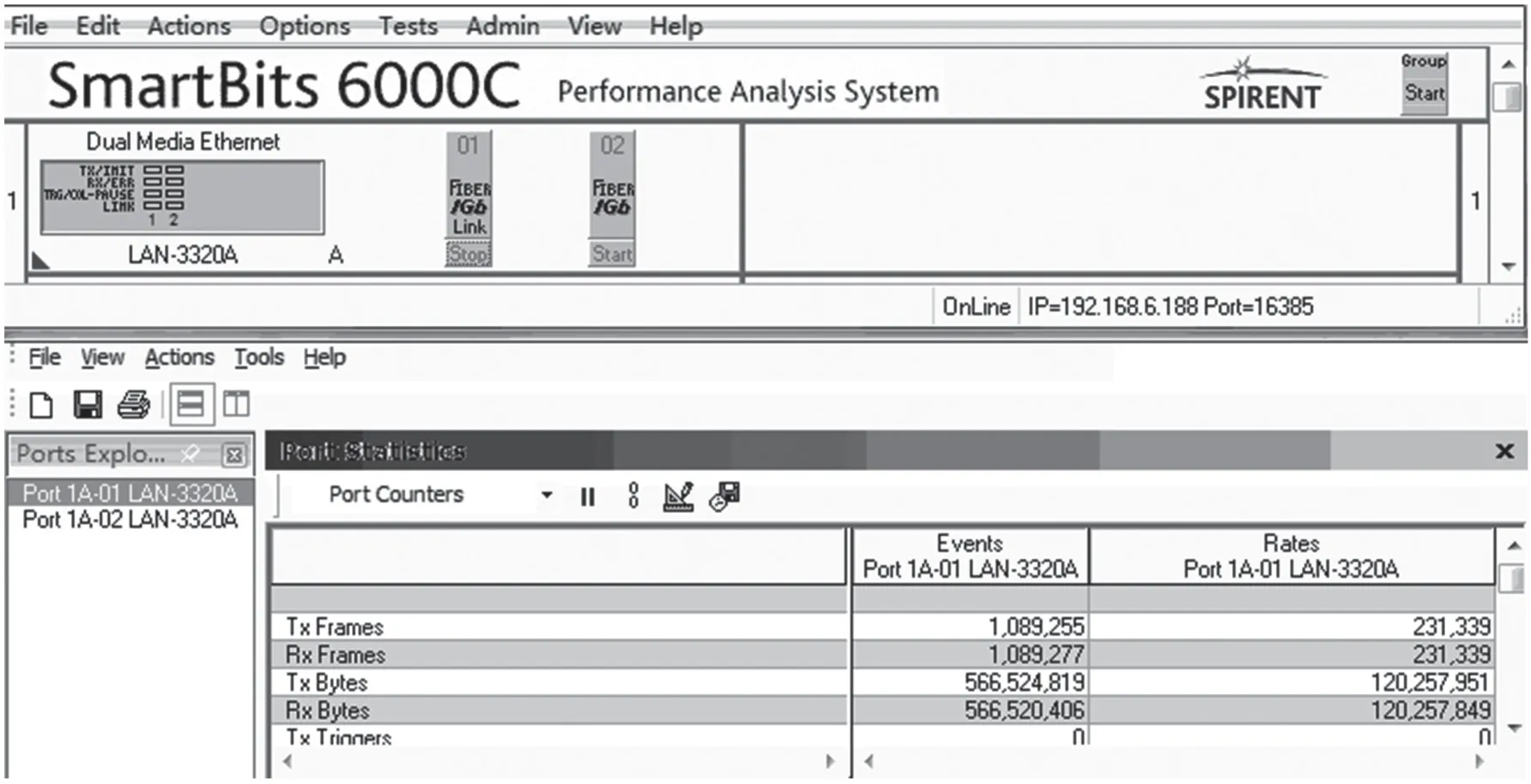

3 测试结果

针对以上的设计方法开展了实际应用测试,在PHY 接口注入1 Gb/s 的数据流,通过网络平台的数据查表流程后再次返回到PHY 接口,测试结果如图4 所示。

图4 测试结果

从测试结果可以看出,收发数据帧速率Tx Frames Rates 和Tx Frames Rates 的大小一致,表明查表功能正常,没有功能缺陷和数据丢失问题发生。因为该测试结果是数据正在收发的过程中获取的,所以收发包字节速率(Tx Bytes Rates 和Tx Bytes Rates)的差异是正常的。

4 结语

本文基于网络平台国产FPGA设计的工程实践,针对高频率情况下的FPGA 设计,给出了IOB 应用、控制信号跨时钟域同步、并行信号跨时钟域同步、异步fifo 时钟域同步等方面的设计方法,并对设计结果做了测试验证,符合设计预期。这些方法对于网络通信设备的FPGA 设计和问题排查都有一定的借鉴意义。后续的工作需要考虑在提高TCAM 芯片工作频率的情况下,实现网络平台更大的数据吞吐量,以及这种情况下的FPGA 实现方法。