面向SCA的DPR软件架构设计与调度技术

2021-12-20文智敏魏急波

郭 彪,唐 麒,文智敏,傅 娟,王 玲,魏急波

(1.湖南大学 电气与信息工程学院,长沙 410082;2.国防科技大学 电子科学学院,长沙 410073;3.长沙轨道交通运营有限公司,长沙 410000;4.军事科学院 系统工程研究院,北京 100101)

0 概述

目前,不同用户需求和技术迭代衍生出WIFI、蓝牙等短距无线通信以及卫星通信、GSM 等长距无线通信。硬件平台趋于多样化,设备之间存在兼容性差、软件开发和维护升级周期长、部署成本高等问题。软件无线电(Software Defined Radio,SDR)技术提供了一种有效的、成本相对低的解决方案,通过软件更新升级即可实现多模式、多频段、多功能的无线通信[1]。

SDR在移动终端、通信基站等民用领域应用广泛。在军事上,SDR 作为新一代军事无线通信领域的关键核心技术,已成为全球军事无线通信系统的技术体制和发展方向。以美军为例,其各军种的无线通信频率范围为2 MHz~3 GHz,频谱覆盖范围广,相互之间通信协同性要求高。美军主导制定了联合战术通信系统和联合战术网络中心计划,在2012 年全面实现软件无线电电台装备体制,截止到2017 年底装备约50 万部各型软件无线电台。这种电台改变了传统以硬件平台为主的设计模式,通过将接收、发送、调制、解调等功能进行模块化设计,从而装载不同功能的波形软件,实现同一平台的多种通信方式切换。

SDR 系统包括硬件支撑平台和软件体系架构。软件体系架构是支撑整个系统的核心,其中以美军JTRS/JTNC 项目中发布的软件通信体系结构(Software Communication Architecture,SCA)最具代表性。目前有诸多针对SDR 的相关研究[2-4],在硬件支撑平台方面,文献[5]搭建了通用一体化SDR 平台,该平台可实现基本的SDR 射频数据收发功能。文献[6]设计了基于ZEDBOARD 的嵌入式软件无线电软件平台,该平台拥有较高的集成度和可拓展性。

基于SCA 的软件架构是SDR 系统的核心,相关研究也十分广泛[7]。在SCA 的标准符合性测试方面,文献[8]基于扩展有限状态机进行SCA 符合性测试,并使用了贪心算法以快速验证测试波形应用是否符合SCA 标准规范。在SCA 的框架设计方面,文献[9]设计了轻量化的SCA 核心框架,解决了接口冗余与可调整性不足的问题。在SDR 系统兼容性发展方面,SCA 已从被设计时部署在通用处理器(General Purpose Processor,GPP)上面,到现在可支持多种类型设备的扩展。文献[10]解决了SCA 在数字信号处理器(Digital Signal Processor,DSP)上的部署问题,通过其框架设计与调制解调器硬件抽象层(Modem Hardware Abstraction Layer,MHAL)的 使用,使波形组件可以在兼容SCA 规范的前提下运行在DSP 上。文献[11]设计了基于SCA 的新型软硬件架构,通过GPP+DSP+FPGA 的数字基带处理单元在硬件平台构建符合SCA 的规范,将该架构应用在雷达、数据链、电子战等多种领域。

随着目前以赛灵思Zynq-7000 等为代表的新型DPR FPGA 计算架构的出现,如何在SCA 中对FPGA 动态部分可重构能力提供支撑的问题尚未得到有效解决。传统的SCA 将FPGA 虚拟化为单一资源,导致资源不能得到有效的空时复用,且SCA 存在资源粒度大、部署方式单一的缺点。

本文将SCA 和FPGA DPR 技术相结合,设计基于SCA 的动态部分可重构软件架构。通过扩展SCA 功能,提升波形应用在动态部分可重构FPGA下的实时部署能力。在此基础上,设计ACO 调度算法增强组件的调度和管理方式,提高硬件平台的使用效率。

1 SCA 与可重构技术

1.1 SCA 软件体系架构

SCA 是美军为建立联合战术通信电台开发定义的与设计实现无关的框架。SCA 通过公共对象请求代理体系结构定义统一的开发标准框架和通用结构,使通信系统开发的软件和硬件可以分离,其宗旨是通过在同一硬件平台上加载不同的波形组件以实现不同的功能。此外,也可根据特定的需要对系统进行部分升级,从而最大化地利用系统资源[12]。基于SCA 的通信系统架构如图1 所示。

图1 基于SCA 的通信系统架构Fig.1 Communication system architecture based on SCA

如图1 所示,该系统包括上层的波形应用、中间的核心框架及对应的域描述文件3 个部分。其中波形应用由不同功能的组件组成,用来实现FSK、MSK、扩频等通信功能。核心框架是一系列应用编程接口与组件集合,在操作系统上对软件和底层硬件进行更高层次封装,为波形应用提供标准化接口和服务,并对波形应用的动态加卸载、部署和域内资源进行统一管理。域描述文件采用可拓展标记语言(eXtensible Markup Language,XML)配置SCA 域内的所有组件。根据配置功能的不同又分为软件包描述文件(Software Package Descriptor,SPD)、设备配置描述文件、软件装配描述文件(Software Assembly Descriptor,SAD)等[13]。这些文件配置了域内每个组件的接口、容量、属性、内部依赖、互联、逻辑位置等信息[14]。核心框架通过解析组件的域描述文件,完成组件的部署、启动、配置、查询等操作。

SCA 将FPGA、DSP、GPP 等物理硬件设备虚拟化为域内的设备组件,设备组件通过提供统一的加载、卸载、部署等接口满足硬件平台的可复用性需求。

1.2 FPGA 的DPR 技 术

基于FPGA 的动态可重构技术能够在FPGA 运行过程中将其内部的全部或部分逻辑资源重新配置,进而实现FPGA 逻辑功能的动态切换和时分复用,而不终止器件的运行[15]。此外,FPGA 的DPR 技术重构粒度更小,允许每个重构区域根据功能需要动态加载和切换配置文件。FPGA 通过内部配置访问端口下载配置文件,并对指定区域进行逻辑功能实时更改而不影响其他区域的任务执行。FPGA DPR 功能示意图如图2 所示。

图2 FPGA 动态部分可重构示意图Fig.2 Schematric diagram of dynamic partial reconfiguration of FPGA

图2 中的DPR FPGA 划分了4 个重构子区域,并分别执行Task1、Task2、Task3、Task4 任务。每个重构区域之间独立执行,可根据任务需求实时更改重构子区域的数量和大小,不影响其他正在执行的重构区域。

在现有的SCA 软件架构体系下,只有面向FPGA 全局重构方式的资源虚拟化支撑,没有针对DPR FPGA 的相关虚拟化架构。本文第2 节在基于SCA 的规范下设计DPR FPGA 的硬件资源虚拟化软件架构,提出波形组件DPR 部署的流程机制。

2 基于SCA 的DPR 软件架构设计

为满足SDR 系统的异构性和可移植性需求,SCA域内将FPGA 硬件设备虚拟化为FPGA 设备组件,核心框架通过管理设备组件来间接管理FPGA 硬件。设备组件的域描述文件利用XML 和统一的软件架构完成硬件资源虚拟化。其主要配置两部分信息:一是该设备组件自身运行所需的软硬件环境,主要包括操作系统、设备组件编程代码语言及设备组件代码在系统内的存放路径等;二是该设备组件所代表的硬件资源,包括硬件设备名称、资源量(内存、计算单元)、接口等信息。

然而,现有SCA 规范下的软件架构将FPGA 设备虚拟化为单一的硬件资源,导致FPGA 的重构粒度大,不能进行空时复用。

2.1 DPR FPGA 设备组件域描述文件架构设计

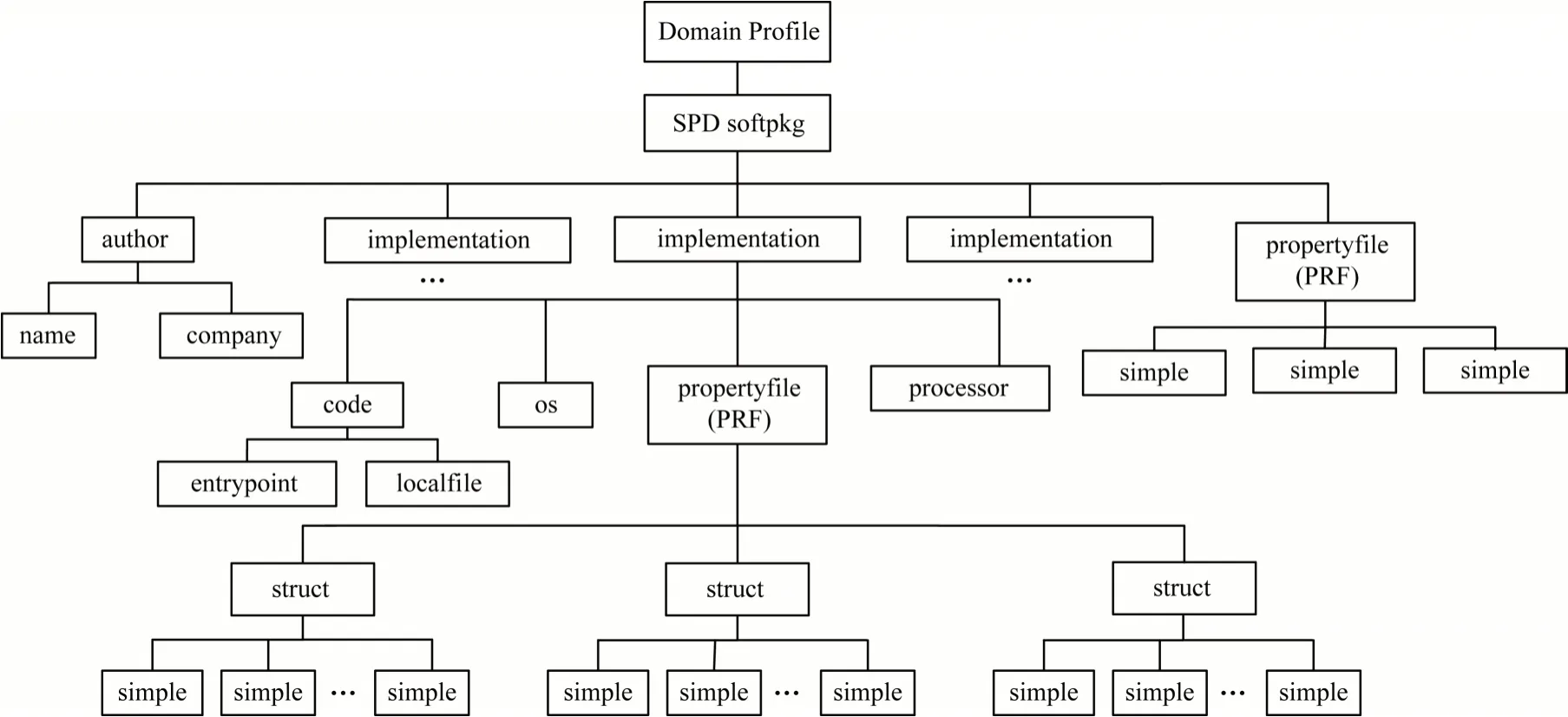

将DPR FPGA 划分的子区域数量和子区域大小不同称为不同的划分方式。将DPR FPGA 硬件设备设计并抽象封装成支持DPR 能力的逻辑设备组件时,该逻辑设备组件应支持不同的划分方式、不同区域约束和不同资源配置。同时,区域描述文件的软件架构要符合SCA 规范要求。图3 所示为本文设计提出的DPR FPGA 设备组件域描述文件的软件架构示意图。其中,DPR FPGA 逻辑设备组件的域描述文件(Domain Profile)主要由软件包描述文件(SPD)和属性配置文件(PRF)组成。SPD 文件的根元素(softpkg)配置了组件开发者(author)、组件实现(implementation)、属性配置文件(PRF)等信息。其中author 元素配置了开发者姓名(name)、组件开发公司(company)等信息;implementation 元素配置了组件代码(code)、组件运行环境(os)、组件执行处理器(processor)等信息;code 元素配置了组件接口信息(entrypoint)、组件代码位置(localfile)等信息。PRF 文件中的结构元素(struct)用来配置多个不同类别组件属性,simple 元素用来配置单一属性。

图3 DPR FPGA 设备组件域描述文件的软件架构Fig.3 Software architecture of DPR FPGA device component domain description file

上述架构在SCA 的规范下提供了对DPR FPGA的资源虚拟化,满足了如下3 个约束:

1)DPR FPGA 支持多种区域划分方式。通过配置图3 中SPD 文件的softpkg 根元素,使其包含一个或多个implementation 子元素,部分代码实现如下:

softpkg 元素下的2 个implementation 子元素分别表示一种FPGA 动态部分可重构区域划分方式的资源描述,每一种划分方式包含不同的FPGA 动态部分可重构区域的数量和大小。

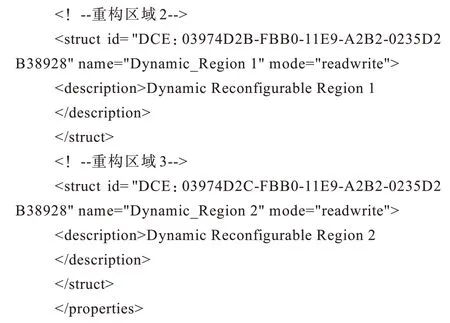

2)每种划分方式支持不同的重构子区域资源描述。配置implementation 元素包含的PRF 属性文件,该文件由多个struct 元素组成,每个struct 元素代表一个重构区域,部分实现代码如下:

上述代码中配置了3 个重构区域,分别是静态重构区、动态重构区1 和动态重构区2。

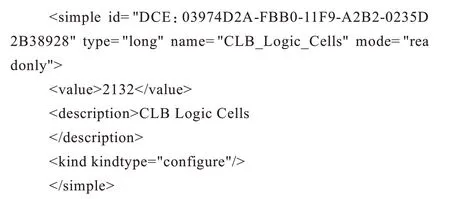

3)每个重构区域支持细粒度的资源配置。图3中的每个simple 元素表示重构区域的一个资源配置信息。资源配置信息包括重构区域标识、重构区域坐标位置、重构区域CLB Logic Cells 数量、重构区域CLB Slices数量、重构区域Digital Clock Managers数量、重构区域DSP 数量、重构区域RAM 数量等。以重构区域CLB Slices 数量为例,部分实现代码如下:

上述代码中的simple 元素配置区域中CLB 资源的数量为2 132。

上述针对DPR FPGA 设备组件域描述文件的软件架构设计,支持了FPGA 的细粒度资源虚拟化,拓展了FPGA DPR 功能,建立了FPGA 硬件可重构区域到SCA 域内的映射关系。软件架构设计使用的所有域描述文件配置元素如simple、struct 等均符合SCA 规范,保证了SCA 整体架构的一致性和统一性,减小了SCA 软件的升级和维护难度。

2.2 基于SCA 的波形组件DPR 部署机制

波形应用是完成某种通信功能的软件应用,由多个组件组成,图4 所示为波形应用示例。

图4 波形应用示例Fig.4 Sample of waveform application

该波形应用由网络设备、滤波、变频等组件组成。基于SCA 的SDR 系统,域管理器通过解析波形应用的XML 域配置文件启动、初始化、运行、配置、重构相应的波形应用程序[16]。

在2.1 节中完成了FPGA DPR 的资源虚拟化,使SCA 域内有了FPGA 动态部分可重构区域的资源信息。为了将波形组件部署到FPGA 动态部分可重构区域,本节提出了在SCA 域内波形组件DPR 部署的流程和机制,如图5 所示。

图5 波形组件DPR 部署机制Fig.5 DPR deployment mechanism of waveform components

在图5 中,客户端首先调用核心框架控制接口中ApplicationFactory接口 的create 操作。create 操作在SCA 域内创建应用,从而在客户端请求的设备上创建应用提供客户端接口。SCA 解析波形应用的域描述文件,包括应用的SAD 文件、各个组件的SPD 文件等,从而获得应用的组成、各个组件之间的端口连接、组件部署所需的处理器/运行环境等配置信息。逻辑设备通过执行allocateCapacity 操作,分配组件运行所需的内存、处理器,从而更新Device(s)的内存和处理器使用状态。逻辑设备还可以通过LoadableInterface 和ExecutableInterface接口完成组件的加载和执行。如此,波形组件DPR 部署机制建立了波形应用创建、依赖性检查、容量分配、可重构部署完整的映射,提高了组件部署和管理的灵活性。

3 基于蚁群优化算法的调度技术

本文第2 节提供了SCA 下对于DPR FPGA 的架构支撑,包含DPR FPGA 的SDR 硬件设备系统,使组件部署更具灵活性。DPR FPGA 与CPU 计算设备构成了可重构的异构计算平台。为进一步提高波形应用在该平台的部署效率,提升硬件资源利用率,高效的调度算法支撑尤为关键。

3.1 波形应用与计算平台建模

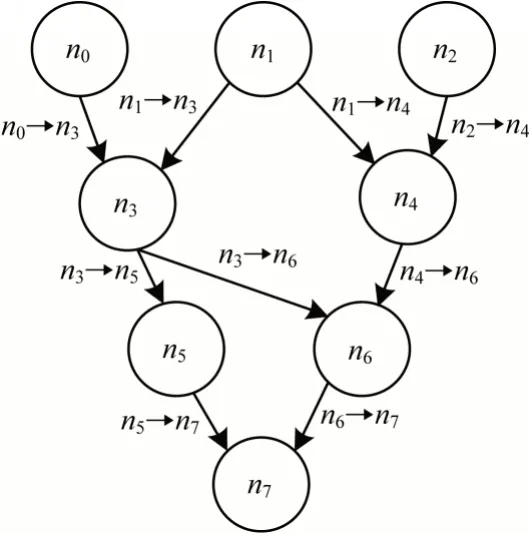

目前针对应用的建模方法有多种,如有向无环图(DAG)[17-19]、同步数据流图(SDFG)[20-22]等。本文运用目前研究较多的DAG 图建模波形应用。图6 所示为DAG 应用示例。

图6 DAG 应用示例Fig.6 Sample of DAG application

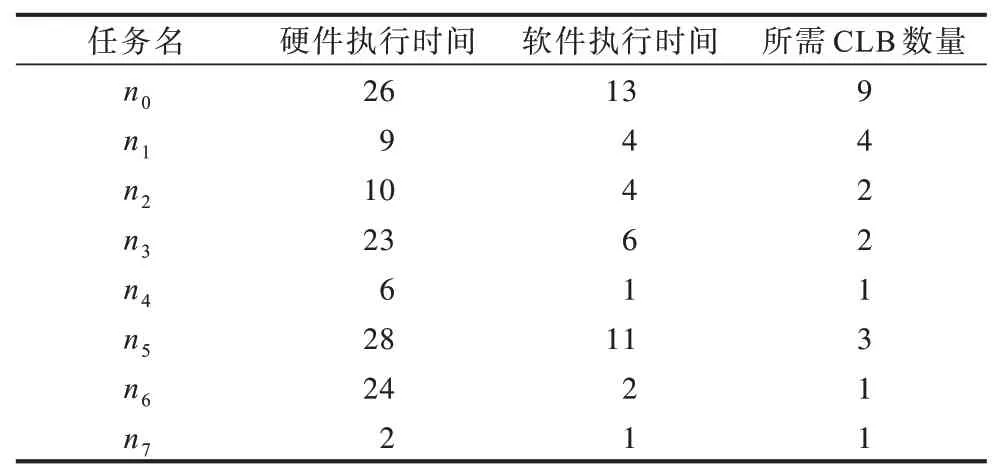

在图6 中,该应用由8 个任务和9 条边组成。任务之间的箭头表示相互依赖关系。将任务在DPR FPGA 上的执行时间称为硬件执行时间,在CPU 上的执行时间称为软件执行时间。表1 为具体任务参数信息,包括任务名、软件执行时间、硬件执行时间以及在FPGA 上执行所需的CLB 资源数量。

表1 波形应用的任务参数Table 1 Task parameters of the waveform application

DPR FPGA 与CPU 组成的SDR 系统中的异构计算平台模型如图7 所示。

图7 异构计算平台Fig.7 Heterogeneous computing platform

图7 中的异构计算系统由一个CPU 和支持二维重构的DPR FPGA 组成,其中FPGA 被划分为4 个重构子区域,通过加载不同的配置文件来更改其逻辑功能。

3.2 调度问题

高效的调度算法可以减小波形应用的执行时间,从而提高系统计算资源的利用率。将确定DAG图中各个任务的执行方式(软件执行或硬件执行)和执行时间(任务的开始时间和结束时间)称为调度。调度结果示意图如图8 所示。

图8 波形应用的调度结果示意图Fig.8 Schematic diagram of scheduling results of the waveform application

在图8 中,计算单元包括一个CPU 和2 个DPR FPGA 重构子区域,深灰色方块代表任务在FPGA 上的重构时间,浅灰色方块代表任务的执行时间。

对于3.1 节异构计算平台,在对波形应用进行调度时需要满足一定的约束条件,具体如下:

1)DAG 图中的任务依赖关系。子任务需要等其所有父任务执行和通信结束后才能开始执行。

2)任务只能执行一次且只能选择一个计算单元(CPU 或FPGA 的一个重构区域)。

3)FPGA 上执行的任务需要先重构再执行。

4)限制FPGA 的资源数量,需满足任务执行所需的资源且同一时间不能超过FPGA 的资源总量。

5)重构端口不能复用,且同一时间只能重构一个任务。

3.3 算法设计

针对3.1 节的应用和计算平台模型,本文提出一种基于蚁群优化的调度算法,通过设置循环次数和控制参数进行迭代求解。每次迭代计算主要分为3 步:确定任务的调度顺序;映射任务到计算单元;信息素更新。该算法能够解决SDR 系统中的波形应用调度问题,有效支撑波形应用的部署。

下面将对算法细节进行介绍。

步骤1确定任务的调度顺序。算法实现时,通过计算组成DAG 各个任务的调度概率,选择调度概率最大的任务作为当前步骤需要调度的任务。任务i在第j步的调度概率如下:

其中:αs为全局调度信息素挥发控制因子;βs为局部调度信息素挥发控制因子为全局调度信息素局部调度信息素;集合N={1,2,…,M}为调度DAG 所需要的总步数,其中M的值等于组成DAG 任务的数量。

步骤2映射任务到计算单元。确定好每一步待调度的任务后,将任务映射到计算单元上并执行,其中计算单元集合由CPU 和DPR FPGA 的重构区域组成。计算任务的“映射概率”,并选取计算值最大的映射单元为计算单元映射。任务i选择计算单元k的映射概率如下:

其中:αm为全局映射信息素挥发控制因子;βm为局部映射信息素挥发控制因子为全局映射信息素局部映射信息素;N是所有计算单元的集合。

步骤3信息素更新。所有蚂蚁完成一次求解时,即更新对应的信息素。信息素的更新公式如下:

其中:ρs为调度信息素挥发因子;ρm为映射信息素挥发因子;SSL为本次迭代所有蚂蚁求解的应用完成时间最小值。其中si为第i只蚂蚁求解的调度长度,其大小等于本次迭代所有任务所完成时间的最大值。Antcount的大小等于蚂蚁数量。上述3 个步骤为单次迭代求解过程,算法执行时不断进行迭代求解。当达到所设置迭代次数的上限时返回已经求得的最优解,该最优解中包含了波形应用的调度结果和波形应用的总完成时间。

4 仿真实验

4.1 实验参数设置

为验证本文所提算法的性能,波形应用调度的DAG图使用文献[23]中的方式随机生成。表2 所示为随机生成DAG 的详细信息,包括任务数n、边数m和问题规模2n+3m[24]。由于软件无线电的硬件计算平台大多执行计算密集型的波形应用,通信计算比(CCR)较小,故本文测试基准DAG 的CCR 设置为0.1。所提算法中的迭代次数为1 000 次,蚂蚁数量为5,全局调度信息素挥发控制因子αs设置为1,局部调度信息素挥发控制因子βs、全局映射信息素挥发控制因子αm及局部映射信息素挥发控制因子βm均设置为1,调度信息素挥发因子ρs设置为0.9,映射信息素挥发因子ρm设置为0.98。为了验证所提调度算法的有效性,本文仿真了没有调度的DAG 随机算法部署(Random Deployment Without Scheduling,RDWS)、MILP 算法[25]和ILP 算法[26]的调度结果。调度性能的评价指标为DAG 的调度长度(SL)和算法求解时间。其中MILP 算法的求解器为LINDO API12.0,ILP 算法的求解器为Gurobi 9.0.1,求解时间上限值(timeout)均设置为1 800 s,若求解器达到时间上限值时仍没有求出最优解,则返回当前已求得的最优解。

表2 随机生成的DAG 信息Table 2 Randomly generated DAG information

4.2 实验结果与分析

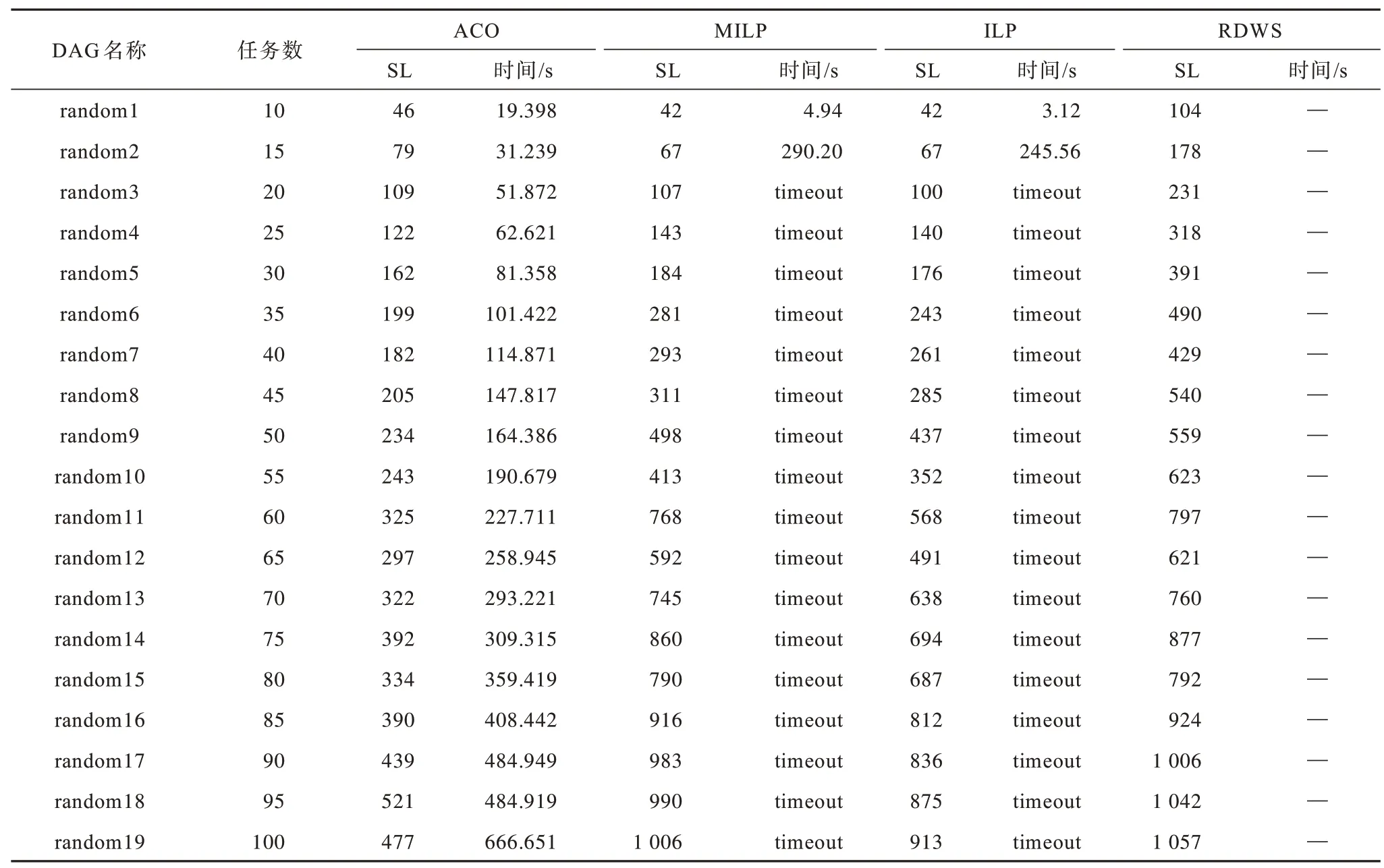

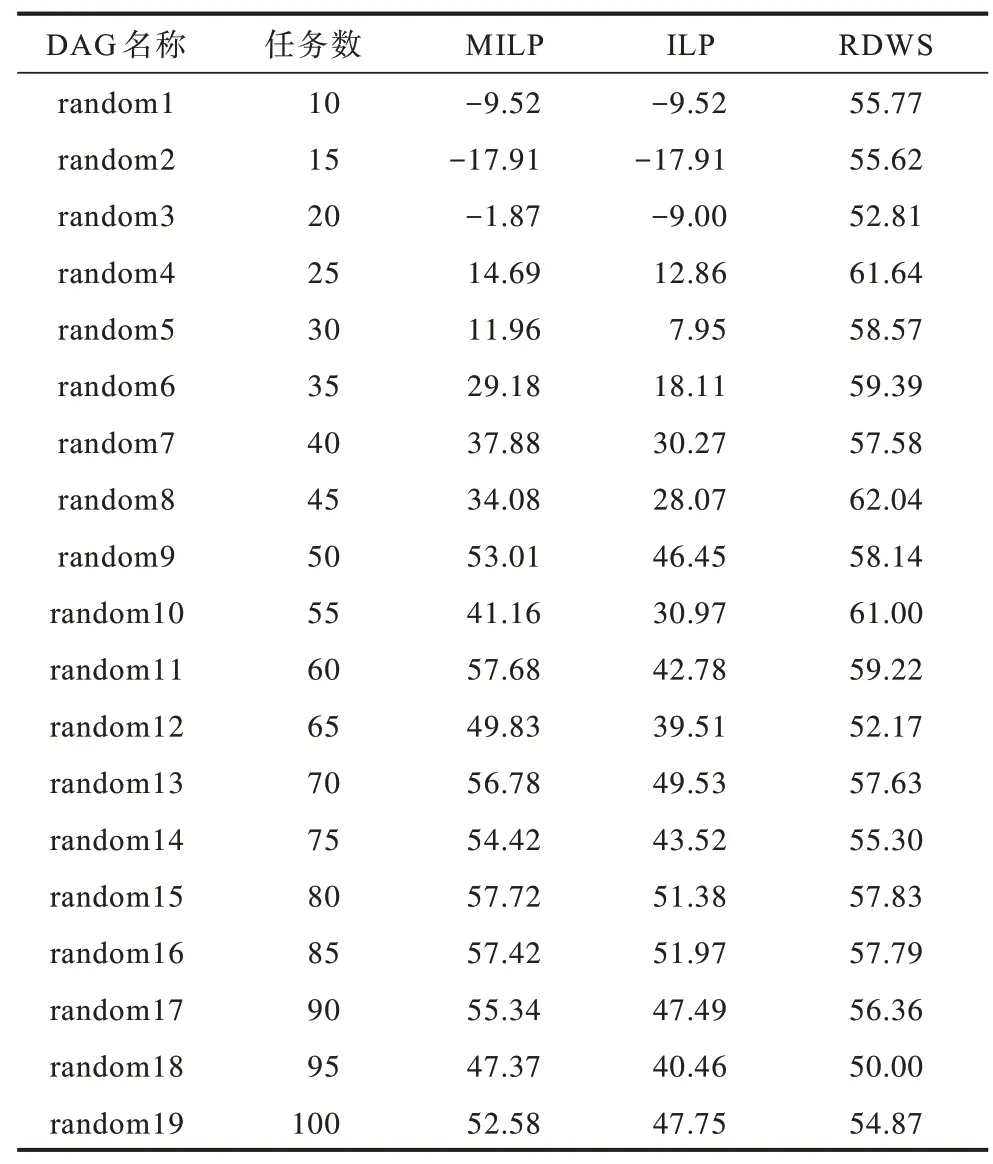

表3 为仿真实验的结果数据,包含DAG 的调度长度和算法求解时间。

表3 本文算法仿真实验结果Table 3 Simulation results of the algorithm in this paper

为评估所提算法在波形应用调度中的性能,引入调度长度提升程度(SSLI)来计算求解性能提升程度。

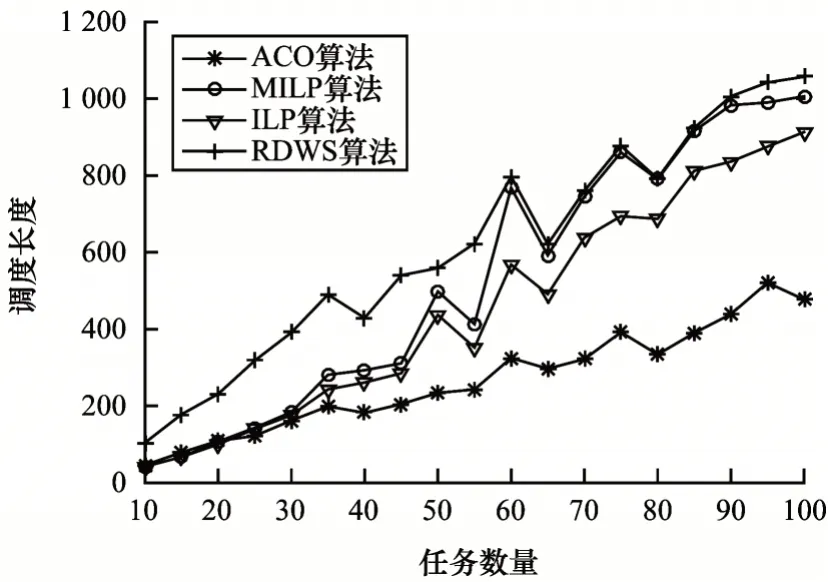

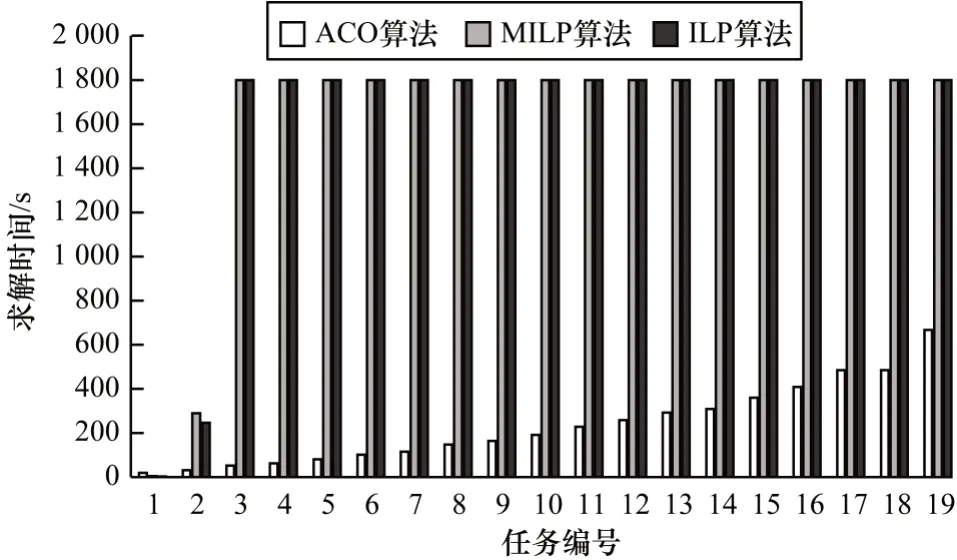

图9 分析了在面对不同DAG 规模时4 种算法的调度结果变化关系。由图9 可知,任务规模越大,本文所提算法求解性能越好,可以有效提升部署效率,减少应用的总执行时间。图10 分析了算法的求解时间变化关系。从图10 中可以看出,当任务规模大于15 时,MILP 和ILP 算法在1 800 s 内已经求不出最优解,时间复杂度远大于本文所提算法复杂度。

图9 调度长度与任务规模的关系Fig.9 The relationship between scheduling length and task size

图10 3 种算法求解时间对比Fig.10 Comparison of solution time of three algorithms

表4 所示为测试DAG 应用的SLI 数据。由表4数据可知,与没有调度的随机算法相比,本文所提算法的平均性能提升了57.04%,可有效减少SDR 系统中的软件部署和执行时间,提升硬件的资源利用率。与MILP 算法相比,当任务规模小于20 时,本文算法性能略差于MILP 算法,但随着任务规模的增大总体性能呈递增的趋势,最终平均性能提升了35.89%。当任务规模较小时,ILP 算法可在时间上限值内求出问题的最优解,求解时间也较短。但随着任务规模的增大,算法的时间复杂度呈指数级增长,任务数量大于20 时,在时间上限值内已求不出问题的最优解,求解结果差于本文算法。实验结果表明,本文算法与ILP 算法相比,平均性能提升了29.09%。综上分析,在面对大规模应用时,本文算法在求解性能和求解时间上更有优势。

表4 3 种算法SLI 分析Table 4 Three algorithm SLI analysis %

5 结束语

本文将软件通信体系架构与FPGA 的DPR 技术相结合,提出在软件通信体系架构规范下的DPR FPGA设备资源虚拟化及波形组件的部署机制。介绍基于XML域描述文件的DPR 软件架构设计,并从软件架构层面建立从波形组件到FPGA 可重构区域的映射关系。在此基础上,针对SDR 系统中支持DPR FPGA 的异构计算平台和波形应用,提出基于蚁群优化的调度技术算法。实验结果表明,与MILP 算法和ILP 算法相比,该算法能有效提升调度性能,减少求解时间。下一步将对列表启发式和搜索元启发式算法进行系统设计,以支持波形应用的实时调度。