基于SRIO交换的分布式系统功能动态重构实现

2021-12-18白海斌武宝刚张晓宇

白海斌 武宝刚 张晓宇

摘要:为满足大容量、多功能的信息处理需求,采用VPX标准、SRIO交换等技术,利用RapidIO总线高速率、低时延、高可靠性,设计了基于SRIO交换架构的多功能分布式处理系统。在RapidIO总线技术基础上,介绍了RapidIO网络拓扑和交换原理,提出了对节点功能动态重构、SRIO路由灵活配置的方案。设计实现了整体系统功能在线动态重构,以快速适应不同的功能模式和工作场景,大大提高了处理系统资源利用率。

关键词:SRIO;功能重构;RapidIO交换;VPX

中图分类号:TN919文献标志码:A文章编号:1008-1739(2021)19-55-4

0引言

随着电子信息技术快速发展和大容量宽带通信常态化,日常产生并处理数据量以及传输速率急剧增加,对信息系统的处理能力和适应场景提出了更高的要求。传统X86,PowerPC,ARM等架构的单系统环境,已经不能满足大容量信息处理的需求。采用VPX标准规范,基于串行RapidIO(SRIO)交换架构,集成X86,PowerPC,DSP,FPGA等处理资源和存储资源,构建大规模嵌入分布式系统基础平台,可为综合化信息处理系统提供解决方案,并通过动态软件加载、功能重构进一步提高资源利用率,面向不同应用形成不同功能的信息处理系统。

1 VPX标准规范

VPX是由VME国际贸易协会(VITA)组织于2007年提出的新一代高速串行总线标准,并于2010年正式发布OpenVPX标准,具有高集成度、高计算性能、高可靠性和开放互联的特点,主要面向工业、军事、航空航天领域中多处理器协同、实时的信号/信息处理应用。VPX基本规范、总线信号、结构散热、互联拓扑等内容在ANSI/VITA系列技术规范[1]中的具体定义,VITA系列技术规范如表1所示。

VPX总线由VME总线发展而来,重要变化是采用高速串行总线来替代并行总线。VPX模块之间可采用的高速串行总线主要有SRIO,PCI-E,Ethernet等标准总线,特别是SRIO总线技术已经成熟应用于高速数据传输与交换。

2 RapidIO总线技术

RapidIO总线技术主要针对嵌入式系统的芯片到芯片、板卡到板卡、机框到机框的高性能互联互通,具有高速率、低时延、高可靠和可扩展的特性,可为未来大规模分布式处理系统提供高性能数据交换和通信机制。RapidIO协议規定了总线软件接口和驱动规范,是一种基于分组数据交换的协议体系,包括逻辑层、传输层和物理层3层。其中,逻辑层定义了操作协议和包格式;传输层定义了包交换的路由和寻址机制;物理层定义了电气特性、链路控制和纠错重传。

RapidIO操作是基于请求和响应事务方式进行数据交互,包是RapidIO节点间通信的基本单元,主要定义了维护包、读/写包和消息包等数据包结构。

RapidIO包含并行和串行2种方式,目前广泛应用的是串行RapidIO,即SRIO。SRIO支持×4/×2/×1链路宽度的配置,支持每路1.25 Gbaud,2.5 Gbaud,3.125 Gbaud,5 Gbaud,6.25 Gbaud等传输速率。目前,RapidIO最新标准为4.1版[2],单路支持25 Gbaud,采用×4链路可达到100 Gbaud的带宽。

3 RapidIO交换网络

一个典型的RapidIO网络有端节点(End Point)和交换机(Switch)2个元素。不通过交换机端节点间直接互联,可构成点到点、点到多点、多点到多点网络拓扑架构[3],无交换机的网络拓扑架构具体如图1所示。

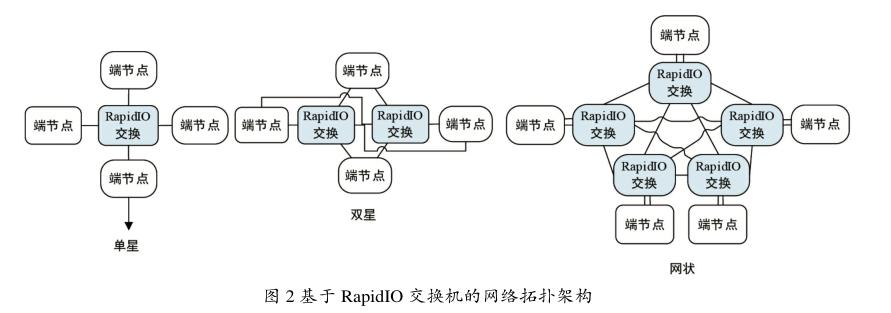

基于RapidIO交换机进行端节点间互联,可构成星状、双星、网状等网络拓扑架构,端节点间互联更加灵活,基于RapidIO交换机的网络拓扑架构如图2所示。

端节点的每一个RapidIO端口配置有器件ID号,通过ID来区分端节点设备,ID长度支持8位或16位,因此一个RapidIO网络最多可容纳256或65 536个端节点。端节点是数据包的源或目的地,源节点发送的数据包中包含源ID和目的ID,RapidIO交换机根据配置的路由转发表查找目标ID进行包转发,目的节点接收数据包,实现数据包收发。

4基于RapidIO交换的分布式系统平台设计

按照VITA协会VITA65(OpenVPX)标准,设计基于 RapidIO交换网络的分布式系统,配置2个VPX机箱,每个机箱12个槽位,设计实现了多种功能板卡,系统配置灵活支持槽位互换,提供高带宽SRIO、以太网内部全互连和对外接口。基于RapidIO交换的分布式系统平台如图3所示。

系统设计多种高性能处理板卡,包含P4080 CPU性能处理器、XC7V高性能FPGA处理器、C6678高性能DSP处理器,以及交换板卡、存储板卡,具有高性能数据处理、高性能信号处理、高带宽数据交换、大容量数据存储的能力,通过多种类型、多个节点构成了分布式信息处理系统,可满足不同应用的运算处理需求,通过动态加载各节点功能软件,分时或同时实现不同的系统功能。

系统采用SRIO作为数据平面,是板卡间高速数据交换的主要通道,整机采用双星型交换方式互联;采用千兆以太网作为控制平面(Control Plane),提供以太网全交换,用于实现各处理板卡间的控制、数据或程序加载等功能。

5分布式系统功能动态重构实现

分布式处理系统中,不同的处理节点实现不同功能,多节点共同完成系统功能。其中,基于DSP,FPGA的处理节点侧重于实现信号采集与处理,基于CPU的处理节点侧重于数据信息处理,SRIO交换则实现各处理节点间的高速信息交换。

系统功能的动态重构包含2个方面:SRIO交换网络的路由配置、各个处理节点的功能重构。本系统中,存储板卡上有不同版本、不同模式的波形软件,也支持程序远程加注存储。存储板卡作为主控单元,CPU,FPGA,DSP处理板卡作为各处理单元,SRIO交换机作为交换单元。主控单元通过SRIO网络实现对处理单元ID、交换单元路由表的配置,通过以太网络实现对处理节点的软件加载重构。

5.1处理节点功能重构

各处理节点功能重构中,主控单元运行配置管理软件,其他各处理单元与主控单元交互管理协议,完成受控波形软件加载与功能重构。软件加载与重构原理如图4所示。

主控单元作为管理核心,实现管理配置界面、任务解析、波形管理、波形库以及重构与配置管理接口。采用基于TCP/IP的波形重构与配置管理协议,主控单元读取各个处理单元的状态,并根据任务解析情况按需将各类波形软件以配置文件bin、可執行文件、脚本或配置参数等各类形式下发到各个处理单元。各个处理单元完成波形的加载重构或参数的更新。主控单元还提供波形库以及波形库的管理,根据任务需求增加、更新或删除波形,完成波形的管理。

以FPGA型处理板卡为例,板卡上协处理器运行配置管理代理,提供与主控单元管理总线的接口,通过解析配置协议,完成波形文件接收与本地更新,并将波形文件通过板卡内部管理接口转发至管理FPGA,管理FPGA通过SelectMap[4]方式将波形文件加载到目标FPGA。同样,主控单元可以发送参数配置,完成各个处理单元的配置参数更新或当前波形下的工作模式切换等功能。

5.2 SRIO交换的路由动态配置

在系统中,由于SRIO交换机之间以及与各个处理节点的物理连接是固定不变的,因此要改变节点间互联关系,则需改变的是交换芯片的路由转发表,即端口与目标ID的映射关系。完整的SRIO启动及配置流程包括:系统初始化、设备器件枚举、SRIO路由表配置、存储器映射,由主节点控制完成。

器件枚举采用广度优先或深度优先的算法遍历SRIO网络,以发现系统中所有SRIO节点并为其分配唯一的器件ID。SRIO路由表配置有3种方式实现:JTAG,I2C,RapidIO维护包[5]。其中,JTAG用于设备交换器件调试中进行路由表维护,I2C接口配置管理是通过预先固化到EEPROM中的初始化路由表信息进行上电配置,这2种方法均有局限性。

本文采用了RapidIO维护包方式,对整个SRIO网络中任意端节点和交换器件的能力寄存器、状态寄存器[6]和数据结构实时动态访问控制。与静态路由配置相比,采用RapidIO维护包可根据枚举阶段记录的节点互联信息以及当前系统任务规划、功能部署情况,计算互联最短路径,实时配置和动态维护SRIO路由表,配置维护灵活快捷,大大提高系统工作效率。路由表配置流程如图5所示。

6结束语

基于SRIO交换架构的分布式处理系统满足了对数据交换高性能、大带宽、低时延和高可靠的需求,通过SRIO节点功能的动态重构、SRIO交换的路由灵活配置,实现系统功能在线动态重构,快速适应不同的功能模式和工作场景,大大提高系统资源利用率,可广泛应用于卫星地面关口站、雷达信号地面处理中心、机载/星载/舰载数据处理系统等大型综合电子信息系统。

参考文献

[1] ANSI/VITA 46.0-2019: VPX BASELINE[S/OL].https://www. vita.com/,VMEbus International Trade Association (VITA)/VME2019.

[2] RapidIOTMInterconnect Specification 4.1[S/OL].https:// RapidIO. org, RapidIO Trade Association/RapidIO2017.6.

[3] FULLER S.RapidIO:The Embedded System Interconnect[M].USA: John Wiley&Sons Inc, 2009.

[4] Xilinx. 7 Series FPGAs Configuration User Guide[EB/OL]. https://www.xilinx.com, 2018.

[5]邓豹.RapidIO交换互连与配置管理研究[J].航空计算技术, 2014,44(2):124-127.

[6] Renesas Electronics Corporation. CPS-1848 Datasheet[EB/OL]. https://www.renesas.com, 2019.