新型垂直导线印制电路板信号传输的优越性

2021-12-08孙丽丽唐子全解福洋

孙丽丽 唐子全 解福洋

(沪士电子股份有限公司,苏州 昆山 215301)

根据行业的发展方向,以及系统级芯片和现场可编程逻辑门阵列(FPGA)型技术的发展路线,就会试图在印制电路板(PCB)之外的有机基板上研发更多可能。这种发展方向有利于将其推向高性能发展的前沿。紧随其后,通过某种工艺,其系统可以被利用或转移到PCB中,这正是一些工程转化过程发挥的作用。这和已经到来的400G高频技术发展一样,因为连接器和PCB技术的问题,我们正在开发相应的产品以支持这一发展趋势。例如最初开发的光纤互连技术与电缆互连技术,受限于与连接紧密性与PCB现有的技术,导致并未很好地支持400 G的发展。但从长远来看,希望将这种系统构建到更紧密的互连中,而这正是PCB的机会所在。并且,即使是下一代产品,也可能需要这些芯片更紧密的布局,在这种情况下,跳线连接可能不是最为理想的方法[1]。

新的垂直导体结构(VeCS:Vertical Conductive Structure)技术可以减少层数,并且无需顺序层压技术就可提升信号完整性。VeCS与传统的通孔、微导通孔及微孔任意层互连设计不同,后面这三种技术成本高且需要多次层压、钻孔和电镀周期才能制造出合理的层数。使用VeCS技术可整合布线通道,更好地利用通道实现引脚数较多器件的扇出。更多的布线通道可以在更可靠/坚固的平面基准下实现更多的布线。

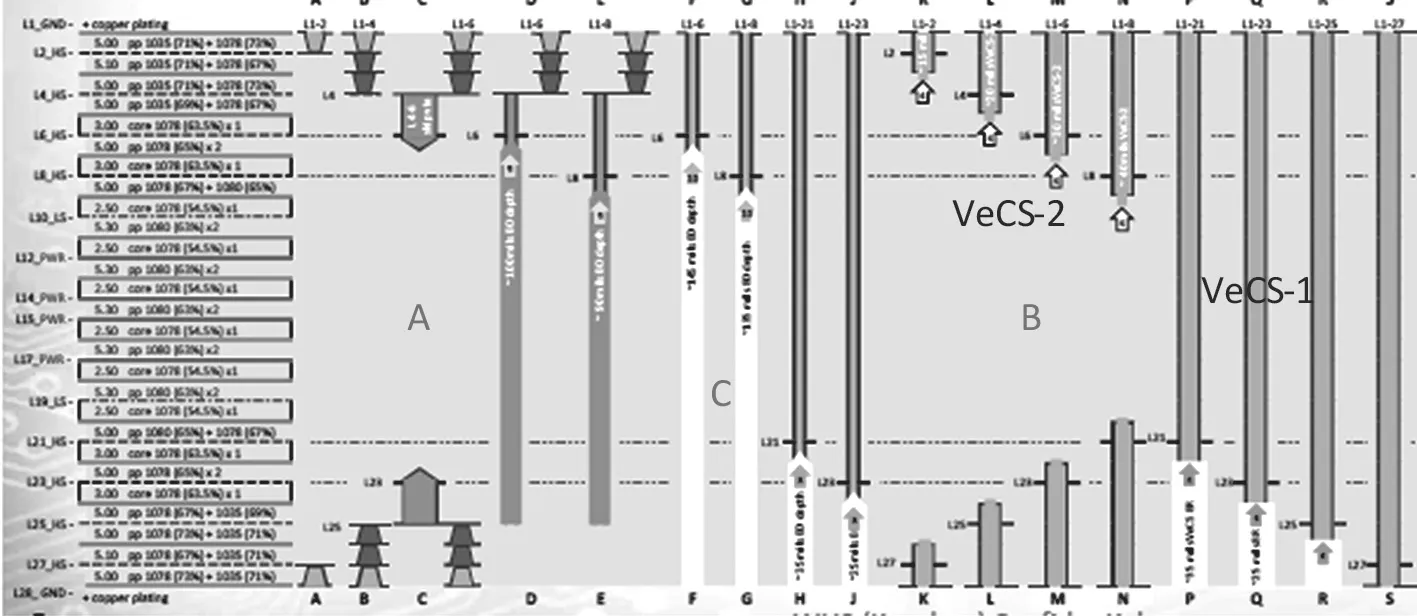

传统HDI(高密度互连接)的叠加孔设计需要经过多次压合和多次激光钻孔,如果HDI的叠孔替换为VeCS,则只需要进行一次压合与一次电镀。VeCS的结构为厚度25 μm的垂直铜柱,如图1中的B区所示。传统的高速信号板多会背钻去掉孔多余的长度,因为这部分长度会对信号产生谐振,与背钻孔相比VeCS有两项优势,第一是VeCS柱状体的总面积比孔小,总电容少,电容性降低对信号的插损有很大帮助,第二个优势是VeCS-2可以控制高度,可以一次完成想要的高度不需要二次背钻,而且残根(stub)长度可以控制在0.10 mm以内,这种控制高度的VeCS不仅残根短,它同时带来另外一个好处是原来的背钻的区域可以用来布线或者在相反面布孔,如图1的B区。

图1 Via 与VeCS 结构差别

我们去年对垂直导体结构(VeCS )技术与传统通孔技术进行了可靠性的比较分析,其中VeCS与传统通孔使用的材料均为M**,叠构相同,孔间距相同。从测试结果看VeCS的CAF(导电性阳极丝)在测试条件为85 ℃/85 RH 偏压100V的条件下可以完成1000个循环测试,与同等叠构的通孔PCB结果并无差别 IST(互连强度测试)的测试条件为25~150 ℃测试500次循环,VeCS的表现极为优秀的结果可以参考《新型垂直导电体PCB与传统导通孔PCB之可靠性能与信号性能博弈》[2]一文。

1 实验设计

1.1 测试板的设计

今年我们与清华长三角研究院共同设计了VeCS与Via信号性能比较的测试板。对VeCS信号性能进行了初步的研究,其中测试样品的结构如图2所示。

实验设计中主要包含:(1)包含通孔的残根长度对插损的影响如以下几点。(2)在相同残根长度条件下VeCS与通孔的阻抗和插损比较;(3)VeCS宽度对阻抗和插损的影响。

1.2 测试设备

测试设备及夹具信息见图3所示。

2 实验结果

2.1 PTH 通孔残根长度对信号的影响

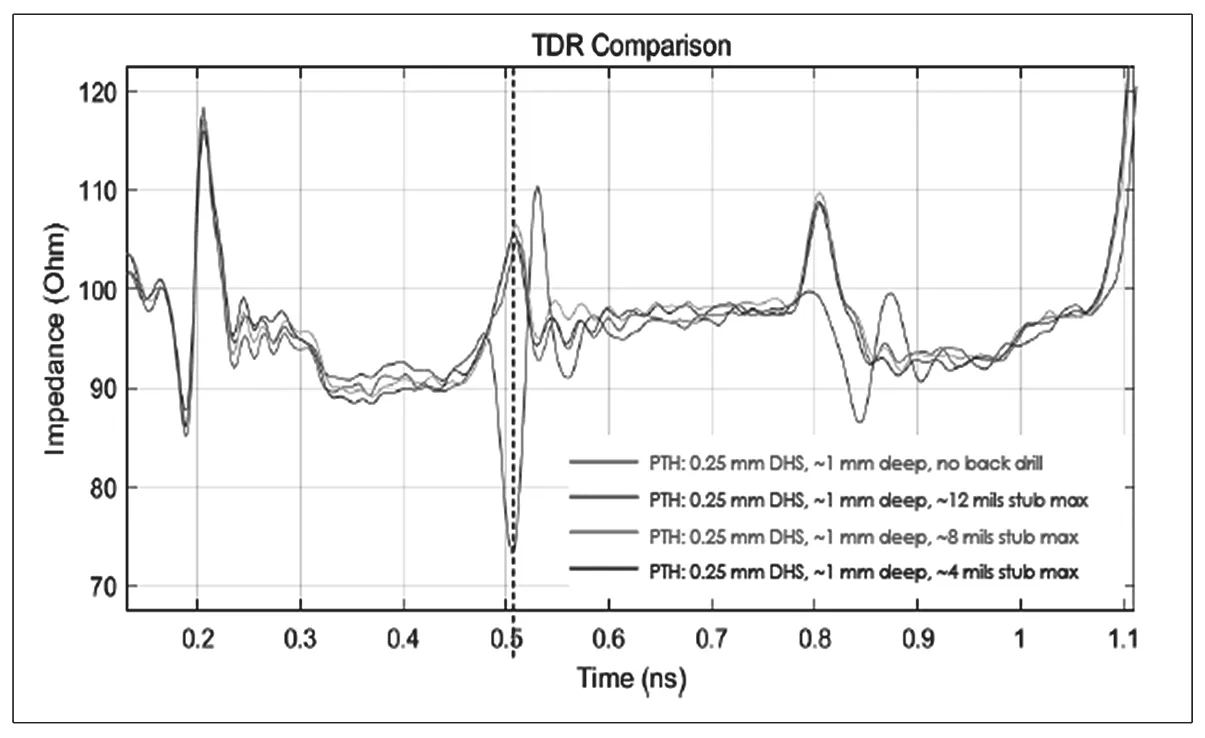

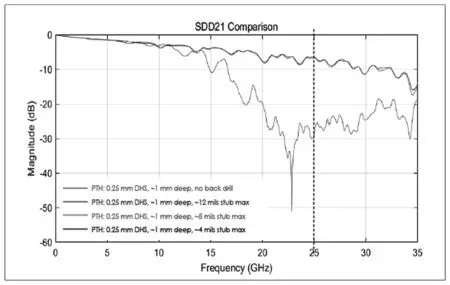

图4与图5中曲线是PTH(0.25 mm)无背钻、有背钻而残根长度不同的导线性能。没有进行背钻的孔明显阻抗出现下陷现象,当传输信号时这种下陷会导致信号的谐振问题,如图4的插损比较。而背钻孔的位置阻抗呈现为波峰,这说明这个孔的阻抗与内层线路的阻抗不一致,此孔的阻抗可以通过调整焊盘来获得相匹配的电阻。

图4 不同残根长度的阻抗

图5 不同残根长度的插损

2.2 PTH 背钻孔与VeCS 垂直导体的信号比较

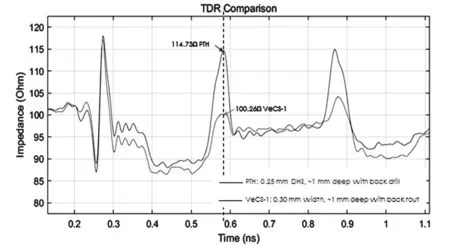

背钻孔与背铣VeCS的阻抗比较如图6所示。

图6 背钻孔与背铣VeCS的阻抗比较

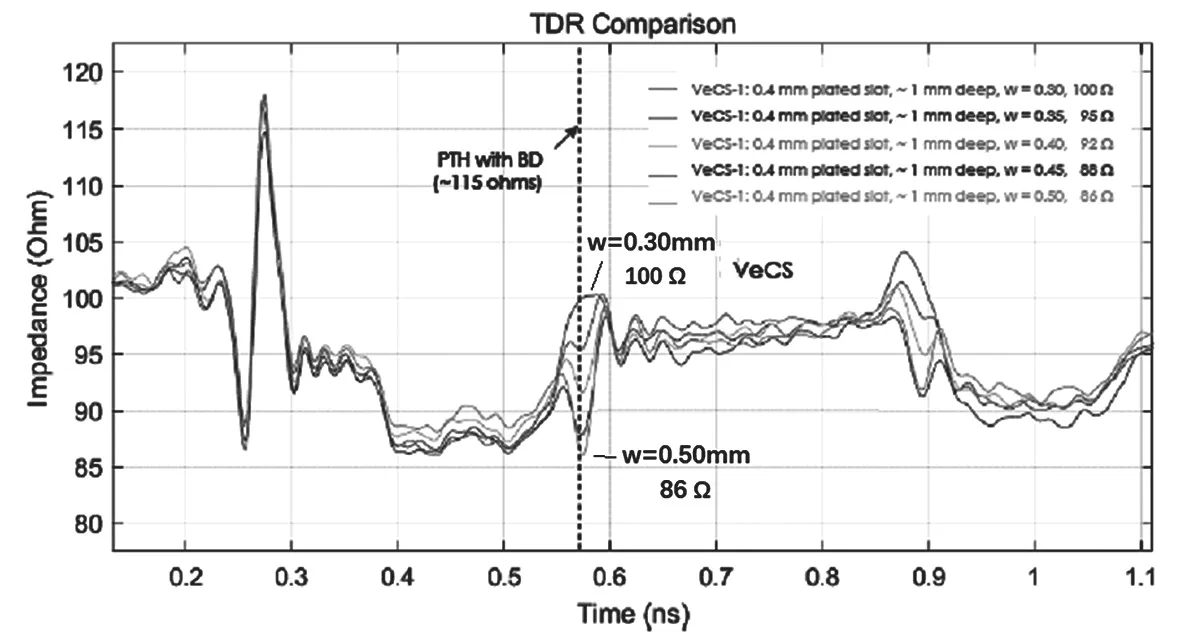

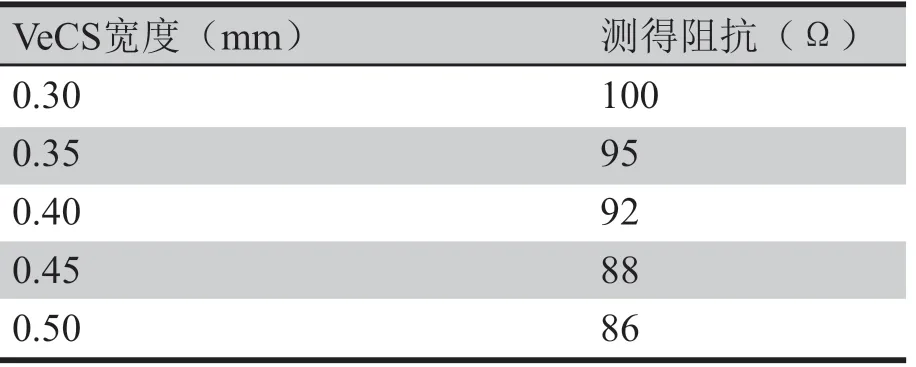

当残根长度相同的条件下,VeCS的阻抗比背钻通孔的阻抗要小,并且可以调整到目标值100 Ω,此项测试结果可以证明VeCS的阻抗可以根据需要进行调整。如表1和图7所示,宽0.4 mm槽孔的不同VeCS宽度的阻抗。

图7 不同VeCS宽度的阻抗

从表1可以得到,随着VeCS宽度的增加电阻下降,依据上表的结论VeCS的阻抗可以调整到与线路的阻抗相一致。当过孔阻抗与内层线路的阻抗相一致的时候,信号传递的时候的额外损耗会降低从而信号更加平稳的传输。

表1 不同VeCS宽度的阻抗

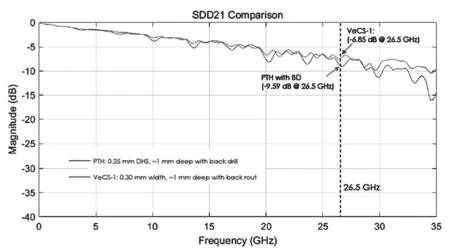

从图8可以得出,由于外层线路的设计问题,信号线有抖动但是我们依旧可以得出在相同残根长度的条件下,在26 GHz频率下VeCS的插入损耗比背钻孔的阻抗小29%,因此VeCS对高速信号传输相对孔而言具有很大的优势,迫于夹具的限制我们目前只可以测试至26.5 GHz。下一步我们会优化设计减少信号线波动突破更高频率的设计,以证明VeCS在信号在高频上的优势。[2]

图8 背钻孔与背铣VeCS的插损比较

3 结论与下一步计划

从以上的分析可以得出在相同的设计条件下,VeCS的阻抗可以根据需求调整到需要的阻值,在相同条件下在26.5 GHz时VeCS的信号传输性能优于传统背钻孔的性能。这一次的实验结果看到外层线路阻抗的不匹配导致阻抗内外层不一致,这也会影响VeCS的信号结果。

同时此次实验结果可以看到VeCS具有高频优势,但受到夹具的限制,所以下一步设计计划需要调整夹具能匹配40 GHz+的测试条件,同时也要完善内外层阻抗保持一致。