一种基于虚拟仪器的军用计算机总线仿真技术*

2021-12-01万岳

万 岳

(中国船舶重工集团公司第七二四研究所 南京 211100)

1 引言

在自动化测试诊断系统中,需要对ISA、EISA、I2C、存储器等基于数字总线的设备进行测试,通常采用ISA等总线主控制器+接口适配器的方式,通过总线主控制器与被测对象(UUT)进行通讯,输出激励、采集反馈信号,完成自动化测试诊断工作。传统的方式能够实现总线操作,但是属于专用测试设备,直接影响设备的通用性,同时,设备结构无法精简化,导致部署空间、购置成本增加。本文采用通用型数字IO模块,提出一种基于通用IO的复杂数字总线仿真方法,以复杂的计算机ISA总线为验证目标,采用图形化操控方式,实现IO空间与存储器空间读写操作,完成板载寄存器读写、内存读写等操作。结果表明,基于通用IO的复杂数字总线仿真方法可以模拟仿真ISA、EISA、AT BUS、SCSI BUS、MULTIBUS、I2C等数字总线操作,对总线测试诊断、局部总线通信等设计开发具有参考价值。

2 传统测试诊断系统架构

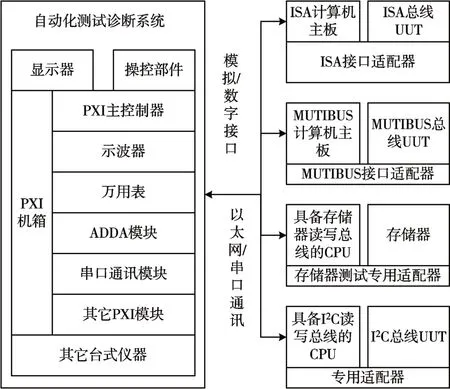

自动化测试诊断系统一般采用VXI、PXI、LXI等测试总线,VXI、PXI机箱集成主控制器、示波器、万用表、ADDA模块、串口通讯模块等虚拟仪器,配齐操控组件与其它外围设备,构成自动化测试诊断系统[1]。

对于ISA、EISA、MULTIBUS、I2C、存储器等数字总线被测对象,一般采用总线主控制器+接口适配器方式,实现与被测模块的数字通讯,组成架构如图1所示。

图1 传统总线测试系统架构

以ISA总线测试为例,设计专用接口适配器,上面配置ISA总线计算机主板,主板通过适配器与被测ISA总线模块(视频板、异步串口板等)通讯。测试程序运行在测试PXI主控制器上,测试指令通过网络或串口发送给ISA主板,ISA主板转换为总线读写操作,进而实现对被测模块的功能测试。

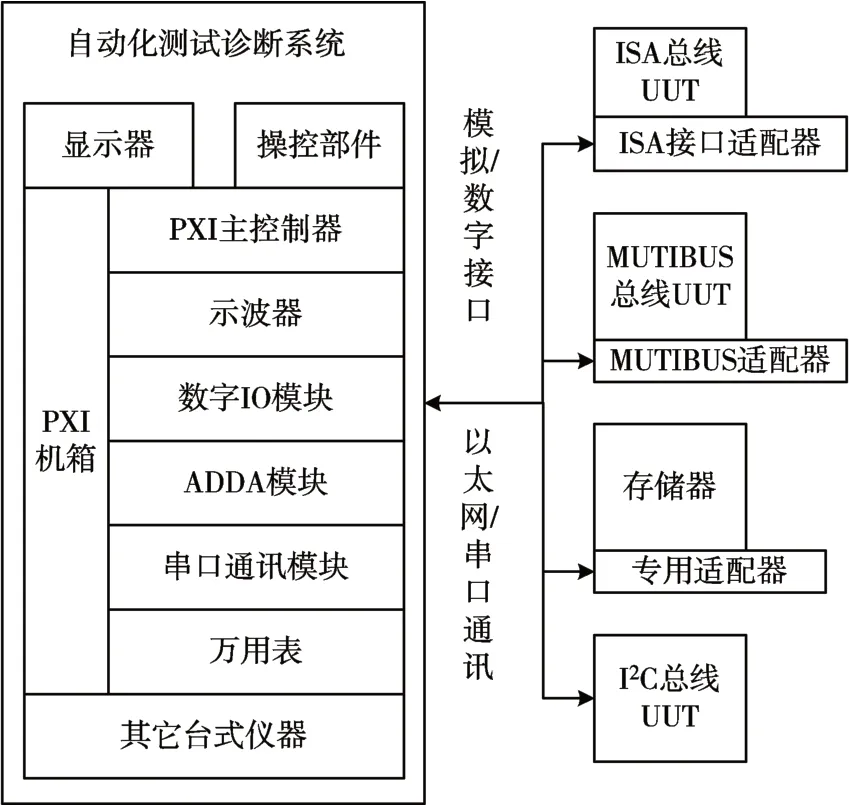

采用通用IO模块的测试系统框架如图2所示。

图2 基于通用IO模块的测试系统框架

在PXI系统中,不再配置总线计算机主板,配置通用数字IO模块,采用软件控制数字通道,模拟总线信号交互过程,实现总线操作。由于被测UUT接口在电气、物理结构上多样,专用接口适配器实现接口适配功能。对于数字接口简单的模块,如I2C模块,可以直接采用适配电缆。由于采用数字IO模块,通过软件适应各种总线操作需求,进一步提高测试系统的通用性与经济性。

3 通用数字IO仿真技术

3.1 数字总线仿真对通用数字IO的技术要求

通用IO模块需要模拟仿真ISA、EISA、MULTI⁃BUS、I2C等数字总线操作,实现完成的完整的数字激励—响应测试,因此,通用IO模块主要技术要求如下。

1)由于总线操作涉及读写,数字IO通道具备必须输出与输入双向控制功能;

2)考虑到计算机总线的电气特性,数字IO通道信号逻辑电平标准为TTL与CMOS;

3)除高低电平基本逻辑状态,需要提供高阻状态,确保不会多设备同时驱动导致的总线冲突;三态是I2C通信、IC测试和通用数字激励/响应测试等双向应用必要特性;

4)由于总线测试,涉及大规模的数据交互,大量激励数据与采集数据需要存放在数字IO模块上,因此通用数字IO模块需要大容量的板载内存;

5)具备内时钟与外时钟同步能力。内时钟输出,是同步外部被测模块总线操作;外时钟输入,是同步自身总线操作;

6)考虑到计算机总线特性,建议数字IO通道可以按照8路为一组成组控制,降低控制难度;

7)由于测试诊断系统工作性质,被测对象与PXI板卡之间往往有电缆连接,单端信号电缆传输,会带来信号完整性问题。因此,高速的总线信号如CPCI[2](33MHz/66 MHz),推荐采用计算机主板+接口适配器方式;采用通用数字IO模拟总线方式,建议总线运行速率控制在20MHz以下。

3.2 PXI数字IO模块

本项目采用的PXI数字IO模块,主要技术指标如下。

1)单模块48通道;

2)内置同步机制,支持多模块数据通道并行扩展;

3)标准PXI接口,32位PXI总线,即插即用;

4)每通道64Kbit存储深度;

5)I/O通道电平标准:TTL兼容;

6)两种操作模式:动态/静态;

7)最大猝发速率:40MHz。

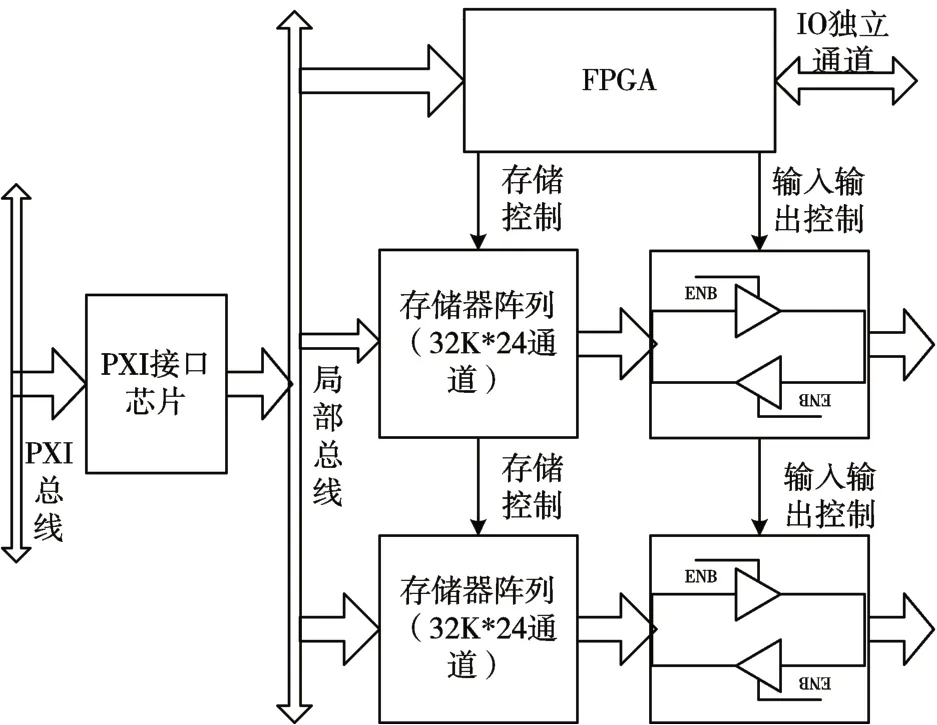

单块原理框图如图3。

图3 数字IO模块框图

PXI接口芯片把PXI总线操作转换为局部总线。FPGA作为模块控制器,负责存储控制、输出控制、单独IO控制,同时负责整个模块的管理与时序控制。存储器阵列负责存储多通道大容量数字激励文件与采集文件的存储。输出输入控制部分负责输出逻辑三态控制。

3.3 模块的工作流程

IO模块在启动后,进行初始化操作,设置相关模块基本参数。然后处于等待状态,接收总线命令。

由于涉及多通道大数据量数字量的读取控制,激励文件与采集文件都是存放于存储器中。待读写完成后,通过中断方式,通知主控制器操作存储器数据,进行后续数据处理。

3.4 IO通道数据文件

激励文件(写操作)与响应数据(读操作)文件都是数字IO逻辑状态的数据文件,在文件中,按照输出时拍(操作时钟的一个周期)记录所有通道的逻辑状态。

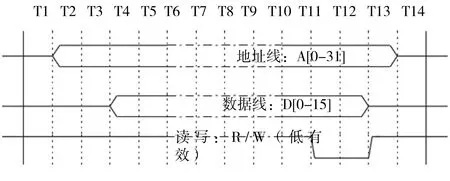

以总线写操作为例,需要占用十四个时拍(T1~T14),激励波形如图5。

图5 写操作示意图

其中,数字IO通道与信号的对应关系,在模块工作参数设置时确定。在激励文件中,地址线在A[31-0]在T2-T13有效,D[15-0]在T4-T12有效,写信号在T11-T12有效。

从中可以看出,对于多通道大数据量数字总线模拟操作,激励文件的生成成为关键,采用人工方式效率低,无法满足研发进度需求,必须采用自动化方式。

4 ISA总线仿真-视频图形板测试

4.1 ISA总线概述

ISA是16bit的计算机系统总线,最大传输速率为16MB/s,允许多个CPU共享系统资源。虽然运行速率低,但是由于兼容性好,在PC104等产品中广泛使用。

ISA总线包括地址总线SA19-SA0、数据总线AD15-AD0、中断信号等[3]。与总线仿真操作重要的控制信号为

1)BALE:地址锁存信号;

2)IORC#:IO空间读信号;

3)IOWC#:IO空间写信号;

4)MRDC#:存储器空间读信号;

5)MWTC#:存储器空间写信号。

System Clock是一个自行运转的时钟,频率在7MHz~10MHz之间。

4.2 视频图形板仿真测试

1)视频图形板

视频图形板由主机接口、图形系统处理器、存储器、调色板五部分组成。

其中,主机接口用于完成图形系统处理器与主机之间的通信控制;图形系统处理器用于完成图形加工与显示控制;存储器、调色板(RAMDAC)完成图形、数据、程序的存储与视频信号的生成。

2)测试项目

本项目共配置4块PXI模块,具备192路数字IO并行仿真测试能力,能够满足ISA总线仿真需求。

主要测试项目:

(1)主机通讯测试;

(2)VRAM测试:地址总线测试、数据总线测试、存储单元测试;

(3)DRAM测试:地址总线测试、数据总线测试、存储单元测试;

(4)FLASH测试:存储单元测试;

(5)调色板测试:寄存器测试、内部调色板空间测试。

在测试中,涉及大量存储器操作,如地址总线测试、数据总线测试、存储单元测试等,为此编制了激励文件专用生成器,自动生成大容量数据文件。

4.3 测试结果

测试程序启动后,程序自动运行,并把测试结果在进度状态对话框中反馈。测试中如有故障,其故障结果在实测值中显示,方便使用人员记录故障原因。

5 结语

在传统总线测试系统架构分析的基础上,基于通用型数字IO模块,本文提出一种基于通用IO的复杂数字总线仿真方法,设计数字IO模块工作流程、底层驱动方式。以复杂的计算机ISA总线为验证目标,针对视频图形板,采用自动化测试向量生成器,进行IO空间与存储器空间读写操作,实现板载寄存器读写、内存读写等操作。验证结果表明,基于通用IO的复杂数字总线仿真方法可以模拟仿真ISA、EISA、I2C等数字总线操作,对总线测试诊断、局部总线通信等设计具有参考价值。