电机转矩转速性能测试系统设计

2021-11-28姚碧辉竺春祥邓立唯王斌锐

姚碧辉,竺春祥,邓立唯,王斌锐

(中国计量大学 机电工程学院,浙江 杭州 310018)

电机测试的准确度和便利性在电机的生产评价过程中占据了重要的地位。在电机测试中,台架测试为主流的测试方法[1],即在国标要求下,先将电机置于一定的工作条件,如相应的负载、转速、温度、湿度等,再通过各种技术手段采集电机的各项工作参数[2]。其中包括电参量和非电参量,电参量主要包括电压、功率、效率等,需要通过一定的调理电路来获得。而非电参量主要包括转矩和转速信号,一般通过传感器来获得。

现行的测试系统有许多缺陷,大多测试系统的信号采集处理模块和控制输出模块是两个独立的模块,无法实现闭环测试的功能。而兼顾采集和输出的系统大部分情况下功能单一,只能在单一的测试平台中的针对性测试项目中使用,可升级性较差,无法兼容现在基于负载模拟等研究的各种测试项目[3]。

因此,本文研制一套用于电机-测功机测试平台的测试系统,舍弃现在常用的板卡结构,将采集和输出功能兼容在一个较小的核心板中,在能够高速高精度采集转矩转速信号的同时,可以输出多种模拟信号,甚至任意输入的外部信号,在满足基本测试要求的同时还提供更多样的测试可能。

1 系统设计原理

1.1 系统结构设计原理

非电参量测试的结构如图1[4]:被测电机的运动轴与测功机的运动轴通过联轴器相连。通过电机测试系统给控制系统命令,令控制系统输出电机控制器的相应参考信号,分别控制被测电机和测功机,以此来模拟电机的工作条件。而联轴器中间接转矩转速传感器采集电机的非电参量,并反馈给控制系统。

图1 电机-测功机平台示意图Figure 1 Schematic diagram of motor-dynamometer platform

为了实现可以搭载复杂系统的测试平台,鉴于FPGA时钟频率高、内部延时小、逻辑速度快的优点[5],结合STM32强大的内核,成熟的开发体系和丰富的外设资源[6],该测试平台设计使用FPGA结合STM32的双核心体系。

具体设计框图如图2,FPGA和STM32使用FSMC进行通信,在FPGA中实现数据采集测量和模拟控制量输出的功能,在STM32中进行上位机通讯,实现数据中转和人机交互的功能。

图2 电机测试系统功能示意图Figure 2 Schematic diagram of motor test system function

1.2 模拟量输出设计原理

为了满足实际中复杂多变道路环境的高精度模拟,结合现行电机测试系统的设计参数,设计模拟信号的输出频率范围为1 Hz~1 MHz,模拟信号可以输出标准的正弦波信号,方波信号和三角波信号,标准信号的频率幅值相位等均可调。还提供外部信号类型输入,峰峰值范围为1~10 V,输出误差低于1%。

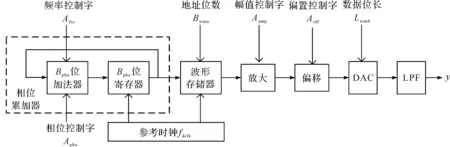

根据上述设计要求,该模块选择使用直接数字合成(Direct Digital Synthesuzer,DDS)原理。这种技术不仅可以产生高带宽高精度可变频的各种调制信号,同时还能产生用户自定义的有限带宽任意信号。并且该技术产生的波形输出相位是连续变化的,具有很好的频谱特性[7]。图3为该系统的DDS的设计原理图,与基础DDS设计相同,由参考时钟、相位累加器、波形存储器、DAC和低通滤波器(Low Pass Filter,LPF)组成。图3中,fdclk为参考时钟频率,Afre为频率控制字,Bpha(为相位累加器位数,Bwma为波形存储器地址位数,Lwmd为波形存储器的数据位字长和DAC位数[8]。

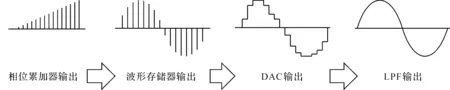

DDS系统的核心是波形储存器,即对目标波形做离散化处理后将数字信息通过存储技术在硬件中进行储存,每个数据都有相应的地址位,然后在软件中做相位累加器,对波形储存器做循环寻址,将目标地址的数据按顺序输出给DAC进行连续的输出,生成离散的波形图像,最后通过LPF生成连续平滑的目标曲线,具体生成流程如图4。

图3 系统DDS设计原理图Figure 3 Schematic diagram of DDS design in the system

图4 DDS模拟信号生成流程图Figure 4 DDS analog signal generation flowchart

频率控制字实际上是波形存储器中的地址增量值,即寻址步长,根据参考时钟fdclk的频率在加法器中进行累加,当相位累加器溢出后,再开始寻址的下一个周期。重复输出波形储存器相应地址的寄存数据,生成一串连续的离散信号。因此,频率控制字Afre越大,相位累加器产生溢出的速度越快,完成一个输出周期的速度就越快。所以改变频率控制字,可以改变输出波形的频率,输出频率为

(1)

当Afre=1时,系统有最小分辨率,即

(2)

在此基础上,在相位累加器中设置初始相位Apha,实现对初相位的设置,对波形储存器的输出进行Aamp倍的放大,对幅值进行控制。对完整波形进行Aoff位的偏移,即可实现偏移功能。因此瞬时输出为

y=AampF(TAfre+Apha)+Aoff。

(3)

DDS误差主要来源有相位截断,幅度量化和DAC的非理想特性。具体来源如图5。

图5 DDS误差模型Figure 5 DDS error model

相位截断误差是由相位累加器的位数大于波形存储器地址宽度造成的[9],误差的平均功率为[10]

E[Pa]=(-6.02Lwmd-4.77)dB。

(4)

幅度量化误差是由波形存储器的字长限制造成的,误差的平均功率为[10]

E[Pp]=(-6.02Bwma+8.18)dB。

(5)

而DAC误差是由器件误差造成的,可以通过选择精度更高的DAC进行改善[11]。

根据式(4)和式(5),当Bwma=Lwmd+2时,相位截断误差和幅度量化误差的噪声功率差不多,因此Bwma的取值一般可以选择等于或稍大于Lwmd+2。

1.3 数据采集模块设计原理

在GB/T18488.2—2015《电动汽车用驱动电机系统 第2部分:试验方法》中,对电机测试的取点原则进行了规定,即取点必须包含必要的特征点[12]。而现在先进的电动汽车电机,加速时间已经低于3 s。为了满足在短时间内采到足够多的点来覆盖标准点,系统设计为最低1 ms的采集测试时间。再综合考虑市面上的先进产品,设计测频最大误差为0.1%。

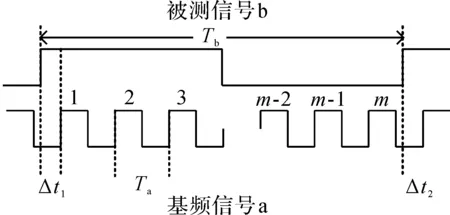

与此同时,该系统应用的数字式转矩转速传感器JN338的输出最大频率为6 000 Hz,综合测试频率范围和对于测试的实时性要求,该系统选择测周法(T法)作为系统的测频模块设计方法。

图6为测周法的原理图,信号b为被测信号,信号a为参考信号,通过测量信号a在被测信号b周期内计数次数m,用计数次数m乘以Ta,其中Ta是信号a的周期,得到的结果可以近似为被测信号的周期时间长度Tb:

Tb=mTa。

(6)

考虑到测试上升沿的时间差,测试误差为

ΔN=Δt1-Δt2。

(7)

而信号b的测量精度为

(8)

图6 测周法原理示意图Figure 6 Schematic diagram of the cycle- measuring method

根据上节分析,在精度要求为0.1%的情况下,最大输出频率为6 000 Hz,所以基频在大于等于360 MHz时满足测试要求。

该系统选择了Altera Cyclone Ⅳ系列的FPGA,基频为120 MHz左右,最高可倍频到600 MHz,为了满足要求,选择将基频倍频到400 MHz,即满足设计要求,也不过于高频影响设计的基本时序。被测频率的计算公式为

(9)

式(9)中,f为被测频率,m为基础频率计算数量,即输出数据。

根据转矩转速传感器的计算公式,可以得到被测的转矩转速与被测频率的关系如式(10)~(11)所示。式中,n为转速,Mp为正向转矩,Mr为反向转矩,N为转矩满量程,f为实测转矩输出频率值,fp为正向满量程输出频率值,fr为反向满量程输出频率值。

n=f,

(10)

(11)

(12)

因此转速转矩和系统中的采集计数值的关系为

(13)

(14)

(15)

其中mT和mv分别为转矩测试输出频率的系统计数值和转速测试输出频率的系统计数值。

1.4 数据储存中转原理

为了保证数据的连续性,系统分别在FPGA和STM32上都设计了两个ROM缓冲区用作乒乓操作,乒乓模块的原理如图7[13]。

图7 乒乓操作示意图Figure 7 Schematic diagram of ping-pong operation

图中黑色箭头为数据流方向,为模块设计一个开关,当Bank A未满,Bank B满时,开关为开,数据流如图7所示,输入数据选择进入Bank A,而Bank B的数据输出,再经过FSMC到STM32。当Bank A存满后,将Bank B清空,新的数据再进入Bank B,由Bank A输出数据。周而复始,达到数据的稳定传输。

双核心板之间的通信使用FSMC总线协议[14],而STM32与上位机的通信使用LwIP协议[15]。

2 系统硬件选型设计

2.1 输出模块硬件选型

本文设计采用AD9767为波形发生主芯片。AD9767是一种高速处理芯片,其中信号以电流的形式输出,满量程输出为20 mA。在实际应用中,使用了ACM9767的DA集成模块,该模块在DA芯片输出口,使用两级运算放大电路,第一级将输出放大为-1~+1 V,第二级将输出放大到-5~+5 V。

2.2 输入模块硬件选型

电机转速传感器输出信号可能包含电机干扰,需要在FPGA和传感器中间设计一个隔离模块,保护系统不受输入端干扰甚至损坏。为了高性能和压缩空间,该系统选择ADUM1210隔离模块,该芯片为高性能双通道数字隔离器,低频通道宽度失真低于3 ns,带宽达到10 Mbps,满足系统设计需求,硬件电路设计图如图8。

图8 隔离电路设计图Figure 8 Isolation circuit design diagram

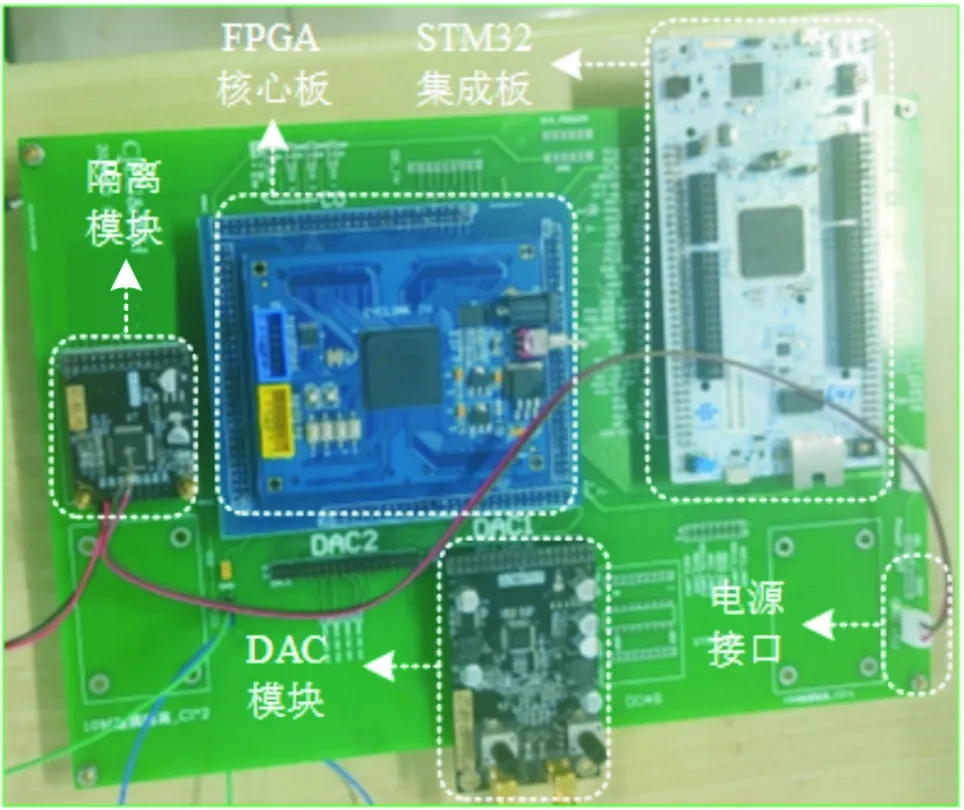

2.3 底板整体设计

在选择完核心硬件后,还需要将硬件模块集成到一个底板上,由于输入输出信号涉及到高速高频,为了保证数据的准确传输,在底板设计中需要对同一数据源的线路进行等长处理,最后设计完成的集合板如图9。

图9 系统底板实物图Figure 9 Physical map of the system backplane

3 系统软件设计

3.1 FPGA软件设计

3.1.1 模拟量加载模块

信号加载的设计使用DSP Builder的设计方法,在Matlab/Simulink中直接对整个系统进行设计模拟,仿真成功后,通过Signal Compiler对模型进行编译,生成可以直接导入FPGA软件的程序文件模拟量加载的实现框图如图10,该系统设计采用位宽14位的DAC来进行波形的数模转换,分辨率可以达到1/214。根据上文的误差分析,正弦波的波形存储器地址位数设计为14+2=16,因此寻址范围达到216=65 536个点。系统时钟fdclk为100 MHz,相位累加器的位宽为27,由此计算频率的最小分辨率为

(15)

对Simulink模型验证无误后,打开模型中的Signal Compiler模块,设置好相应参数后,把模型文件转换成VHDL代码、综合及Quartus Ⅱ适配。最后生成.qip文件,在工程中将该文件进行例化。

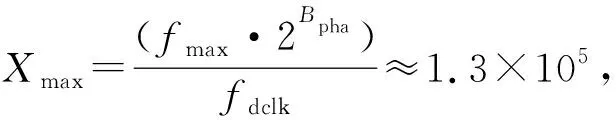

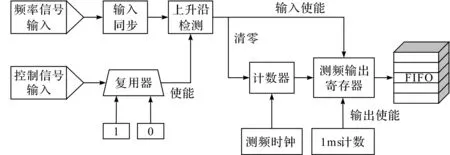

3.1.2 数字量采集测试模块

该模块直接在Quartus Ⅱ中对代码进行编写,在设计中使用测周法对频率进行测试,具体设计框图如图11,对输入信号先进行同步,再进行边沿检测,然后对基频进行计数,到第二次上升沿到来后,将计数值送入寄存器。而为了保证数据的时序,对输出设置使能,1 ms输出一个数据入FIFO。

图10 DDS软件设计原理图Figure 10 DDS software design schematic diagram

图11 测频软件设计原理图Figure 11 Schematic diagram of frequency measurement software design

3.2 STM32软件设计

为了保证系统的可升级性和有序性,为STM32设计了基于FreeRTOS的轻量级操作系统。操作系统中设计五个线程,分别为网络连接,网络通信,信息分析,模拟信号指令处理和测频数据中转,其中网络连接的优先级高于其他线程。线程中间的信息传输使用消息队列的方式,具体线程和消息队列框图如图12。

图12 STM32操作系统设计图Figure 12 STM32 operating system design diagram

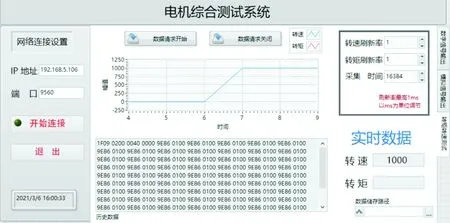

3.3 上位机软件设计

需要设计完整可操作的上位机,设计框图如图13。设计完成后的交互界面如图14。

图13 上位机软件设计图Figure 13 Host computer software design drawing

图14 上位机前面板示意图Figure 14 Schematic diagram of the front panel of the host computer

4 系统测试与分析

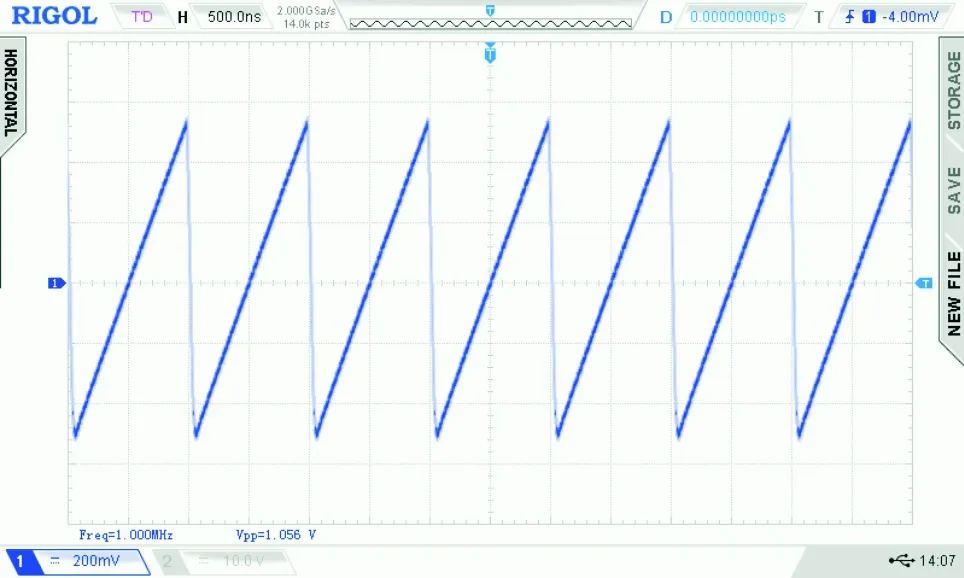

4.1 模拟量加载测试

通过上位机给系统输出1 MHz三种波形的指令,并通过示波器对输出波形进行记录。输出示意图如图15~17,可以看到该模块输出频率可达到1 MHz,且输出稳定。

图15 正弦波信号输出示波器图Figure 15 Sine wave output oscilloscope diagram

图16 方波输出示波器图Figure 16 Square wave output oscilloscope diagram

图17 三角波输出示波器图Figure 17 Triangle wave output oscilloscope diagram

动态模拟量的调制参数有频率、峰峰值、偏置,因此分别对这些参数进行误差测试。首先对频率误差进行测试,针对每种波形,从低频到高频,取40个测试点,按照低频间隔小,高频间隔大的规律进行取点,测试结果图如图18。

图18 输出频率相对误差Figure 18 Relative error of output frequency

由图18可知,正弦波在1 MHz时有最大误差0.7%,三角波在1 MHz时有最大误差2%,方波在700 kHz时有最大误差0.4%。正弦波和方波在范围内频率均满足设计要求,三角波在800 kHz内满足设计要求。

然后对输出峰峰值进行误差测试,对频率取对数,从1 Hz到1 MHz,共取6个点,针对每个频率点,再取10个峰峰值点,每个峰峰值间隔1 V,共10×6=60个测试点进行测试,测试结果如图19~21。

图19 正弦波输出峰峰值相对误差Figure 19 Sine wave output peak-to-peak relative error

图20 方波输出峰峰值相对误差Figure 20 Square wave output peak-to-peak relative error

图21 三角波输出峰峰值相对误差Figure 21 Triangle wave output peak-to-peak relative error

该系统输出正弦波在峰峰值为1 V,频率值为1 Hz时有峰峰值最大相对误差0.3%,方波在峰峰值为1 V,频率值为10 kHz时有最大峰峰值相对误差0.36%,而三角波在峰峰值为1 V,频率值分别为1 kHz和100 kHz时有最大相对误差0.2%。均满足设计要求。

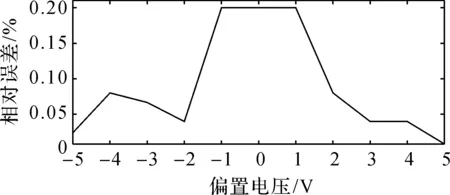

最后对偏置进行误差测试,只取直流偏置进行计算,在偏置范围内,从-5 V到+5 V,共取10个点进行测试。输出的相对误差如图22,即输出偏置最大相对误差不超过0.2%。

图22 偏置电压相对误差Figure 22 Relative error of bias voltage

4.2 频率计算精度测试

由信号发生器在输入端输入不同的标准频率信号,记录由系统输出数据后根据公式计算频率结果,误差精确到小数点后三位,结果如表1。由表1可知,在测试范围内,误差均在0.01%以下,满足测试要求,且频率越低,精度越高。

表1 频率测试结果

4.3 电机测试台架测试

为了对数据采集的实时性进行测试,同时进一步确认该系统可以应用于电机测试平台,因此在电机测试台架上进行进一步的测试,实物平台如图23。

图23 电机测试系统实物平台Figure 23 Motor test system physical bench

对被测电机取900 r/s为目标转速,参考电压为3 V。测功机不给转速和转矩信号。首先将测试系统接上电机测试平台,开始接收数据,然后输出直流偏置电压3 V,一段时间后停止数据接收。取其中一段离线数据进行绘图分析,如图24。

图24 电机测试平台阶跃响应Figure 24 Step response of motor test platform

图中2~2.5 s中间有50个数据点,根据国标要求,可以完整地绘制出电机转速阶跃响应的几个标准点。因此,该测试系统的数据接收可以实时地测试出电机的转速变化,提供可靠的电机测试环境。

5 结 论

本文设计了一个兼容性强,具有较大升级空间的综合测试系统。可以加载高精度的动态模拟信号,并且能够对数字信号进行采集测频。模拟信号采用DDS的方式进行合成,可对幅值、频率、偏置等参数进行范围内的调制,输出波形的相位连续性高,可提供更丰富的测试内容,模拟电机运行场景。测频使用测周法可满足低频段测频精度高且实时性高的要求。经过验证,该系统在测频范围内的输出相对误差小于等于0.01%,满足设计要求。