以双字线双阈值4T SRAM 为基础的存内计算设计

2021-11-17蔺智挺钮建超吴秀龙彭春雨

蔺智挺,钮建超,吴秀龙,彭春雨

安徽大学 电子信息工程学院,合肥230601

在大数据时代来临之际,冯·诺依曼体系中的存算分离架构带入的“存储墙”成为提高系统性能的最大障碍。学者们提出了一种存储与运算相结合的架构——存算一体即存储单元,不仅可以实现数据的存储与读取,而且存储数据无需输出到外围电路,在读取数据的同时即可完成运算。存算一体架构已广泛地应用到机器学习、人工智能等领域中[1-2]。存内计算架构的提出不仅极大提升了数据运算的效率,而且有效降低了存储系统的能耗,提高了存储系统的吞吐量[3]。但是由于芯片面积的限制,片上系统能够集成存储单元的数量受到严重限制。为了实现大容量、低成本的存储器设计[4],人们对传统静态随机存储器(static random access memory,SRAM)进行了优化,设计了一种由4管组成的单字线双阈值4T存储结构[5]。本文设计电路对传统单字线双阈值4T 存储单元进行了优化改进,提出了一种双字线双阈值4T 存储结构,相较于传统6T 存储单元的优势为:存储单元存储面积减少近25%[6],在大规模集成电路应用中双字线4T存储单元读功耗比单字线4T 存储结构减少了47%,同时由于双字线存储单元实现了字线分离,不仅可以单端实现一些基本逻辑运算,还能完成二元数据搜索(binary content addressable memory,BCAM)运算,极大地丰富了4T 存储结构的运算功能。

1 双字线双阈值4T SRAM 存储系统设计

1.1 双字线双阈值4T 存储单元

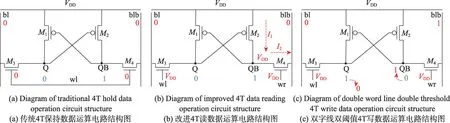

本文提出一种双字线双阈值4T SRAM 存储结构,如图1(b)所示,M1、M2为高阈值(high threshold value,HVT)上 拉PMOS 管,M3、M4为低阈值(low threshold value,LVT)传输NMOS 管[7]。bl、blb 为位线控制信号,wl、wr 为字线控制信号,Vdd为电源电压,Vwl、Vwr为字线电压。

1.2 存内计算系统结构

基于双字线双阈值4T 存储单元的存储系统由存储阵列与外围电路共同构成。如图1(a)所示,存储系统主要包括存储阵列、行译码电路、列译码电路、预充电路和由灵敏放大器(sense amplifier,SA)组成的输出电路[8]。其中存储阵列由双字线双阈值4T 存储单元构成。由图1(b)可知,sw(switch)为列译码电路产生的列选控制信号,高电平有效。位线bl、blb 电压由预充电路提供,字线控制信号wl、wr 由行译码电路生成。其中D 区域代表由两个上拉PMOS 管组成的负载模块。本文所提设计电路不仅可实现传统SRAM 的读、写、保持操作,还可以实现多种逻辑运算。因此存储系统包含两种运算模式:(1)SRAM 模式,主要执行数据的保持、存储与读取操作;(2)CIM模式,通过对多行存储单元进行“读”操作,无需将数据输出到外围电路即可实现BCAM 运算和与、或非、异或等逻辑运算。

2 系统模式介绍

2.1 SRAM 模式

SRAM 模式主要执行数据的保持、存储和读取操作。下面具体介绍各操作详细过程。

(1)数据保持操作

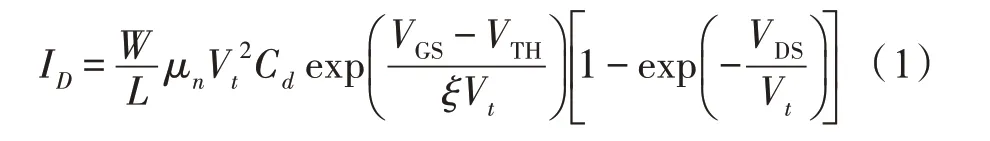

本文提出的双字线4T 结构比传统的6T 结构少两个NMOS驱动管,因此4T存储结构存储数据的稳定性弱于6T 存储结构,称4T 存储结构为亚稳态结构[9]。由图2(a)可知,上拉管M1、M2分别处于关断和导通状态,传输管M3、M4均处于关断状态。由于MOS 管存在亚阈值导电效应,当VGS小于阈值电压VTH时,一个“弱”的反型层仍然存在,并存在源漏电流ID且与VGS呈现指数关系,如式(1)所示:

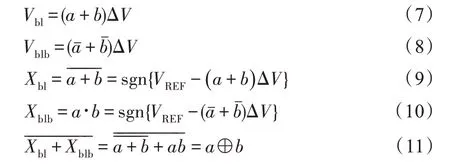

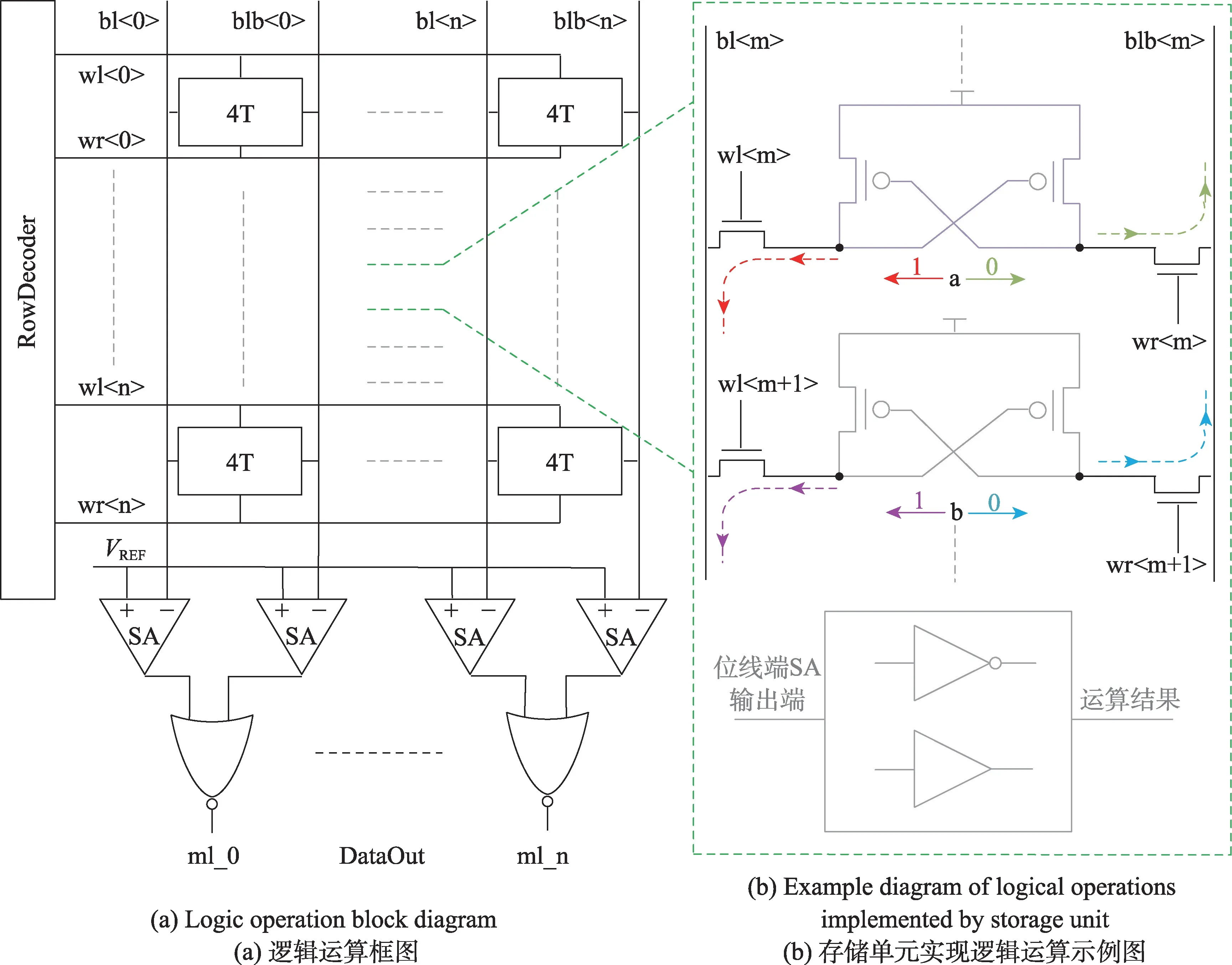

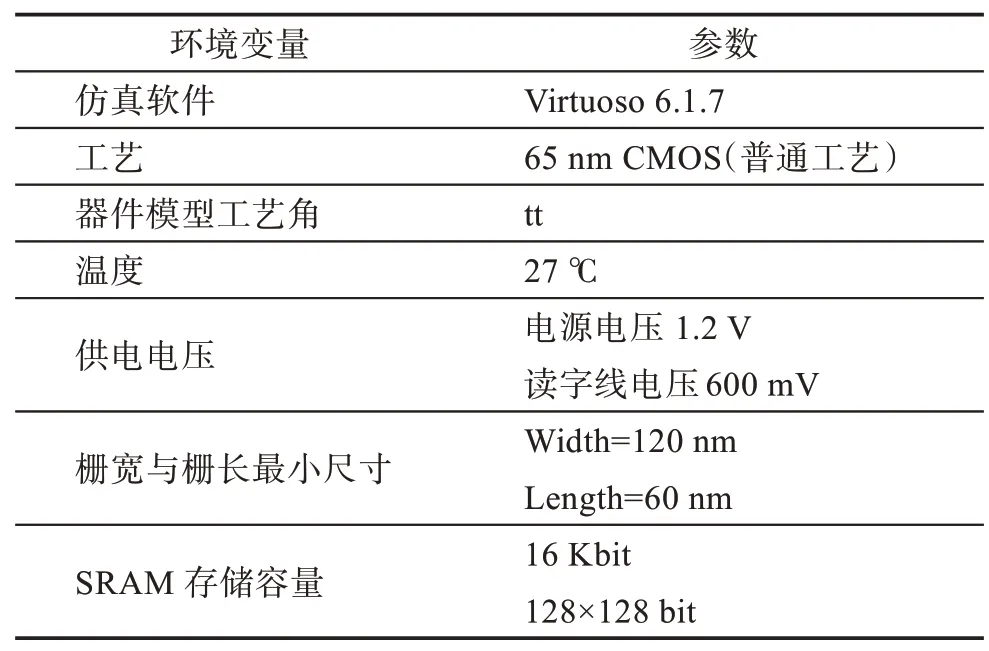

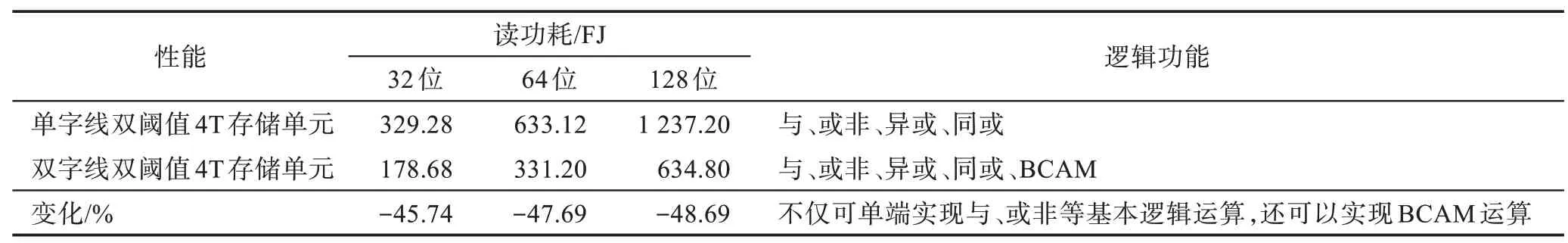

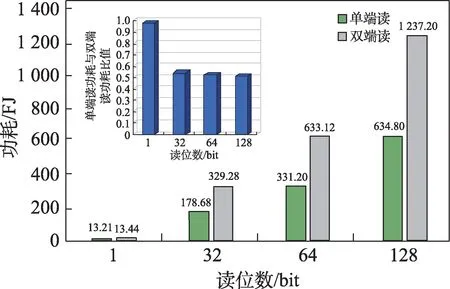

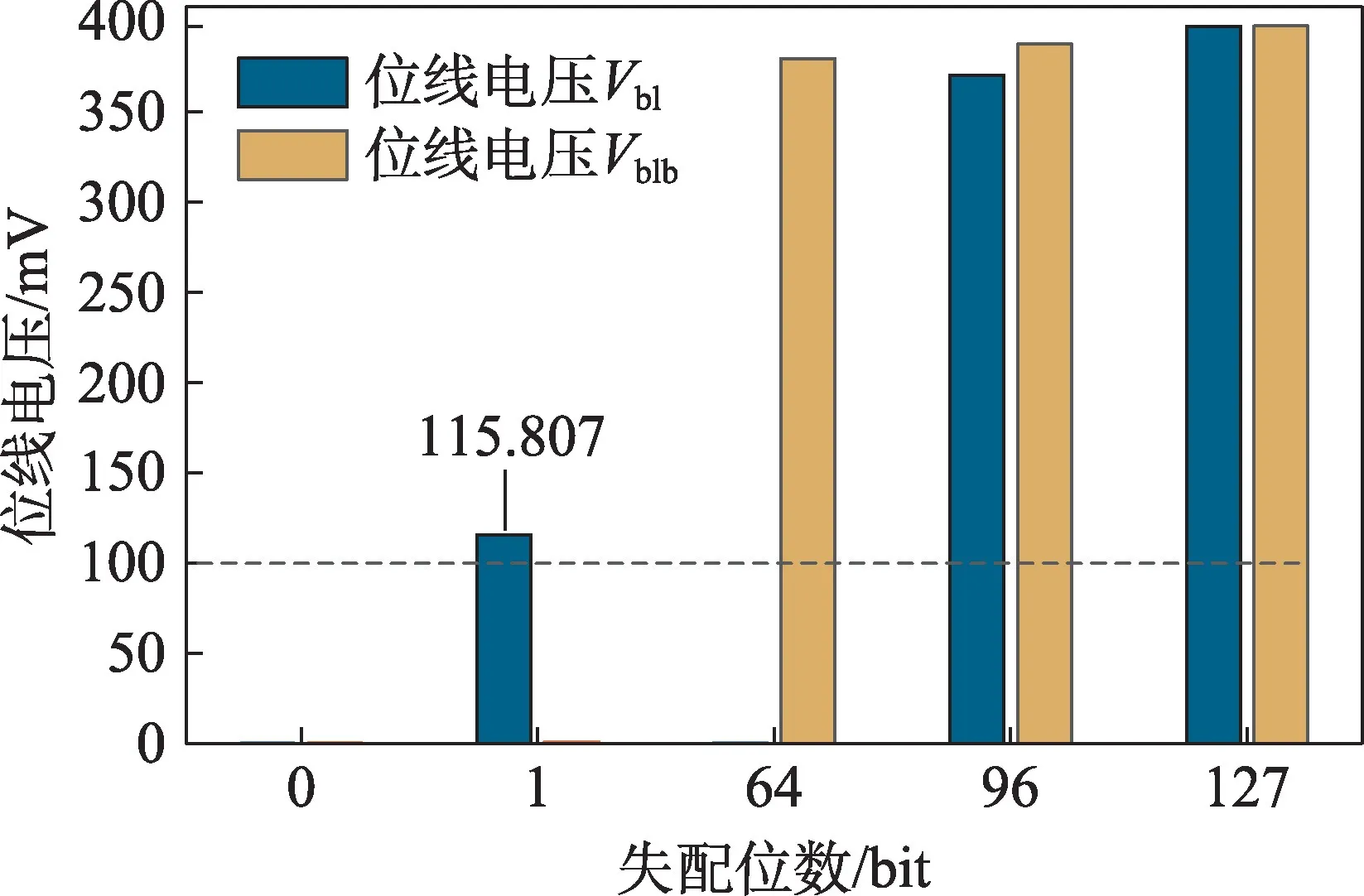

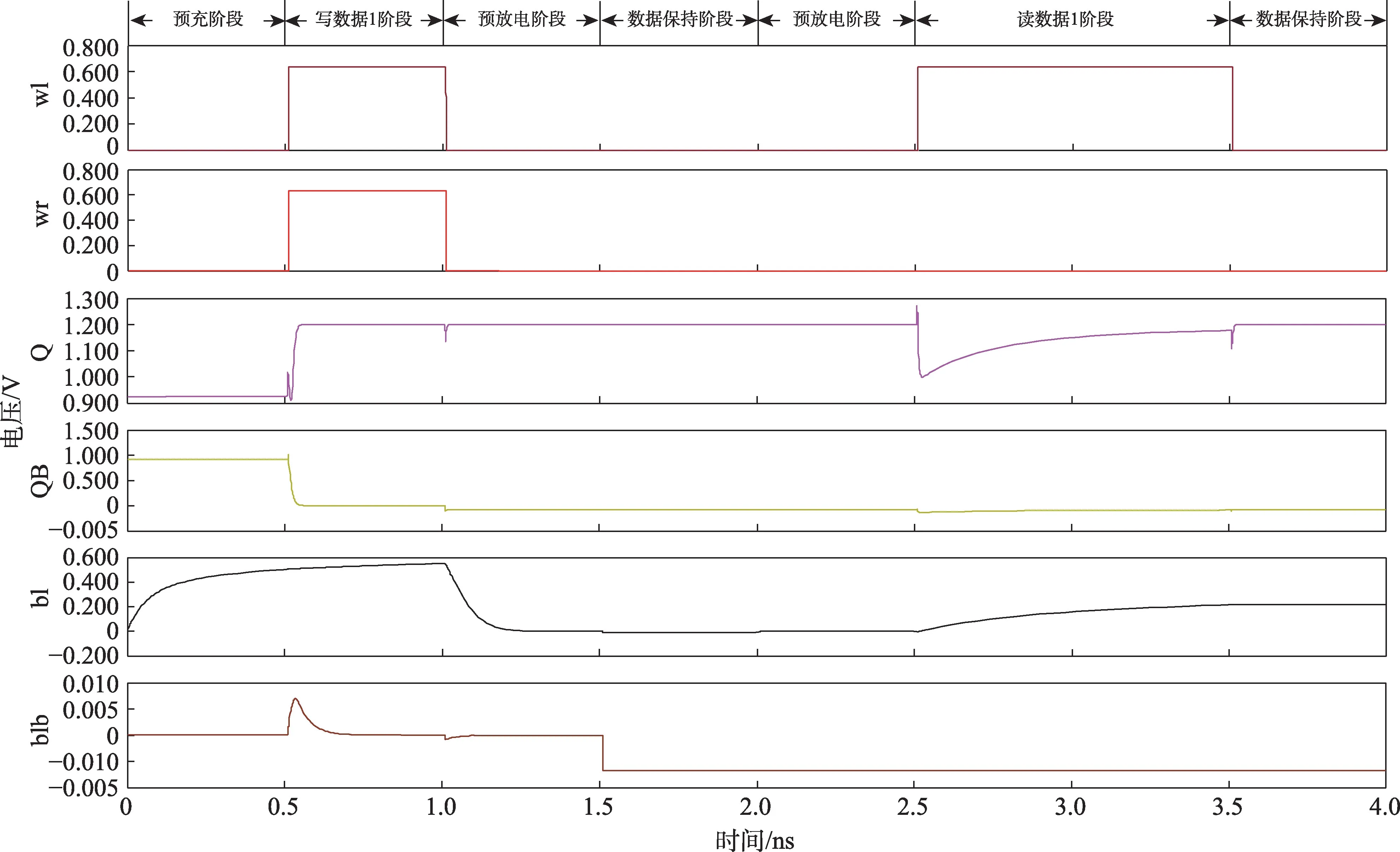

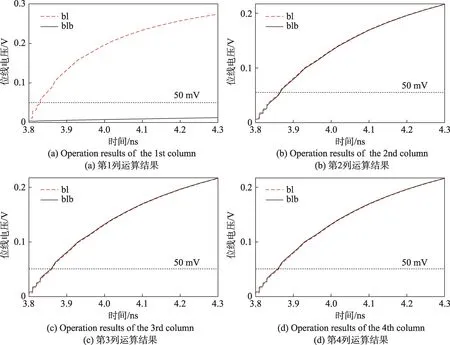

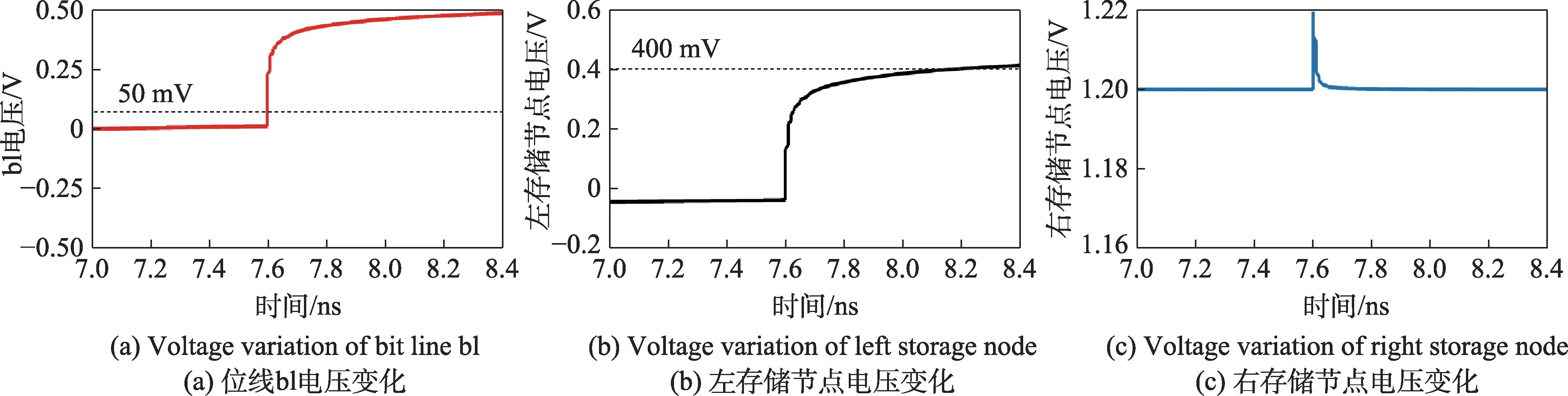

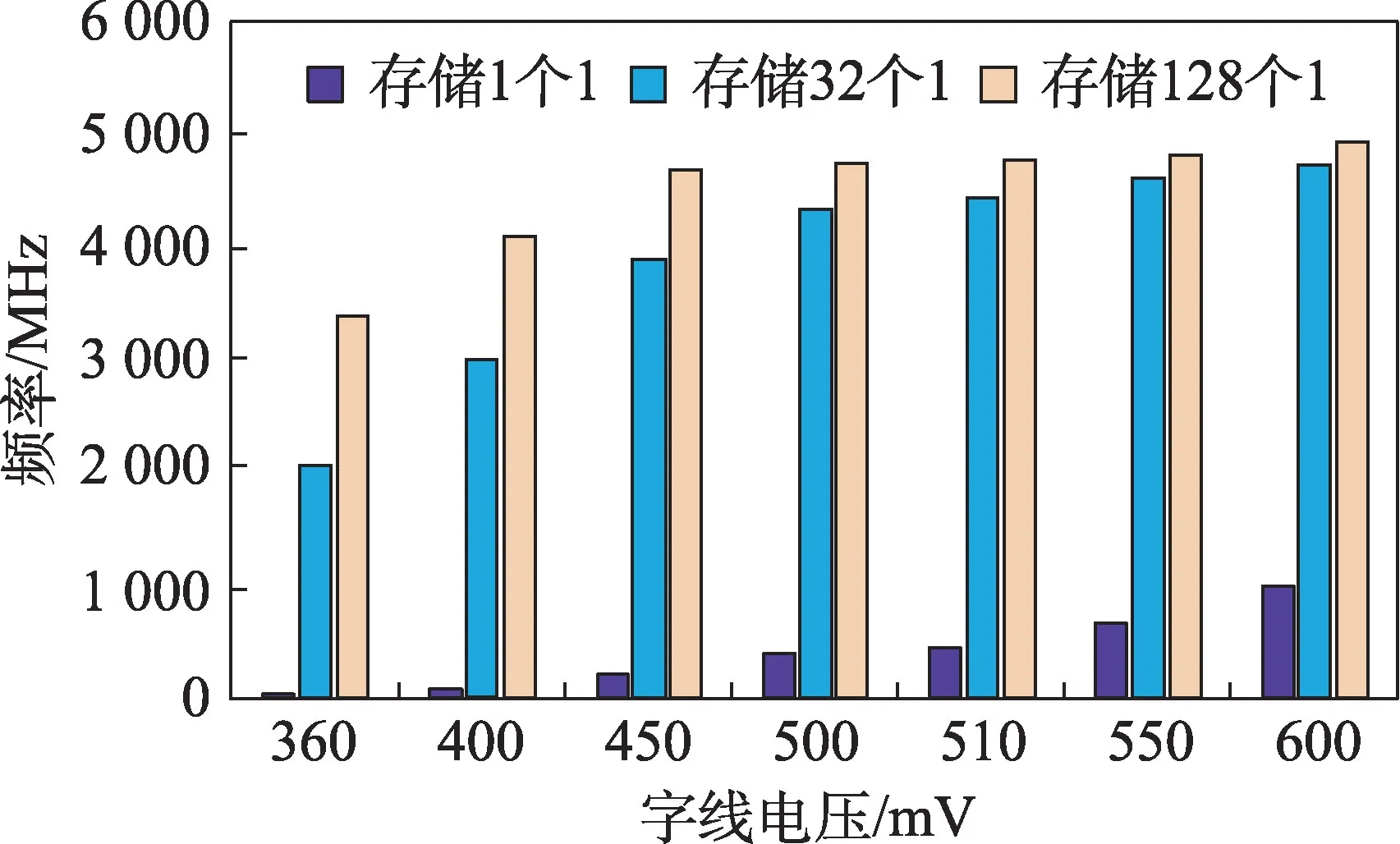

式中,ξ>1,是一个非理想因子,Vt=KT/q,此时MOS 管工作在弱反型区。虽然亚阈值电流只有纳安到微安量级,但在大规模集成电路应用中,即使所有器件都处于关断状态,由亚阈值电流构成的整个芯片的关态电流也相当大,可能达到数个安培,产生无用功耗[10],为了减小亚阈值电流的影响,需要对亚阈值电流随VGS的变化关系进行研究。亚阈值导电效应的前提条件是VGS (2)数据读取操作 由图2(b)可知,上拉管M2,传输管M4处于导通状态。上拉管M2的漏-源电压VDS1约为0,M2的过驱动电压VGS1-VTH1为-VDD-VTH1,满足式(2),即上拉管M2处于深三极管区。传输管M4的漏-源电压VDS2约为VDD,M4的过驱动电压VGS2-VTH2为VDD-VTH2,满足式(3),即传输管M4处于饱和区。因此导通电流I1、I2满足式(4)、式(5)。根据基尔霍夫电流定律可知,I1与I2的绝对值相等,由式(4)、式(5)可得到MOS 管M4的漏极电压VD如式(6)所示。 Fig.2 SRAM memory unit improved circuit structure diagram图2 SRAM 存储单元改进电路结构图 由于M2为高阈值,M4为低阈值,空穴的迁移率是电子的1/2 到1/4。即由式(6)可知,M4的漏极电压小于电源电压,存储节点稳定性降低。为了增强存储单元读数据稳定性,本文所提电路改进如下:①采用单端读模式,单端读取数据“0”时,位线blb 未预放电至低电平,M4的过驱动电压降低,漏极电压VD随之升高。②减小字线电压,字线电压降低导致M4的过驱动电压减小,使得MOS管M4的漏极电压VD升高。综上所述,双字线双阈值4T 存储结构在读数据时,字线wl、wr 置低电平,位线bl 预放电至低电平,字线wl 置高电平(字线电压低于电源电压),通过位线端灵敏放大器与参考电压VREF比较后输出存储数据,实现读数据操作。 (3)数据写操作 4T SRAM 存储结构相较于传统6T 存储结构减少了两个NMOS 下拉管,导致存储“0”节点易于翻转,故写入操作相较于6T SRAM 存储结构更容易实现。假设存储数据如图2(c)所示,存储数据为“1”,写入数据“1”时位线bl 为高电平与存储数据相同,存储数据不变,完成写“1”操作。写入数据为“0”时,位线bl、blb 分别为低电平和高电平,存储“1”节点通过传输管M3向位线bl 充电,存储节点Q 电压下降。位线blb 通过传输管M4向存储“0”节点充电,存储节点QB 电压升高。由于传输管为低阈值,上拉管为高阈值,故存储“1”节点电压下降速度大于存储“0”节点电压上升速度,当存储节点Q 电压下降到M2的开启电压时,M2导通。存储“0”节点与上拉电压连接变为存储“1”节点,存储“1”节点充电完成变为存储“0”节点,实现数据“0”的写入操作(存储数据相反时,过程类似)。 2.2.1 或非、与、异或等逻辑运算 存内计算(CIM)技术是提高计算机性能的关键技术之一。改进后的4T 结构具备存内计算功能,在追求大容量、多功能存储器设计的大时代背景下,具有重要的实用价值。如图3(a)为执行逻辑运算时的电路结构图,存储系统进行逻辑运算时调用的电路主要包括行译码电路、存储阵列、预充电路和输出电路(由灵敏放大器和门电路组成)且第n列输出结果为ml_n。位线bl、blb 预放电至低电平,输入信号通过行译码电路任意选择两行数据。如图3(b)所示,假设所选行储单元左存储节点存储数据分别为a和b。进行逻辑运算时,当存储数据存在“1”时,左存储节点向位线bl 充电,反之右存储节点向位线blb 充电。位线电压增量为ΔV[12],逻辑运算时,位线电压值如式(7)、式(8)所示。为了能够正确输出运算结果,需要通过理论分析与实验对比,选择一个合适的参考电压VREF(参考电压小于ΔV大于保持状态下位线电压值)。然后通过灵敏放大器输出逻辑运算在位线上的运算结果,如式(9)、式(10)所示[13]。由函数关系式可知,在位线bl 上实现数据的或非运算,位线blb上实现数据的与运算,对存储单元进行操作无需将数据输出到外围运算电路便可实现基本逻辑运算。由于存储单元是双字线存储结构,可通过单端操作的方式实现基本逻辑运算。通过译码电路选择要参与运算的存储单元,所选存储单元字线wl 置高电平,wr 置低电平,通过SA 检测位线bl 电压变化可输出或非运算结果。实现与运算过程和或非运算类似,字线wl、wr 与之设置相反。SA 输出端接反向器,可实现相反逻辑运算。字线wl、wr 均置高电平,将两位线端SA 输出结果通过或非门输出后即可获得所选数据的异或运算结果,如式(11)所示。 2.2.2 BCAM 运算 Fig.3 Logic operation circuit structure diagram图3 逻辑运算电路结构图 为了更高效地使用有限的存储容量,学者们提出了一种内容可寻址存储技术(content addressable memory,CAM),该技术可以对存储数据进行匹配筛选,从而提升了存储效率[14]。本文通过对单字线4T 结构进行改进,使其具有BCAM 运算功能。输入一个数据信号通过译码电路后,转换为两个相反的电平信号,分别控制存储单元两个传输管的开断,然后通过灵敏放大器输出运算结果,即可实现BCAM 运算[15]。存储系统在执行BCAM 运算时调用的电路包括行译码电路、预充电路、存储阵列和输出电路。图4 为4×4存储阵列执行BCAM 运算示意图。BCAM 运算时,位线bl、blb 预放电至低电平,输入数据通过译码电路实现对相应传输管的开断控制,通过灵敏放大器输出运算结果。输出结果为“1”时代表匹配,反之不匹配。输入数据为“1”时,字线wr、wl 分别为高电平和低电平,输入数据为“0”时相反设置。输入数据与存储数据不同时,存储节点向位线充电,否则不向位线充电。位线电压大于参考电压VREF时,灵敏放大器输出结果为“1”,否则输出结果为“0”。两位线端灵敏放大器的输出结果通过或非门输出后即可得到BCAM运算结果。由图4 可知,输入数据与前3 列存储数据不同,均存在存储单元的存储节点向位线充电,通过输出电路得到输出结果均为“0”。输入数据与第4 列存储数据相同,不存在存储节点向位线充电,两位线电压均小于参考电压,通过输出电路得到输出结果为“1”即实现数据匹配。 对存储单元的各性能进行分析,是衡量存储结构优劣的重要步骤之一。它不仅有利于直观展现存储结构的优缺点,更有利于设计者进行改进与优化。由于在不同仿真环境下所得到的数据可能不同,需要对具体仿真环境进行设置,本文所提电路的具体仿真环境如表1 所示。 设计存储单元时需要在单元面积和功耗等性能之间进行综合考虑,折中取舍。本文在表1 仿真环境下分别对双字线双阈值4T 存储单元与传统6T 存储单元和单字线双阈值4T 存储单元各性能进行仿真分析,实验结果如表2 所示。 Table 1 Simulation environment表1 仿真环境 为了保证实验数据的可靠性,下面具体介绍各性能仿真、性能分析的详细过程。 3.1.1 存储单元面积分析 在追求大容量、低成本存储器设计的大背景下,存储单元的存储面积成为存储器设计时要考虑的重要因素之一。本文所设计的双字线双阈值4T SRAM存储单元相较于传统6T SRAM 存储单元最大的特征为减少了两个驱动NMOS 管,实现了存储面积的大幅度减小。图5 给出了6T SRAM 存储单元与4T SRAM 存储单元的版图对比图。由图5 可知6T 与4T存储单元版图面积分别为(Pmetal表示版图单元尺寸单位),即4T 存储单元存储面积相较于6T 存储单元减少了25%。 3.1.2 读数据功耗分析 本文提出的双字线双阈值4T SRAM 存储结构采用单端读模式相较于传统单字线双阈值4T 结构的双端读模式,不仅可以增强读数据时存储节点的稳定性,而且在大规模集成电路应用中还可以大幅度减小读功耗。如图6 为双字线双阈值4T 存储单元与单字线双阈值4T 存储单读功耗对比图。横坐标为读取数据的位数,纵坐标为读数据时产生的功耗,其单位为FJ。读取数据位数为32 位和32 位以上时双字线结构比传统单字线结构读功耗可减少47%左右。其中蓝色柱状图为单端读功耗与双端读功耗比值示意图,读取一位数据时单端读功耗与双端读功耗比值接近1,读取数据位数为32 位和32 位以上时双端读功耗与单端读功耗比值约为0.53。 Table 2 Performance comparison of single/double word line and double threshold 4T storage unit表2 单/双字线双阈值4T 存储单元性能对比 Fig.5 Map comparison of storage units图5 存储单元版图对比 Fig.6 4T single-and double-end read power图6 4T 单/双端读功耗 对以双字线双阈值4T 存储单元为基础的存储阵列进行功能仿真,有利于更加全面地展示双字线4T存储结构的特性与运算能力。下面详细介绍以双字线4T 存储结构为基础进行功能仿真的具体过程。 3.2.1 参考电压的分析与选择 正确读取由双字线双阈值4T 存储单元构成的存储系统所存储的数据是其SRAM 模式和CIM 模式得以实现的关键,因此对参考电压的选择尤为重要。在CIM 模式下做BCAM 运算时,位线电压的变化最为多样,因此通过分析大阵列BCAM 运算时不同匹配情况下位线电压的变化情况,找到其最小电压,即可确定参考电压大小。本文在以双字线双阈值4T 存储单元为基础构成的大小为128×128 bit 的存储阵列下,仿真时长1 ns 时,测试不同失配情况下位线bl、blb 的电压变化情况。实验结果如图7 所示,其中1 位失配时,存储阵列存储1 个“1”和127 个“0”且失配对象为“1”。此时与存储数据“1”不匹配,存储节点向位线bl 充电。127 个“0”全匹配,存在位线bl 向左存储节点充电的情况,此时位线bl 的电压值是CIM 模式和SRAM 模式下位线电压变化最小值。为了能够正确读出升高的位线电压并确保电压不变的位线端SA 不会输出错误的结果,因此参考电压要小于位线变化最小电压且大于全匹配时位线电压,即参考电压要小于115.807 2 mV 且大于0.412 96 mV。SA 正确输出的前提条件是输入端电压具有一定的电压差且电压差越大越有利于正确读出数据。在综合考虑上述条件的同时为了确保输出的准确性,本文参考电压VREF大小设置为1/2×ΔVmin,即为50 mV。 Fig.7 Voltage values of bit line with different mismatch digits图7 不同失配位数下位线电压值 3.2.2 数据的保持、读、写操作 由前文论述可知,保证双字线双阈值4T 存储单元的存储数据在各运算模式下不发生翻转是整个设计的核心问题之一。字线电压是影响存储数据稳定性的重要因素,在不同字线电压下,对存储节点的稳定性进行研究并找出合适的字线电压是本文设计得以完成的关键步骤之一。在单端读模式下,本文重点研究存储数据为“1”时,存储节点随字线电压变化时的稳定情况。随着字线电压的变化,读数据时位线电压的上升速度也会受到影响。因此不仅要保证存储数据的稳定性,还要保证存储数据能够被正确读出。如图8 所示,存储“1”节点跳变时最低点电压随着字线电压的升高而减小,变化幅度则相反。字线电压为868 mV 时存储节点发生翻转,字线电压为821 mV 时位线电压达到最大值,分别为360.129 mV和279.395 mV。综上所述,要保证存储节点稳定且存储数据可被正确读出,字线电压不能大于868 mV,控制在600 mV 到821 mV 范围内为最优,字线电压为高电压/低电压时,控制读取时间为500 ps/1 ns 为最佳。 Fig.8 Voltage variation diagram of storage node/bit line图8 存储节点/位线电压变化图 如前文所述,字线电压越低越有利于保证存储数据的稳定。故本文所提设计电路在字线电压为600 mV,读数据时长为1 ns 的前提下进行时序仿真。图9 给出了以双字线双阈值4T 存储单元为基础构成的存储系统在SRAM 运算模式下的时序仿真图。由仿真图可知,读数据时存储节点会发生小幅度跳变,但不影响存储节点稳定。位线电压持续升高,在读数据时长为1 ns 时位线电压远超过50 mV,可被灵敏放大器正确读出。存储结构不足之处为读“1”时存储节点仍有一定幅度的跳变,对字线电压变化敏感。位线电压上升幅度有限,位线电压变化的线性度不理想等限制了该结构在汉明距离计算等运算方面的应用。 Fig.9 Timing simulation图9 时序仿真 3.2.3 异或、与、或非逻辑运算 在对双字线双阈值4T 存储单元的稳定性进行研究并解决相关问题后,以存储数据为“1011”“1100”时双字线4T 存储系统执行逻辑运算为例。图10 给出4列位线电压变化波形图,虚线与实线分别代表位线bl、blb 的电压变化,参考电压为50 mV。位线电压小于50 mV 时灵敏放大器输出“1”,反之输出为“0”。由图10 可知,执行异或运算时,第1 列位线端灵敏放大器输出结果经或非门输出后得到运算结果为“0”,第2~4 列变化趋势一致,输出结果均为“1”,即两个4位二进制数异或运算结果为0111。执行与、或非运算时,4 列位线bl 端灵敏放大器输出或非运算结果为0000,blb 端灵敏放大器输出与运算结果为1000。 3.2.4 BCAM 运算 BCAM 运算时位线电压的升高势必会影响存储节点的稳定。在大规模集成电路应用中,多行电路同时操作对存储节点的稳定性造成很大的影响,尤其是存储“0”节点。因此设计大阵列BCAM 运算,研究多行存储数据向位线充电且仅有一个存储“0”节点匹配时,存储“0”节点的稳定情况,是检验以双字线双阈值4T SRAM 存储单元为基础构成的存储阵列能否实现BCAM 运算的必要步骤之一[16]。本文以大小为128×128 bit 的双字线4T 存储阵列实现BCAM运算为例进行分析。预设存储数据为“111……10”(127 个1),输入数据全为“0”(128 个0)。图11 给出BCAM 运算完成后,位线bl 电压约为400 mV。存储数据为“0”的左存储节点电压升高到0.4 V 左右,但远远低于1.2 V。右存储节点电压基本稳定在1.2 V,存储节点未发生翻转。因此本文提出的电路结构在大规模集成电路设计中可实现多种情况下的BCAM 运算。 Fig.10 Waveform diagram of logic operation simulation图10 逻辑运算仿真波形图 Fig.11 Timing diagram of BCAM simulation图11 BCAM 仿真时序图 BCAM 运算功能是双字线双阈值4T SRAM 存储单元具备的一个重要运算功能,在解决BCAM 运算可行性问题后对其运算能耗和运算频率进行分析也十分重要。图12 给出BCAM 运算时,随着失配个数的增加不同匹配情况下的功耗变化图。输入数据“1”时能耗最大为909.72 FJ,输入“0”时能耗最小为432.12 FJ。电路的运算频率和位线电压的大小密切相关,图13 给出在不同字线电压下,存储阵列存储不同数据时,BCAM 运算频率变化图。由图可知字线电压为600 mV 时,频率为1 010.1 MHz,即运算速度为16 161.6×NMB/Hz。 Fig.12 Mismatch energy consumption图12 失配功耗 Fig.13 BCAM operation frequency图13 BCAM 运算频率 本文提出了一种基于双字线双阈值4T 存储单元的存储系统。基于双字线双阈值4T SRAM 的存内计算架构与基于6T SRAM 的存内计算架构均可实现异或、与、或非、BCAM 等运算,但其存储面积比基于6T存储单元的存内结构的存储面积降低了25%,采用双字线4T 存储结构较单字线4T 存储结构在大规模集成电路应用中读数据操作时功耗降低了47%左右。当字线电压为600 mV 时运算速度可达到16 161.6 ×NMB/Hz,具有很好的工程应用价值。

2.2 CIM 运算模式

3 性能分析与功能仿真

3.1 存储单元性能分析

3.2 功能仿真

4 总结