基于MEMS工艺的电学TEM芯片研发与应用

2021-11-16金传洪

孙 扬,金传洪

(浙江大学 材料科学与工程学院,硅材料国家重点实验室,浙江 杭州 310027)

1 前 言

透射电子显微镜(TEM)自诞生[1]以来,就一直是材料微尺度表征的重要工具。近年来,得益于球差矫正器、单色化光源和超快成像等技术的引入,TEM在空间、能量和时间分辨率上都有了进一步拓展和优化,空间分辨率已达亚埃尺度。同时,通过特制样品杆可在电子显微镜内引入力场[2-3]、电场[4-5]、热场[6-7]和磁场[8]等外场作用,结合TEM芯片,可实现对样品的实时、动态观察和表征,在化学、物理、生物和微纳电子等领域有更广泛应用[9]。

TEM电学测试通过原位电学样品杆在电镜内引入外加电场,以观察材料结构在不同电场激励下的实时响应行为,被广泛用于电迁移[10-13]、 场发射[14-16]、电化学[17-18]及电子束(EB)辐照的影响[19-21]等过程的研究,相关结论在材料的微观结构研究以及性能提升方面起到了重要作用。

实现原位TEM电学测量主要有两种方案。方案一是结合扫描探针显微技术(SPM)与透射电子显微镜(TEM)[14,22-24],即采用嵌有微型SPM针尖的样品杆,其一端为压电陶瓷驱动的SPM移动电极,另一端为固定电极。可移动的SPM针尖有利于对样品的不同区域施加电激励,但针尖与待测样品的接触不易控制,接触电阻常常较大。方案二是使用具有完整电学回路的电学芯片[25-27],通过一定的转移方法将待测样品转移到电学芯片上,然后与对应的电学样品杆连接,即可载入透射电镜进行原位观察,操作简单且稳定性高,但是商用的电学芯片价格昂贵,其电学回路设计也较为有限。

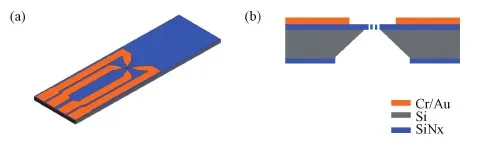

本研究通过MEMS工艺自行设计并研制出用于原位电镜实验的四电极电学芯片,如图1所示。结合透射电镜电学样品杆和高精度数字源表,并以CVD生长的单层MoS2材料为参照体系,测量I-V电学特性曲线。

图1 四电极电学芯片 (a) 芯片单元; (b) 横截面图

2.1 窗口材料的选择

为了实现样品在不同电学激励信号下的动态行为表征,电学芯片需设计合适的观察窗口,窗口材料需要满足两个条件:一是应力要求,窗口材料要有足够高的机械强度,给样品提供有力支撑;二是可视要求,窗口材料对入射电子束透明。常用的窗口材料有非晶氮化硅薄膜(Si3N4)[28]和非晶碳薄膜(Carbon film)[29]等,膜层很薄,窗口尺寸也较小,最近也有用原子层厚的石墨烯(Graphene sheet)作为窗口层的相关报道[30]。其中,Si3N4薄膜具有高电阻率,高机械强度,化学性质稳定,对硅的各向异性湿法腐蚀具有较好的自停止效应,并兼容各种材料的制备环境等优点,是最常用的窗口层材料。

氮化硅的成膜工艺主要有低压化学气相沉积法(LPCVD)和等离子体增强化学气相沉积(PECVD),LPCVD通过降低压强使气体的传输速率减慢,反应时间增加,从而得到高纯度、高致密度的薄膜,膜内残余应力较小[31]。为得到高质量的窗口层材料,本研究采用LPCVD工艺生长的非化学计量比SiNx薄膜作为窗口层材料。氮化硅的膜层厚度为50 nm,残余应力低于250 MPa。此外,在成像过程中将部分TEM样品悬空可有效减少SiNx薄膜对成像分辨率的影响,故对SiNx窗口进行开孔处理。

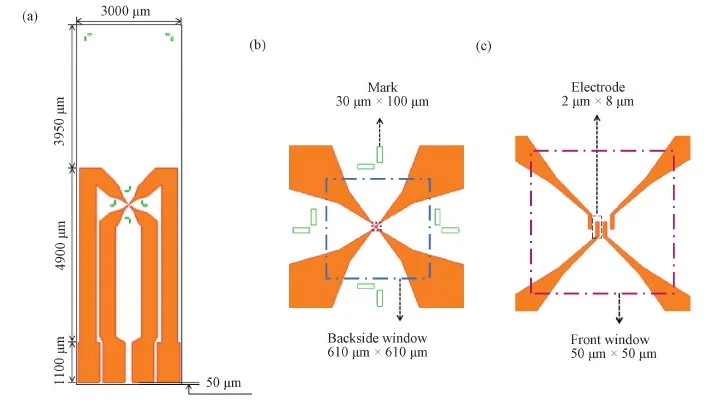

2.2 电极图案掩模版设计

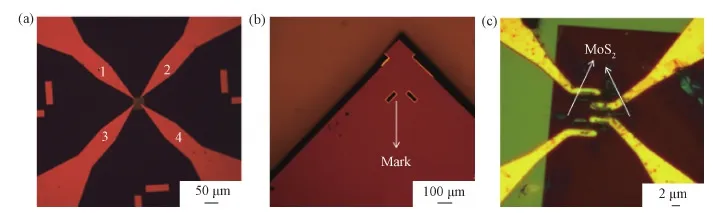

电极图案掩膜版的基本单元如图2a所示,图中橙色区域为四个电极,图2b和2c分别是芯片的中心和氮化硅窗口的区域放大图。考虑到电学芯片与单倾样品杆的兼容性,将芯片整体单元尺寸定为10000 μm(长)×3000 μm(宽)×400 μm(厚)。另考虑到样品的尺寸和工艺精度等因素,氮化硅窗口大小设计为50 μm(长)×50 μm(宽)×50 nm(厚),样品放置区域的电极尺寸为2 μm(宽)×8 μm(长)×185 nm(厚)。套刻标记为30 μm(长)×100 μm(宽)的数对重复单元。SiNx窗口上的开孔由双聚焦离子束微纳加工仪加工,其大小和尺寸由实验参数决定,与版图无关。

图2 电极图案掩膜版设计 (a) 基本单元; (b) 芯片中心区域放大图; (c) 窗口区域放大图

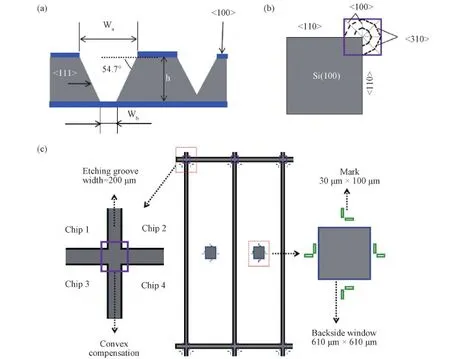

2.3 SiNx窗口掩膜版设计

芯片的三维结构主要通过KOH溶液对Si的各向异性湿法腐蚀来完成。已知质量分数为33%,温度为80 ℃的KOH溶液对Si (100)晶面的刻蚀速率约为1 μm/min[32],而对(111)晶面的刻蚀速率几乎为0,两个晶面的夹角为54.74°,几何构型如图3a所示。假设芯片背面窗口的宽度为Wa,正面窗口的宽度为Wb,硅片厚度为h,可推得Wb≈Wa-2hcot54.7°。基于此,为保证正面窗口尺寸Wb为50 μm,掩模版背面窗口的尺寸Wa设计为610 μm。

湿法腐蚀对凸角的切削效应会使最终形成的芯片外观与目标图形失配,影响芯片的性能和良率。为完整保留芯片单元的方形凸角,需根据晶面上各个晶向的腐蚀速率,预先设置好一定的补偿图形。采用图3(b)所示的方形补偿方案[33],在湿法腐蚀过程中补偿块和凸角都沿<310>晶向切削,当腐蚀进行到凸角顶点时,留下完整的凸角结构。为简化划片流程,引入200 μm宽的刻蚀槽,根据图3(a)所示的几何模型,该刻蚀槽最终会被腐蚀成V型槽,分离芯片时只需在V型槽的顶点处稍微施加作用力。最终得到如图3(c)所示的SiNx窗口掩膜版设计图形,图中灰色部分为SiNx刻蚀区域。此外,因为使用的对a准标记是非中心对称图形,为满足背面套刻的要求,对准标记需要做镜像处理。

图3 SiNx窗口掩模版设计

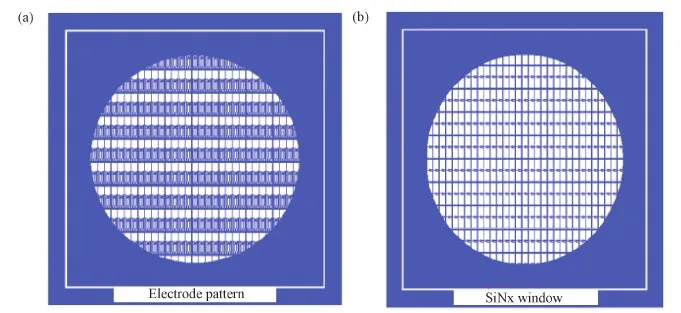

2.4 芯片制备流程

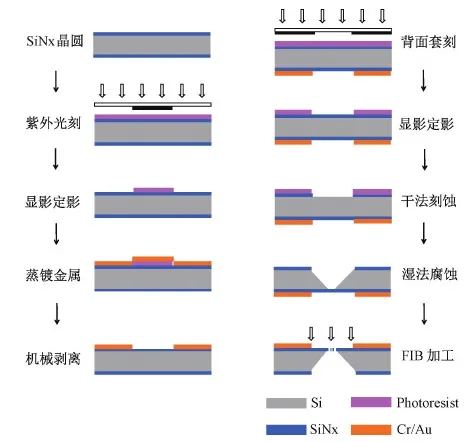

原位电学芯片的制备需要用到如图4(a)和4(b)所示的5寸掩膜版,图4(a)为金属电极掩膜版,用于图形化电极图案,图4(b)为刻蚀掩膜版,用于刻蚀芯片的背面窗口,由中科院微电子所代加工。芯片制备工艺流程如图5所示:①通过LPCVD工艺在4寸的双面抛光 (100) Si晶圆上下两侧各生长一层50 nm厚的SiNx薄膜;②紫外光刻,将图4(a)掩膜版上的图形转移到SiNx晶圆上;③微波等离子体去残胶,电子束蒸发镀膜仪蒸镀黏附层Cr (5 nm) 和电极层Au (180 nm);④丙酮超声剥离金属,得到电极层;⑤清洗硅片,进行背面套刻,转移图4(b)掩膜版上的图形到硅片的背面;⑥利用反应离子刻蚀法刻蚀未被光胶保护的SiNx薄膜,露出背面窗口,窗口尺寸为610 μm×610 μm;⑦用质量分数为33%,温度为80 ℃的KOH溶液腐蚀硅,释放结构得到50 μm× 50 μm正面窗口;⑧划片后用聚焦离子束在SiNx窗口区域开孔,孔的大小和形状可视样品形貌自行调整,本研究中矩形孔的尺寸为2.5 μm(长)×0.7 μm(宽),共5个孔。

图4 光刻掩膜版 (a) 金属电极掩膜版; (b) 刻蚀掩膜版

图5 电学芯片制备工艺流程

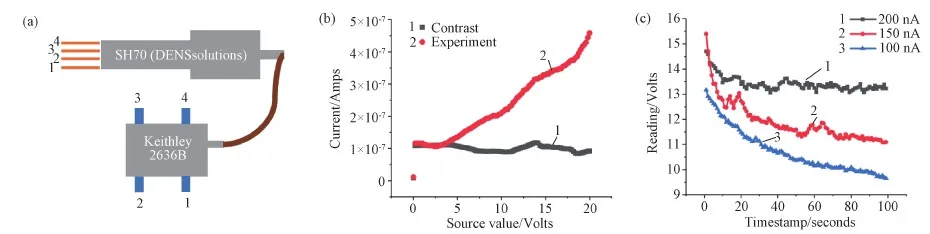

设计的掩膜版共有188个完整的芯片单元,流片成功105片,良品率约55.8%。图6是自制电学芯片的光镜图,测得芯片正面窗口大小为50.0 μm×49.5 μm,电极宽度2.1 μm,误差小于5%,主要来源于工艺和测量误差。图6(b)是划片后芯片的凸角情况,可看出其方形凸角得到了很好保护。选取CVD生长的MoS2样品作为对象,测试芯片。图6(c)是转移了MoS2样品之后的芯片表面,将该芯片的4个电极分别记为1,2,3,4,其中1~2和3~4分别构成电学回路,然后将其载入样品杆,连接到高精度数字源表上,对1~2两个电极进行退火处理,测量I-V特性曲线,如图7所示。发现退火处理后的MoS2导电性更好。采用不同大小的恒流源对电极进行退火处理,发现电流源为100 nA时接触电阻随着时间的增加而出现明显减小,从130 MΩ 降到了65 MΩ,当电流源增大到200 nA时接触电阻随时间的变化就很小。

图6 芯片表面光镜图

图7 MoS2电学性能测量 (a) 实验装置图; (b) MoS2退火前后I-V曲线; (c) 不同退火条件下MoS2的I-V曲线

4 结 论

本研究以4寸双面抛光(100)硅晶圆为衬底,氮化硅薄膜为窗口层材料,金属铬/金为电极材料,制备了一批TEM电学芯片,图形补偿和刻蚀槽的引入不仅保护了凸角,还简化了划片流程。对制备的电学芯片成功测试了其不同条件下制备的单层二硫化钼(MoS2)材料的电学特性曲线,说明该芯片设计满足电学测量的要求。若更改掩膜版的电极图案,还可以在芯片上集成加热电阻,制备具有加热功能的电学芯片,以实现不同温度调节下材料电学性能与微观结构间动态响应行为的实时观测。

(校对:周邦昌)