质子辐照下4T CMOS图像传感器满阱容量退化模拟研究

2021-11-10王祖军尚爱国霍勇刚薛院院贾同轩焦仟丽

杨 勰, 王祖军, 尚爱国, 霍勇刚, 薛院院, 贾同轩, 焦仟丽

(1. 西安高科技研究所, 西安 710025; 2. 强脉冲辐射环境模拟与效应国家重点实验室, 西安 710024; 3. 湘潭大学 材料科学与工程学院, 湘潭 411105)

目前,主流的可见光固态图像传感器有电荷耦合器件(charge couple device,CCD)和互补金属氧化物半导体(complementary metal oxide semiconductor, CMOS)图像传感器2种。与CCD相比,CMOS图像传感器具有功耗低、集成度高和价格低等优点[1-5]。近些年随着背照式和堆栈式等新型CMOS图像传感器技术的进步,CMOS图像传感器将成为星敏感器、太阳敏感器和空间遥感等光学成像系统中不可替代的核心器件[1-6]。然而在未来星际空间的探索中,器件面临恶劣的辐射环境,可能会造成器件短暂性或永久性辐照损伤,甚至使CMOS图像传感器功能失效,这将严重影响到航天器的成像性能[1-2]。

国内外均开展了CMOS图像传感器质子辐照损伤相关研究,但主要以实验研究为主,仿真模拟研究开展较少,且大部分研究集中在暗电流、图像噪声、暗电流非均匀性、饱和输出和转化增益等参数随质子辐照注量变化规律方面[5-9],对图像传感器满阱容量性能退化及抗辐射设计研究较少。满阱容量是指能够存储在PPD内的最大电荷量,满阱容量下降会导致图像传感器的动态范围、信噪比及灵敏度等性能退化[10]。然而,已开展的辐照实验并未揭示质子辐照导致图像传感器满阱容量下降机理。与实验相比,理论模拟可直观揭示质子辐照下满阱容量与像素内部结构及工艺参数的关联,在CMOS图像传感器辐射损伤评估及抗辐射加固技术方面具有独特的优势。

为揭示质子辐照导致CMOS图像传感器满阱容量退化规律,深入分析图像传感器质子辐照损伤机理,本文以4T CMOS图像传感器为研究对象,开展了不同注量质子辐照导致满阱容量退化模拟研究,分析了辐照导致满阱容量退化机理,并结合像素内部结构提出了抗质子辐照设计方案。

1 理论模拟

1.1 器件模型构建

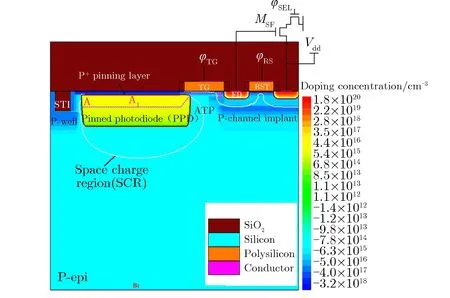

4T CMOS图像传感器像素单元的器件模型由浅沟槽隔离区(shallow trench isolation,STI)、P+型重掺杂注入层、N型注入层、传输栅(transfer gate,TG)、传输栅阈值调节注入层、防穿通注入层(anti-punch-through,APT)、浮置节点(floating diffusion,FD)、复位管RTS、复位管阈值调节注入层、P阱注入层、电源电压VDD和硅基底等区域构成。4T CMOS图像传感器像素单元掺杂分布如图1所示。

图1 4T CMOS图像传感器像素单元掺杂分布图Fig.1 Doped pattern of 4T CMOS image sensor pixel element

1.2 物理模型构建

在电场和电势的驱使下使得电子和空穴发生漂移-扩散运动,导致器件内部原本平衡状态发生改变,进而影响器件相关性能参数。器件内部电子-空穴输运可由基于Poisson方程和载流子连续性方程的输运方程描述:

(1)

(2)

(3)

其中,φ为电势;εr,ε0分别为相对介电常数和真空介电常数;np,ne分别为空穴与电子密度;e为电子所带的电荷量;NA,ND分别为受主和施主掺杂浓度;Je,Jp分别为电子和空穴的电流密度;Ge,Gp分别为总剂量引起的电子和空穴的产生率;Ue,Up分别为电子和空穴的复合率。

质子辐照会产生电离和位移损伤,电离损伤主要在SiO2和STI浅沟槽隔离区中产生氧化物陷阱电荷,在Si-SiO2界面处产生界面态,位移损伤主要在体硅中产生体缺陷[13]。在仿真中电离损伤是利用总剂量辐射模型来等效质子辐射在辐射敏感区产生电子-空穴对,该模型中电子-空穴对的产生率可表示为[14-15]

(4)

(5)

位移损伤是利用缺陷模型来模拟质子辐照在器件中产生的体缺陷,表1列出了能量为10 MeV,注量为5×109cm-2质子辐照时,产生缺陷的种类、能级和密度。模型中缺陷类型、能级位置和缺陷浓度,通过改变缺陷的电荷状态、浓度及载流子俘获截面,利用Shockley-Read-Hall(SRH)复合模型来表示缺陷对载流子复合的影响, SRH复合模型可表示为

(6)

其中,ni为本征载流子浓度;τe,τp为电子和空穴的平均寿命。

表1 能量为10 MeV,注量为5×109 cm-2的质子辐照时,产生的缺陷类型、能级和密度[16]Tab.1 Defect parameters after 10 MeV protonirradiation with the fluence of 5×109 cm-2

2 结果讨论与分析

像素的满阱容量(full well capacity,FWC)是指耗尽层在积分时间足够长时收集到的最大光生电子数。满阱容量主要受光电二极管(PPD)电容、TG沟道势垒及浮置节点(FD)与衬底形成的耗尽层的影响。

2.1 PPD电容退化分析

通过分析不同注量质子辐照对PPD电容以及耗尽层N区电势的影响,可揭示辐照导致满阱容量退化机理。满阱容量与PPD电容的关系可以表示为[17]

KFWC=(Vpin-VB)×CPPD

(7)

其中,KFWC为满阱容量;Vpin为TG开启时PPD沟道N区所能达到的最高电势;VB为TG关闭后PPD沟道N区所能达到的最低电势;CPPD为PPD电容。

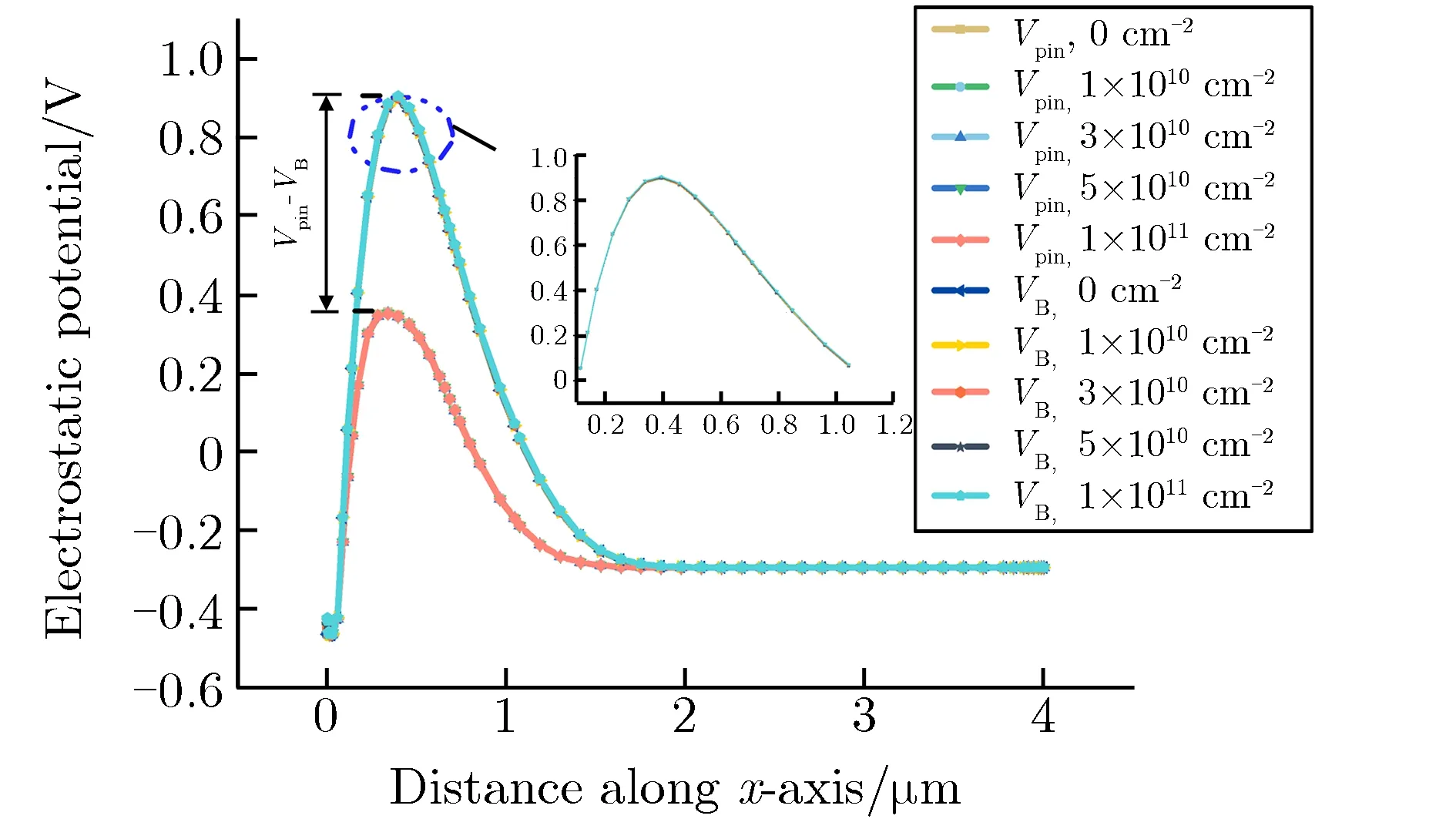

耗尽层N区电压很难在实验中测得,但是在模拟研究中不仅可以直观的观察到辐照前后电势变化,而且可以精准获得耗尽层N区电势。图2为能量为10 MeV,不同注量质子辐照时,沿A1B1处TG开启前后电势分布。

图2 能量为10 MeV,不同注量质子辐照时,沿A1B1切线处Vpin和VB电势分布Fig.2 Vpin and VB potential distributions alongA1B1 at different fluences of 10 MeV

由图2可见,Vpin与VB基本不发生变化,表明质子辐照对Vpin与VB的影响可以忽略,这与文献[18]结果相吻合;满阱容量主要受CPPD的影响,下面分析质子辐照对CPPD的影响。

PPD电容由势垒电容和扩散电容组成,其中,扩散电容只有PPD在外加正向偏压时才存在,但CMOS图像传感器在工作过程中,PPD无外加偏压,所以PPD电容只由势垒电容构成,等效为一个平行板电容,可表示为

(8)

其中,A为PPD底面面积;ε0为硅的绝对介电常数,值为8.85×10-14F·cm-1;εr为硅的相对介电常数,值为11.9;XD为耗尽层宽度。

图3为质子辐照前后耗尽层展宽模拟结果。由图3可见,随着质子注量的增加,PPD耗尽层宽度随之增加。这有2方面原因,一是辐照导致界面陷阱密度增大,造成埋沟型PPD光电二极管中的P型重掺杂有效浓度的降低,使得重掺杂功能失效;二是辐射诱导产生的正氧化物陷阱电荷会在界面处产生一个额外的电场。这2种因素共同作用导致耗尽层宽度变宽。XD增大导致PPD电容CPPD变小,随着辐照质子注量的增大,在SiO2和STI浅沟槽隔离区中产生的氧化物陷阱电荷则越多,加剧了耗尽层展宽,导致满阱容量的退化。

(a) Before irradiation

2.2 TG沟道势垒退化分析

TG沟道是PPD耗尽层累积的光生电子被FD节点收集所经的途径,势垒的高度影响着电荷的转移效率。质子辐照器件后,在传输栅TG下的氧化层中产生氧化物陷阱电荷,氧化物陷阱电荷带正电,会在TG沟道的Si-SiO2界面处产生感应负电荷,使该区域中的电子浓度上升,导致TG沟道势垒下降。原本PPD耗尽层电势低于TG沟道势垒,载流子在TG开启前无法穿越势垒而在耗尽层中累积。由于TG沟道势垒下降,使PPD耗尽层部分区域电势高于TG沟道势垒,载流子在TG开启前就穿越势垒区到达FD节点,形成漏电流。为了更好理解质子辐照损伤机理,图4为质子辐照前后,TG沟道势垒对满阱容量影响机制。

(a) Before irradiation

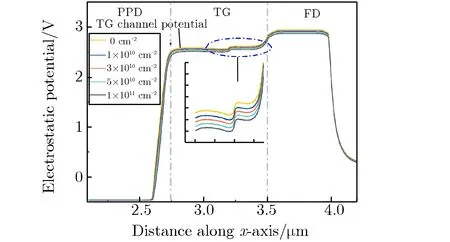

能量为10 MeV,不同注量质子辐照下,y=0.01 μm切线处的电势分布如图5所示。由图5可见,TG沟道势垒随质子注量的增加而减小,将导致PPD内电子提前泄漏到FD中,使PPD耗尽层始终无法达到饱和状态,造成满阱容量下降。

图5 能量为10 MeV,不同注量质子辐照下, y=0.01 μm切线处的电势分布Fig.5 Potential distributions at the tangent of y=0.01 μmwith 10 MeV at different fluences

2.3 FD与衬底形成的耗尽层分析

4T CMOS图像传感器的PPD耗尽层与FD节点之间是硅衬底,之间的距离为TG传输管的栅长。由于FD节点和衬底中的掺杂类型和浓度不同,在FD节点与衬底之间形成了一定宽度的耗尽层。当质子辐照器件后,耗尽层宽度展宽,使得PPD靠近FD节点一侧处在FD与衬底形成的耗尽层内,导致靠近FD节点这一侧累积的光生电子在电场作用下漂移到FD中,同时还可能存在由扩散引起的自PPD流向衬底的PN结反向电流。图6为质子辐照前后,TG开启前FD节点与衬底之间耗尽层展宽模拟结果。

(a) Before irradiation

质子辐照导致FD与衬底形成的耗尽层展宽,提前产生由PPD流向FD中的漂移-扩散电流,使PPD耗尽层始终无法达到饱和状态,造成满阱容量下降。

3 抗辐射设计方案

CMOS图像传感器抗质子辐射设计主要结合像素内部结构和工艺参数进行优化,从PPD电容、TG沟道势垒及FD与衬底形成的耗尽层优化设计3个方面展开。

3.1 PPD电容优化

第2节研究表明,质子辐照会造成PPD耗尽层展宽,使PPD电容下降,满阱容量退化。为了避免质子辐照在SiO2和STI浅沟槽隔离区中产生的氧化物陷阱电荷对PPD耗尽层产生影响,有2种方案可以进行优化:第一种方案是增大PPD中的P+钳位层掺杂浓度;第二种方案是增大P+钳位层掺杂的结深。

质子辐照注量为1×1011cm-2,P+钳位层掺杂浓度为2.3×1017,4.6×1017,2.3×1018,2.3×1019cm-3时,PPD耗尽层展宽模拟结果如图7所示。

(a) 2.3×1017 cm-3

由图7可见,随着P型掺杂浓度的增加,PPD耗尽层展宽逐渐减小,表明增加P+钳位层掺杂浓度可有效减小质子辐照对CMOS图像传感器PPD电容的影响,当P+层掺杂浓度超过N型区域掺杂浓度(1016cm-3量级)2个数量级时,PPD电容基本不受辐照影响。P+层掺杂浓度不能过大,高浓度的P+掺杂会使得该层与传输管的接触区域P型浓度过高,严重影响传输管开启时电子转移通道的形成,或造成局部通路提前夹断[19]。

质子辐照注量为1×1011cm-2,掺杂结深分别为0.01,0.02,0.04,0.05 μm时,PPD耗尽层展宽模拟结果如图8所示。

由图8可见,随着P型掺杂结深的增加,PPD耗尽层展宽逐渐减小。表明增大P型掺杂结深可有效减小质子辐照对CMOS图像传感器PPD电容的影响,提高图像传感器抗质子辐照能力。结深过深会导致N-PD与P-PD形成的耗尽层向下移动,降低短波长光生电子的收集效率。

(a) 0.01 μm

3.2 TG沟道势垒优化

在TG沟道中,工艺的偏差和结晶缺陷重金属污染会产生阻碍电子转移的势阱或者势垒,尤其是靠近PPD一侧区域是辐射敏感区,PPD中N型区域的扩散会导致TG沟道阈值电压变低,很容易形成电子势阱,质子辐照会加剧势阱深度影响电子的传输。为了消除势阱的影响,通过引入非均匀传输沟道的设计,在该区域增加1次P型掺杂来消除上述N型区域的影响。

P型掺杂的位置非常重要,只有根据PPD中N型掺杂的扩散情况来选择合适的P型掺杂位置才能够消除TG沟道下的电子势阱。质子辐照注量为1×1011cm-2,掺杂长度LP分别为0,0.4,0.6,0.8 μm时,TG沟道电势分布如图9所示,电势沿着AB路径的分布变化关系如图10所示。由图9和图10可见,P型掺杂长度选择不合理,会导致势阱的产生。因此,本文LP取0.6 μm。

(a) 0 μm

图10 不同P型掺杂长度下,沿切线AB处电势分布Fig.10 Potential distribution along tangent ABat different P doped lengths

3.3 FD与衬底形成耗尽层优化

质子辐照下FD与衬底耗尽层展宽,使得PPD靠近FD节点一侧累积的光生电子在电场的作用下做漂移运动流向FD,导致光生电子在曝光期间提前泄漏,满阱容量下降。根据半导体物理理论,PN结P区和N区的耗尽层宽度可表示为[20]

(9)

(10)

其中,WDP为P区耗尽层宽度;WDN为N区耗尽层宽度;VD为PN结内建电势,一般在0.6~ 0.9 V之间,本文取0.75 V;V为PN结两端的电势差,正向时V>0,反向时V<0,本文取-2;ND为施主掺杂浓度;NA为受主掺杂浓度。由式(9)和式(10),可得P区耗尽层宽度WDP=2.56 μm。FD与PPD之间的距离即TG传输管的栅长为300 nm,说明PPD靠近FD一侧绝大多数区域将处于FD与衬底形成的耗尽层之中,可能导致TG传输栅开启前,PPD内的电子提前泄漏到FD中。

为避免PPD中产生的光生电子受到FD与衬底形成的耗尽层的影响,4T CMOS图像传感器通常会引入防贯穿注入层(APT)。通过计算,当APT层掺杂浓度为1×1017cm-3量级时,可使WDP变为原来的10%。由于非均匀掺杂的引入,需要对APT层的注入位置进行优化。APT的左边界距TG右边界距离为0.1,0.2,0.3 μm时,TG沟道电荷的转移分布如图11所示。由图11可见,APT层可以防止光生电荷的提前泄漏,但不可避免会阻碍光生电荷的转移,增大APT层的宽度虽然增强了隔离效果,但降低了电子转移效率,所以需在选择较好的隔离效果与较高的电荷转移之间进行平衡。

(a) 0.1 μm

4 结论

本文以4T CMOS图像传感器为研究对象,开展了10 MeV不同注量质子辐照损伤模拟研究,分析了不同注量质子辐照对光电二极管(PPD)电容、TG沟道势垒以及浮置节点(FD)与衬底形成的耗尽层的影响,揭示了质子辐照对满阱容量的损伤机制。在辐照损伤机理分析的基础上,对3个敏感区域进行优化设计,有效提高了满阱容量抗质子辐照能力。研究结果表明,质子辐照会导致PPD耗尽层展宽,使PPD电容下降;质子辐照在氧化层中产生正氧化物陷阱电荷,使TG传输门沟道的Si-SiO2界面处产生感应负电荷,导致TG沟道势垒下降,同时造成FD与衬底之间的耗尽层展宽,导致PPD内光生电荷提前泄漏,满阱容量下降。通过合理增加P+层掺杂浓度和结深、在TG沟道增加1次P型掺杂并优化其位置及优化APT隔离层宽度可有效提高4T CMOS图像传感器满阱容量抗质子辐照能力。