基于多核CPU的雷达信号并发处理架构设计

2021-11-09杨思军

杨思军

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225101)

0 引 言

智能化是电子装备未来发展的必然趋势,而要将当前的数字化装备发展为智能化装备,“软件化”是必由之路,也是未来构建智能化电子装备的基础和平台。雷达作为主要的电子装备产品,其软件化设计更能适应任务需求的多样性和多功能一体化的要求,并可实现软硬件解耦和功能重构,完成无人值守等任务需求。而要实现软件化雷达信号处理,首先要解决的就是雷达信号处理的实时性问题,为此在硬件平台的选择、软件的架构设计以及数据实时传输等方面都要考虑周全,才能确保处理的实时性。

随着计算机多核中央处理器(CPU)、高速存储器以及多任务多线程编程技术的快速发展,计算机的计算能力、处理能力和运行效率得到了很大提高,强大的浮点运算能力和易于开发的软件技术使计算机能够更灵活、快速、准确地完成数据处理工作,为雷达信号处理软件编程带来极大的方便,将逐步取代传统的硬件平台,实现雷达系统的软件化设计。

1 多核超算CPU

多核超算CPU的每个处理器核支持2个硬件线程,也称为“超线程”CPU[1]。它可以对相互不依赖的操作指令打乱顺序执行,提高CPU处理速度。多核CPU从最初的2核、4核,跨越到目前的8核、16核,甚至到32核,然而多核CPU要想充分发挥其效能,在软件设计上必须充分利用其并发处理技术,这已成为计算机设计和应用中不可回避的问题。如何实现多核CPU的并发处理能力,可以参考图形处理器(GPU)的设计和处理模式。

最初CPU的设计主要是针对执行大量离散而不相关任务的系统,而GPU的设计主要是解决那些可以分成成千上万个小块并可独立运行的问题[1]。根据这个思路,在雷达信号处理软件设计上,可将模数(AD)采样后的雷达数字回波按脉冲重复时间(PRT)或波束相参组进行数据打包,分成适合多核CPU处理的多个小块可独立运行的数据包,进行并发处理。

2 数据流驱动模式

数据流驱动机制则允许任何指令均由数据可用性来驱动。指令的执行完全受数据流的驱动,其顺序只受指令中数据相关性的制约,而与指令在程序中出现的先后无关。只要数据不相关且资源可利用,就可以并行,从而有利于并行性的开发[2]。

雷达信号处理流程最显著的特点就是各功能模块的流水性,其前后数据的迭代性和相关性较弱,不同于航迹处理是一个闭环迭代的过程。雷达信号处理流程可以划分为一些功能模块,其中某一个或几个模块的输出作为下一个或几个模块的输入,这是一种粗粒度的数据流驱动方式,各模块之间的输入输出关系就是数据流驱动关系。采用数据流驱动机制,相应数据包到达,即可执行各功能模块的处理指令。一个完整的雷达信号处理流程大体可分为舰速补偿、脉冲压缩、副瓣对消或副瓣匿影、杂波抑制、恒虚警等模块。各模块可独立工作,模块之间每次输出的各距离单元或脉冲数据无关联,适合CPU并发编程。

在架构设计时,将雷达信号处理系统采用数据流驱动机制,目的在于摒弃硬件同步信号,充分利用CPU多核资源并发编程,实现系统的并行性处理,使系统尽可能高速有效地工作。

3 线程池加速处理技术

就像在单核处理器中,操作系统的任务是分时、轮流运行的,每个任务只能运行一小段时间,仿照GPU线程模型的设计思路,分配实际数量多于物理CPU核数的多个任务同时运行的并发处理模式。并发处理模式同时可以解决CPU处理失速状态,这种现象通常是由I/O操作和内存获取引起的,CPU在上下文切换时会出现此类现象,假定此时有足够多的任务,线程的运行时间也较长,那么它将正常地运转,从用户的角度上就感觉不出CPU失速的状态[3]。

多核处理器主要用于实现任务并行,这是一种基于操作系统的并行处理,主要方式是利用多线程来发挥处理器中的多核作用。线程是程序中的一个独立执行流,它可以在主执行流的要求下分出和聚合。通常情况下,CPU程序拥有的活动线程数量不超过其包含的物理处理核数量的2倍,来实现线程池加速技术。

线程池技术是指程序开始时创建若干个线程,当有任务时交给池中的空闲线程执行,执行完毕后线程不销毁而是备用。当执行大量异步任务时,线程池能够提供较好的性能,这是因为线程池复用了线程,可以使每个任务的调用开销减少。从实时性考虑,线程级处理要比进程处理快得多,线程操作的是一个共享的内存空间。这可以带来不借助消息就可以完成数据交换的便利,线程代码的上下文由操作系统保存,数据空间是共享的,缺点是缺乏对共享数据的保护。另一方面,线程池提供了一种资源限制和管理的手段。线程池加速技术不同于OpenMP设计标准,采用OpenMP程序设计相对容易,大多数底层的线程代码都采用Windows线程库函数或POSIX线程库函数实现,而线程池加速技术要用户自己根据实际情况进行多线程并发代码编写。

并发性的首要内涵是,对于一个特定的问题,无须考虑用哪个并行计算机来求解,而只需关注求解方法中哪些操作是可以并行执行的。并发编程会涉及到较多系统资源竞争,比如同时读写共享内容、操作系统层面的线程调度等,因此代码编写要格外小心。下面以脉冲压缩模块为例,设计线程池加速技术:

(1) 在脉冲压缩模块的初始化函数rspl_pulse_compress_init()中事先开辟好脉冲压缩过程中需用到的各种变量和内存空间,即为每个线程开辟好独立的环境变量,避免同时读写共享内容,导致数据不同步。对于脉冲压缩模块来说,环境变量主要包含存储各种码型的匹配滤波器系数、进行快速傅里叶变换(FFT)需要的内存空间,以及舰速补偿等的系数空间。

(2) 根据硬件平台的处理速度和特性,初始化需要开辟线程函数Thread_Function(),建立线程池缓冲区。

(3) 在数据接收线程函数rspl_pulse_compress_entry()中,将接收的数据进行整合处理,根据功能模块特性,分割成适合线程处理的子任务,添加到线程池任务链表中,并释放信号量,激活线程池中的线程处理函数。

(4) 多个线程子函数Thread_Function()并发处理,通过信号量,激活线程池中空闲的线程接收整合的数据块,并调用每个线程的环境变量和空间,进行脉冲压缩处理,并将处理的结果数据整合成数据包,发送给下个模块,实现数据流驱动。

4 仿真验证

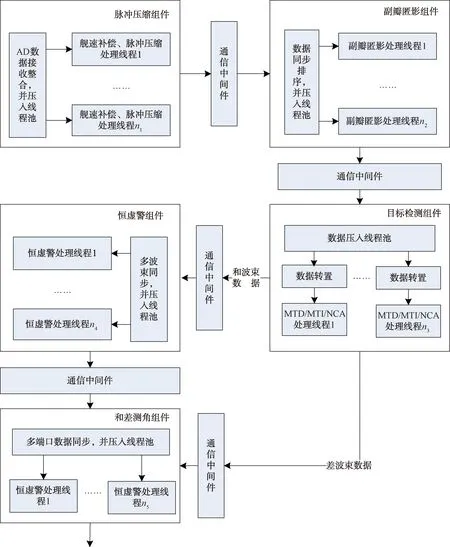

图1是采用超算CPU实现的软件化雷达信号处理并发设计架构框图,有脉冲压缩组件、副瓣匿影组件、目标检测组件、恒虚警组件和和差测角组件5个组件,实现了雷达信号处理的基本功能。各个组件之间不进行互联,而是通过通信中间件进行数据交互。通信中间件屏蔽应用层与底层硬件的差异,实现数据的传输。通信中间件主要包含2种传输模式:一种是组件间的数据传输,在同一个CPU内,采用传址模式保证数据传输的实时性;另一种组件间的数据传输不在同一个CPU内,采用发布订阅传输机制,通过万兆网进行数据传输。采用通信中间件进行数据传输,尽可能少地实现数据搬移,提高处理效率;实现软件的模块化设计,迭代升级;屏蔽IP地址、网络端口等一系列参数,方便实现组件级重构。

图1 软件化雷达信号处理并发设计架构框图

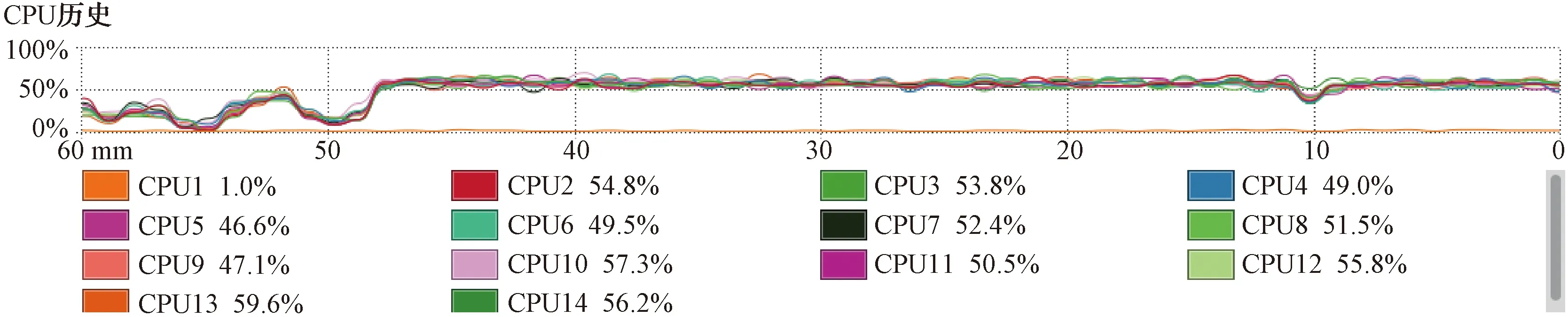

图1中每个组件都有一个或多个输入输出端口和一个线程池,组件将接收的数据压入线程池,释放信号量,等待空闲线程进行处理。根据功能模块算法的复杂度和处理速度,对每个组件合理设置多个并行处理线程。使整个信号处理应用程序达到最佳处理效果,如图2的14个CPU核中,除了第1个CPU核,其余都有50%左右的利用率。第1个CPU核主要由操作系统控制,负责完成CPU处理流程的串行操作。图1中所有组件组合在一起形成一个进程级应用程序,实际占用的CPU数量由设备的数据通过量和使用的CPU线程数决定,它打破了CPU界限的分布。

图2 多核CPU资源利用率

多核超算CPU相对数字信号处理(DSP)芯片主频高、内存大、浮点运算能力强,更能满足雷达信号处理的精度要求,但是CPU都带操作系统,一般无法太快响应外部中断,因此软件设计应扬长避短,将数据以数据流模式传输,以包为单位,以1个脉冲重复时间或者1个相参组脉冲的数据为1包,去掉硬件信号的同步,采用大包传输,多缓冲区缓存,保证数据处理的平均速度满足要求即可。实际测试下来,缓存区过多,也会影响CPU资源利用率及处理速度。

线程池加速技术采用多线程并发处理模式,以数据流驱动模块级联,势必导致乱序执行,因此在需要同步和按顺序执行的功能模块时,需要对零散的数据块进行数据同步、排序处理,以保证功能模块执行的正确。

图1中脉冲压缩组件接收以1个PRT为1包的数字波束合成(DBF)数据或AD采样数据,将接收的整形数据转化为浮点数据,存入多级缓存中,采用第3节中介绍的线程池加速处理技术,实现目标舰速补偿功能和各种调频相位编码的脉冲压缩功能。由于数据是以1个PRT为1包的完整数据,因此不需要排序同步处理,直接压入线程池中等待处理。每个PRT中包含左、中、右3个和波束,1个俯仰角差波束和1个匿影波束总共5个波束数据,每个波束2 048个距离单元的复数数据。脉压后的数据以相同的数据包格式发送到副瓣匿影组件中。每包PRT数据中包含相参组流水号和每个相参组中脉冲的编号,用于实现副瓣匿影组件中的数据同步和排序。同步排序后的数据是以某个波束的相参组为1包的数据流,同样通过线程池加速处理技术,实现副瓣匿影功能,输出只包含主通道的数据,用于后续的目标检测。

目标检测组件接收的数据是按照相参组排好一包包数据流,因此不需要进行同步和排序,通过线程池加速处理技术直接进行动目标检测(MTD)、动目标指示(MTI)和非相参积累(NCA)处理。目标检测组件分2个端口输出,一个端口输出和波束模的数据到恒虚警处理组件,另一个端口输出和波束和差波束的复数数据到和差测角组件。

恒虚警处理组件需要根据左、中、右3个波束的编号和相参组流水号进行数据同步,同步后的数据压入线程池,进行恒虚警处理,处理结果送入和差测角组件。和差测角组件将接收的恒虚警处理数据和目标检测输出的复数数据先通过相参组流水号进行数据同步,同步后的数据压入线程池进行和差测角处理。

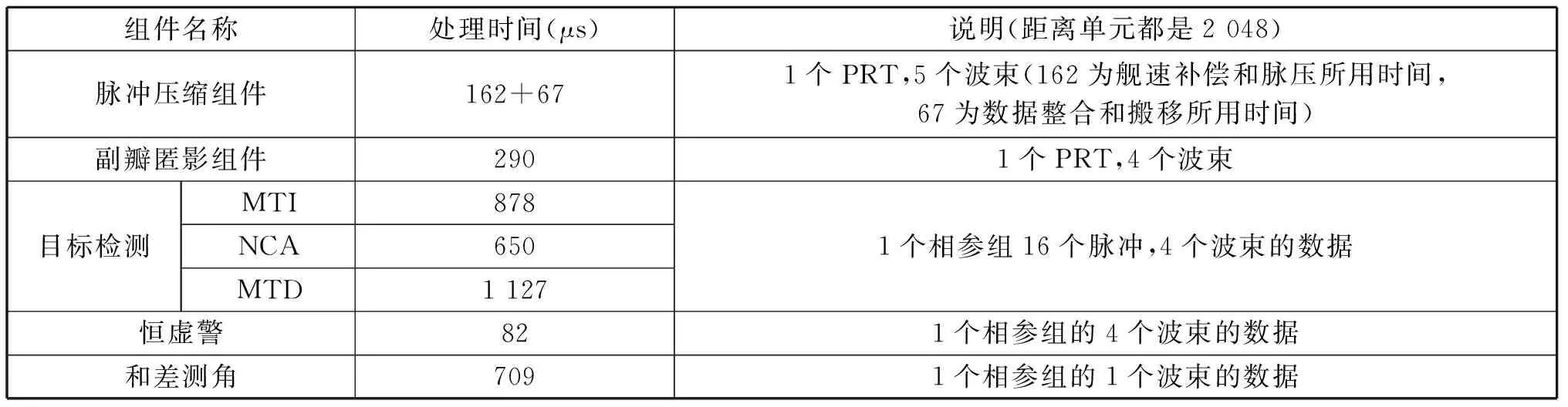

每个组件设计都采用多线程并发处理,要保证整个应用程序达到最佳处理速度,每个组件的线程数的合理设计就显得尤为重要,表1是在X86下采用英特尔数学核心函数库(MKL)和综合性能图元函数库(IPP)实现的单线程雷达信号处理组件的处理速度,可以根据每个组件的处理速度来设置各组件的处理线程数。

表1 单线程各组件处理时间

5 雷达信号处理实时性问题

英特尔至强芯片除了CPU的超线程,还搭载了巨大的三级缓存,并且配合英特尔开发的高度优化、线程安全的MKL函数库和实现了一维信号处理的函数库IPP函数库,同时利用线程池加速处理技术,在图1的软件化雷达信号处理并发设计架构框下,可以实现雷达信号实时处理。至强E5(主频1.8 GHz)系列CPU实现16组1 024点快速傅里叶变换(FFT),单核只需三十几微秒,其处理速度都达到了一般现场可编程门阵列(FPGA)的处理速度。除了速度快,MKL和IPP是线程安全的,MKL或IPP函数无论是在单个线程中调用,还是在多个线程中同时使用Intel,都能够确保函数正确的计算结果。

6 结束语

多核CPU采用线程池加速技术,在并发处理模式下,可实现雷达回波的实时处理;但要实现最优设计,还需根据不同的硬件平台和实际情况进行分析。

(1) 信号量的切换

多线程并发处理必然需要使用同步信号。在不同的硬件平台下,信号量时间的切换各不相同。以计数信号量为例,在X86的架构下,计数信号量的切换平均1 μs即可,而在ARM架构下FT1500A处理器中需要20~30 μs,为此要考虑任务块大小的划分,避免过小的任务块信号量使用频繁,浪费时间。或者在FT1500A处理器平台上,采用互斥信号量配合条件信号量替代计数信号量。

(2) 线程数设置

CPU通过使用寄存器重命名和栈来执行多线程,为了运行一个新任务,CPU需要进行上下文切换,将当前所有寄存器的状态保存到栈上,然后从栈中恢复当前需要指向的新线程上次的执行状态。这些操作通常需要花费上百个CPU时钟周期。如果在CPU上开启过多的线程,时间几乎都花费在上下文切换过程中寄存器内容的换进/换出操作上,有效工作吞吐量将会快速降低。因此并不是线程数越多越好,一般不超过其包含的物理处理核数量的2倍。

虽然雷达信号并发处理架构很多设计思想来源于GPU的设计思路,采用多核处理器,仿照GPU线程模型,同一时刻可以存在大量同时执行的线程,以期带来高吞吐量。但是,由于GPU架构中计算能力较强,逻辑控制单元较弱,GPU不适合开发逻辑较为复杂的并发程序[4]。作为通用处理模块,多核CPU是一个很不错的选择。

带有特定算法硬件加速的多核超算CPU,配备相应的操作系统,既具备浮点强运算能力,又具备高效管理流程,相较DSP、FPGA和GPU,具有更高的处理时钟和内存,可以完成算法更复杂、消耗内存更大的自适应副瓣对消、二维合成孔径雷达/逆合成孔径雷达(SAR/ISAR)成像、多参数波形分集抗干扰以及多域多维度特征无监督学习与检测识别技术等复杂算法。

同时带操作系统的硬件平台可以实现软硬件解耦,通过通信中间件、计算中间件以及存储中间件等实现软件的迭代升级、快速移植和产品的研发。