浅析CMOS图像传感器晶圆级封装技术

2021-11-04马书英郑凤霞刘玉蓉肖智轶

马书英,王 姣,刘 轶,郑凤霞,刘玉蓉,肖智轶

(华天科技(昆山)电子有限公司,江苏昆山215300)

1 引言

2000年夏普推出第一款可拍照的手机,经过二十多年的发展,手机已成为人们日常生活中必不可少的工具,其中摄像是智能手机的核心功能之一,各大手机厂商均把拍摄性能作为产品的关键竞争指标。手机摄像头的演变也日新月异,最初的手机是单个摄像头,但是由于智能手机摄像头尺寸较小,单个CMOS(Complementary Metal Oxide Semiconductor)图像传感器(CMOS Image Sensor,CIS)感光性能有限,为了呈现更好的拍照效果,将原先集成在一个摄像头上的多种功能分解成多个单一功能摄像头,如广角、长焦、微距等,促使了后置双摄、前置双摄,再到3D感应模组、后置三摄、四摄、五摄等多摄视觉解决方案的出现。多摄像头的出现在提升图像质量的同时,促进了图像传感器市场规模稳步提升[1]。2019年,全球智能手机图像传感器出货量超过47亿颗,同比增长15%。2020年华为推出的P40 Pro+型号手机,摄像头多达7个,这表明未来智能手机摄像头市场仍然会保持稳步增长。

与此同时,随着无人驾驶的兴起,CIS在汽车摄像头市场也得到了迅猛的发展。先进辅助驾驶系统(Advanced Driving Assistance System,ADAS)的普及导致每辆汽车至少有8个摄像头,包含后视摄像、全方位视图系统、摄像机监控系统等[2-6]。据Yole统计,2016—2018年全球车载CIS市场规模分别是5.4亿美元、6.6亿美元、8.7亿美元,预计2023年达到32亿美元,年复合增长率高达29.7%,汽车将会成为仅次于手机的第二大CIS应用领域。其他新的应用,如安防、无人机、机器人、虚拟现实、增强现实等,也将给全球CMOS市场的增长提供动力[7-8]。

图像传感器主要生产商有索尼、三星、豪威、安森美、格科微、海力士、思特威等,排名第一的是索尼,市场份额高达53%;排名第二的是三星电子,市场份额为18%;第三是豪威科技,市场份额为11%;第四是安森美半导体,市场份额为4%。四大生产商占据全球85%的市场。国内企业格科微在低端市场(像素小于16 M)优势明显,尤其是2 M、5 M等产品,市占率达到34%。思特威在安防监控摄像头和车载摄像头领域持续发力,相继推出多款产品,市场反响良好,发展势头迅猛。

在CIS产业规模日益扩大的背景下,本文介绍了CIS的主要结构,回顾了CIS的封装技术演变,并根据结构和应用领域的差异详细介绍了基于硅通孔(Through Silicon Via,TSV)技术的多种CIS晶圆级封装技术,指出了CIS晶圆级封装技术的发展趋势。

2 CIS结构

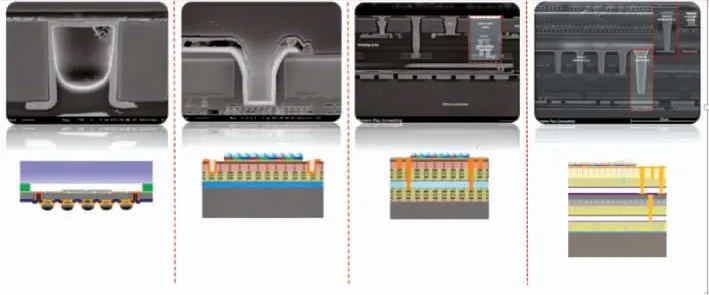

目前CIS可以分为三种结构,前照式(Front Side Illuminated,FSI),背照式(Back Side Illuminated,BSI),堆栈式(Stack)及在Stack基础上演变的Triple Stack,如图1所示。

图1 CIS结构

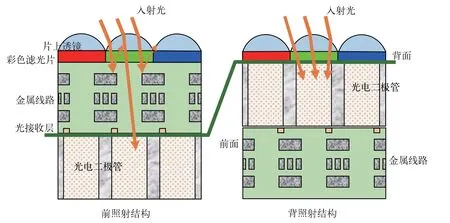

一般的CIS像素都由以下几部分构成:片上透镜(Micro Lenses)、彩色滤光片(On-Chip Color Filters)、金属排线、光电二极管以及基板。传统的CIS是图1中的“FSI”结构,当光线射入像素,经过了片上透镜和彩色滤光片后,先通过金属排线层,最后光线才被光电二极管接收。金属是不透光的,而且还会反光。所以,在金属排线这层光线就会被部分阻挡和反射掉,光电二极管吸收的光线就只有刚进来的70%或更少;而且反射还有可能串扰旁边的像素,导致颜色失真。目前中低档的CIS排线层所用的金属是比较廉价的铝,铝对整个可见光波段(380~780 nm)基本保持90%左右的反射率。这样一来,背照式CIS就应运而生了,其金属排线层和光电二极管的位置和“FSI”正好颠倒,光线几乎没有阻挡和干扰地进入光电二极管,光线利用率极高,所以背照式CIS能更好地利用射入的光线,在低照度环境下成像质量也就更好,见图2[9]。

图2 FSI和BSI图像传感器

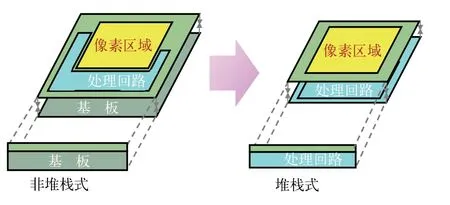

BSI感光单元的基板上不全是受光区,还有相当大的面积是电路板。如果能移除电路板,受光区域就会明显增大,于是新的设计就是将电路板放到受光区下面,形成堆叠的结构,这种设计叫堆栈式(Stacked),堆栈式CIS见图3[10]。它可以显著增加每个单元的受光面积,面积越大,受光也就越多,代表输入信号也越强。但商家更乐意将这种技术用到提高像素方面,因为即便缩小感光单元,受光面积依然可以保持不变,意味着画质不会下降,同样规格的感光器上可以放置更多的感光单元,从而提高像素密度和总像素数量,第一颗堆栈式感光器的总像素达到了1300万,而画质也有了显著的提升。从结构上说,堆栈式应该属于背照式的一种。

图3 堆栈式CIS

3 CIS封装技术演变

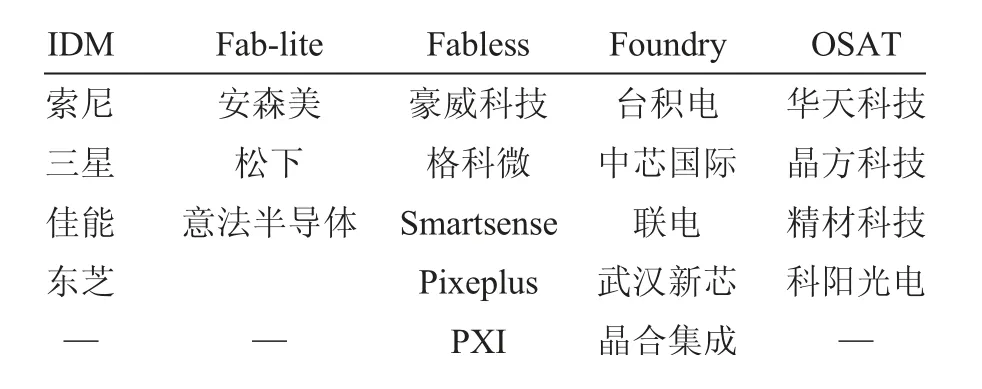

CIS封装最初采用的是带有玻璃盖板的陶瓷封装,例如Amkor公司的VisionPak就是一种陶瓷无铅芯片载体。这种方案比较昂贵而且会占用很大的相机内空间。20世纪末晶圆级封装(Wafer Level Package,WLP)技术逐步发展起来,其优势在于尺寸小、重量轻和成本低,并逐渐引起大家的关注。2007年3月,日本Toshiba公司首次展出采用硅通孔(Through Silicon Via,TSV)技术的WLP小型图形传感器模组,该技术不仅提供用于模块集成的完全密闭的器件,使由污染颗粒所导致的CIS成品率损失大大降低,还具有当时业界最小尺寸和质量、有效降低寄生效应、改善芯片运行速度和降低功耗等优点[11-12]。如今全球只有台湾积体电路制造股份有限公司(台积电)下属公司精材科技、华天科技(昆山)电子有限公司、晶方科技、科阳光电4家OSAT(Outsourced Semiconductor Assembly and Testing)可以提供图像传感器WLP解决方案,其中华天科技(昆山)和晶方科技能够提供12英寸图像传感器WLP服务。表1列举了全球CIS各环节主要供应商。

表1 CIS各环节主要厂商

4 CIS WLP技术

CIS根据其结构和应用领域不同,采用的WLP结构也不同。华天科技(昆山)电子有限公司可以提供8英寸/12英寸基于TSV技术的全套图像传感器WLP技术,含激光打孔技术、平面停留技术、UT(Ultra Thin Process)半切技术和直孔技术。

4.1 激光钻孔技术

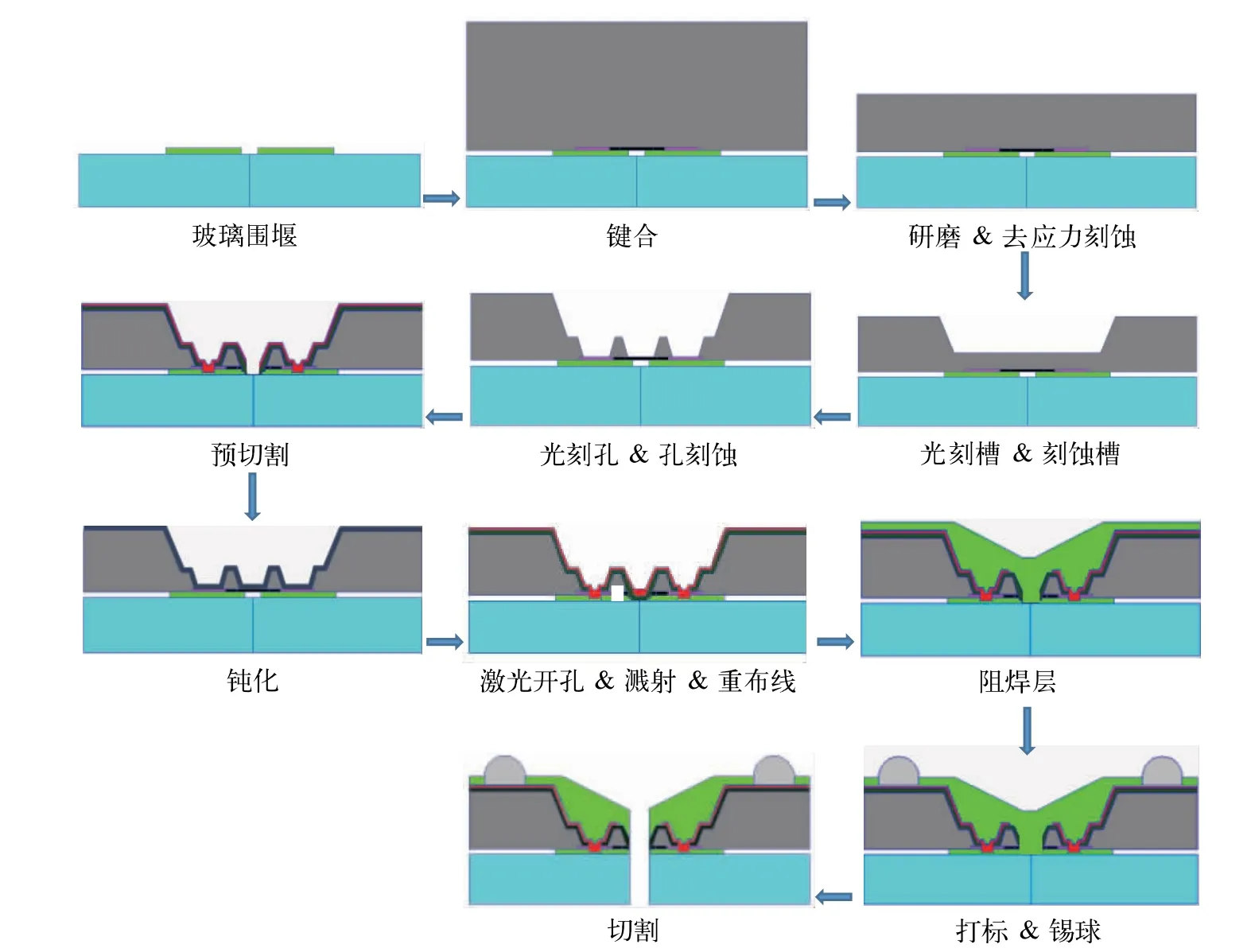

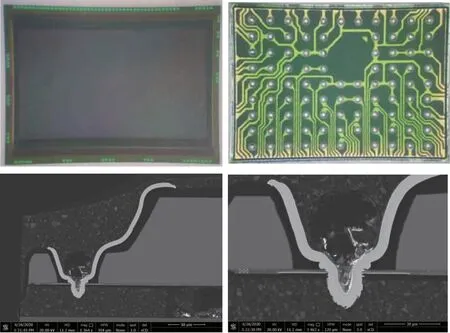

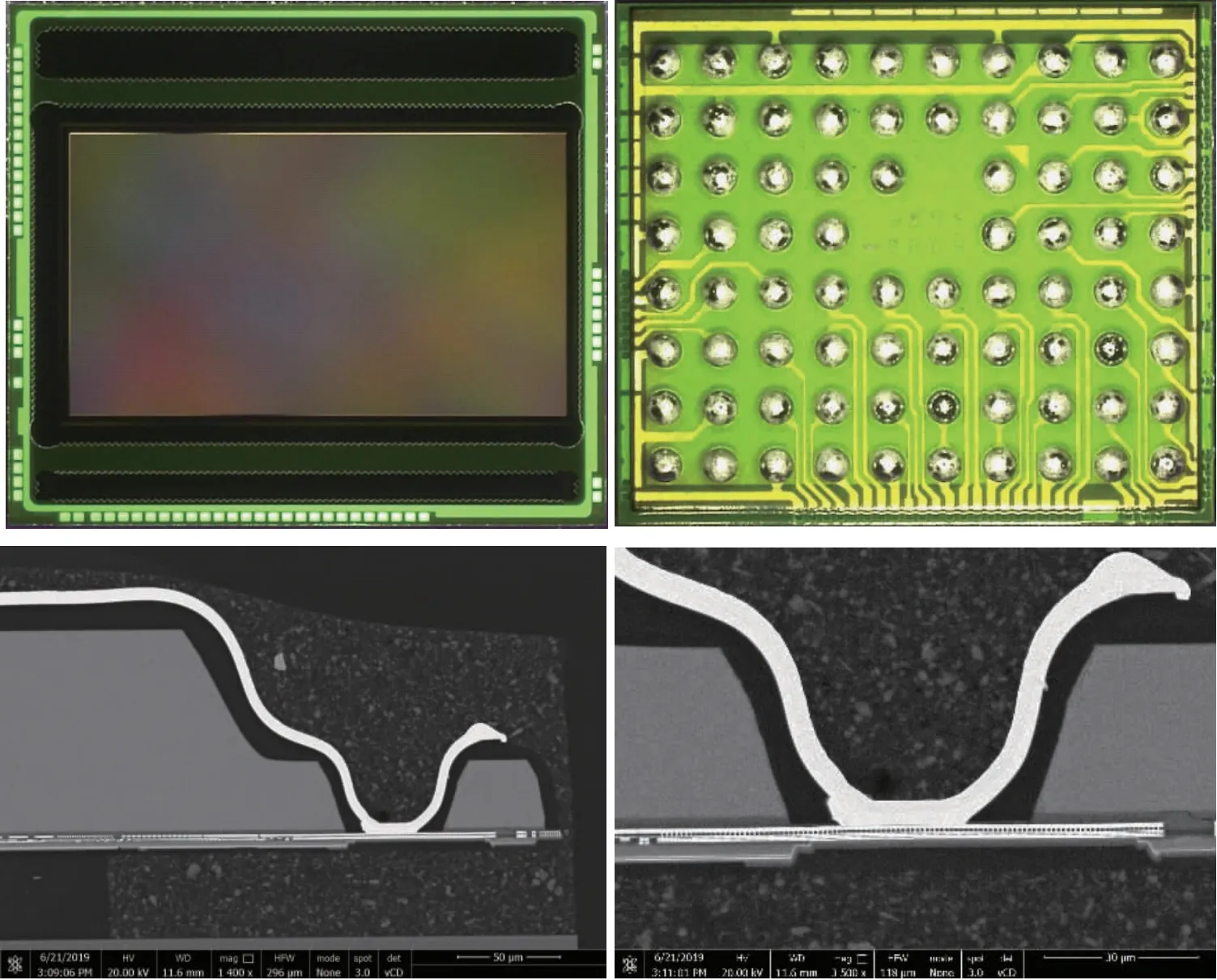

激光钻孔技术主要应用于消费类图像传感器封装,封装工艺流程如图4所示,先采用光刻胶在光玻璃上制作围堰,空腔大小根据芯片传感器区域确定,再通过晶圆永久键合将来料预处理好的晶圆和带围堰玻璃进行键合。键合片通过机械研磨达到预设厚度,再通过干法蚀刻去除应力。通过涂布曝光显影和干法刻蚀形成双台阶通孔,双台阶厚度配比根据客户要求总厚度和金属Pad Pitch来决定。为了增强芯片可靠性,通常采用预切割方式达到芯片包边的效果,采用机械切割打开切割道,切入围堰[13]。再通过喷涂工艺在硅基表面形成一层聚合物绝缘层,聚合物绝缘层不但能达到绝缘效果,同时还能形成侧边保护,阻碍水汽对芯片的侵蚀。采用激光打孔技术直接穿透绝缘层和金属Pad,再溅射Ti/Cu种子层,通过电镀和化学镀工艺形成互联线路,将Pad信号引到晶圆背面,为了保护线路在表面涂布一层阻焊层,光刻形成焊盘开口,再通过印刷工艺形成焊球,最终通过切割形成单颗封装完成的芯片。图5是激光钻孔技术封装成品的外观图和SEM图。

图4 激光钻孔封装工艺流程

图5 激光钻孔技术封装成品外观图和SEM图

4.2 平面停留技术

平面停留工艺和激光打孔工艺流程类似,主要应用于安防监控芯片和车载影像芯片,通过光刻使金属重布线层(Redistribution Layer,RDL)和金属Pad直接接触连接,该连接方式接触面积更大,可靠性更好,同时解决了部分BSI/Stack Wafer不能打孔的问题。平面停留工艺流程如图6所示,涂布完绝缘光刻胶后通过光刻显影去除金属Pad上方的绝缘胶,再通过整面干法刻蚀方式去除Pad最表层的二氧化硅绝缘层从而暴露Pad,后续制程和激光打孔工艺类似[14-15]。图7是平面停留技术封装成品的外观图和SEM图。

图6 平面停留工艺封装工艺流程

图7 平面停留技术封装成品的外观图和SEM图

对比两种封装技术,激光打孔结构的流程相对简单,成本更低,但要求来料晶圆的金属Pad下方不能有线路或者其他功能设计,对晶圆制造工艺也有要求,功能层不能有Low-k材料,否则激光打孔会引起延裂,从而导致产品失效。由于RDL和金属Pad是通过激光打出的孔形成环形接触,可靠性表现不如平面停留工艺[16-17]。华天科技(昆山)电子有限公司采用平面停留工艺封装的车载图像传感器芯片在国内率先通过汽车行业AEC-Q100认证。

4.3 UT半切技术

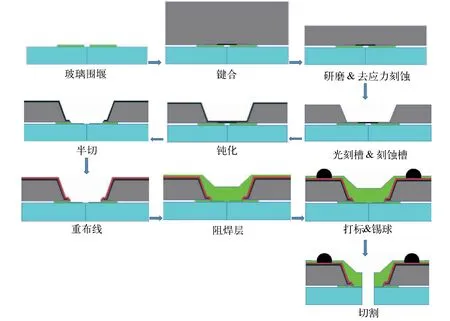

UT封装技术主要适用于Pad间距较小(不大于110μm)且芯片Seal Ring在Pad内侧的产品,其封装流程如图8所示。

图8 UT半切封装技术流程

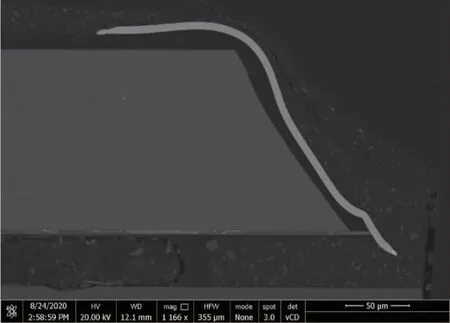

首先制备空腔玻璃,将空腔玻璃与晶圆正面键合。利用研磨工艺对背面减薄,通过干法蚀刻去除研磨产生的应力层并且对硅基进一步减薄。再采用光刻和刻蚀工艺去除Pad上方的硅基,并在表面覆盖一层钝化胶。然后采用半切技术利用高速旋转的角度刀将Pad打开并切入键合胶层,之后进行重布线并制作引出端焊球,最终切割成单个封装体。图9为UT半切结构封装后的SEM切片图。UT封装技术的优势在于可以增加后续所做线路与Pad的接触面积,同时Pad及金属线路的尾端通过阻焊胶(Solder Mask Film,SEM)包边,有效提升了产品可靠性。另外,UT封装技术采用一步硅刻蚀后,再利用半切技术将Pad侧面打开,可以减少Pad上方氧化层刻蚀工序,并且也避免了激光打孔对Pad损伤的风险,可以节约成本,减少制样周期,增加产品的可靠性。

图9 UT结构SEM切片图

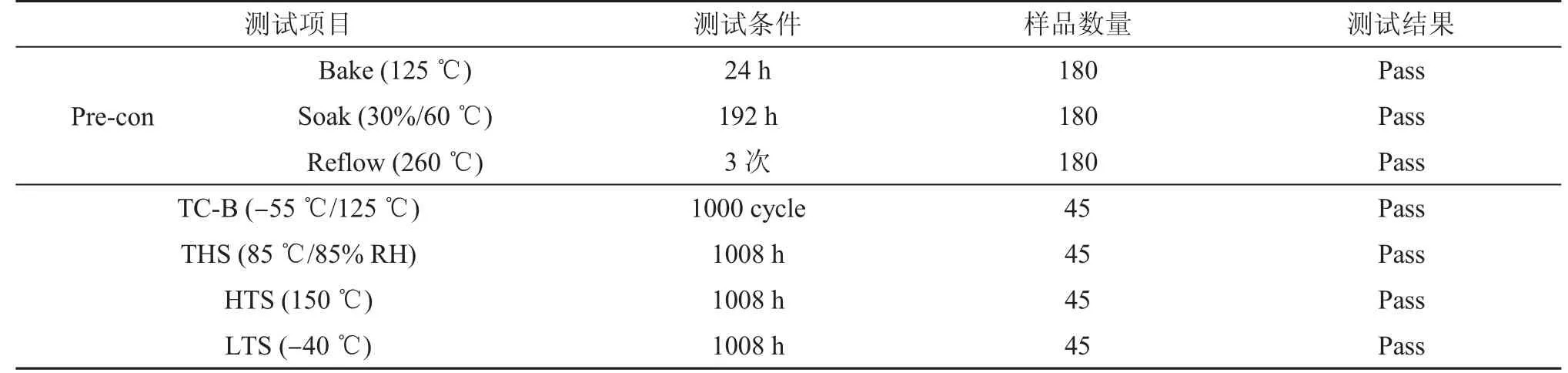

目前UT封装技术主要应用于消费类、安防类等产品,且能满足该类产品的信赖性要求。按照JEDEC(Joint Electron Device Engineering Council)标准进行可靠性验证,每种条件各投了45个产品,具体可靠性项目如表2所示,实验结果显示可靠性结果Pass,且未发现分层,断裂等失效[18]。但是UT封装技术也存在局限性,如果产品的Seal Ring在Pad外侧,则无法采用该类封装结构。

4.4 直孔结构封装技术

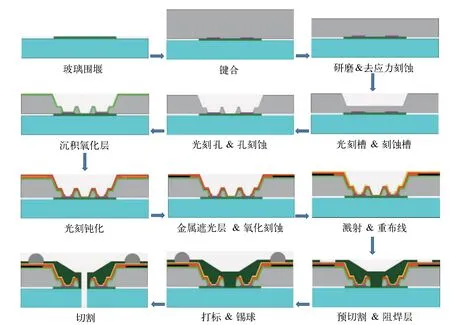

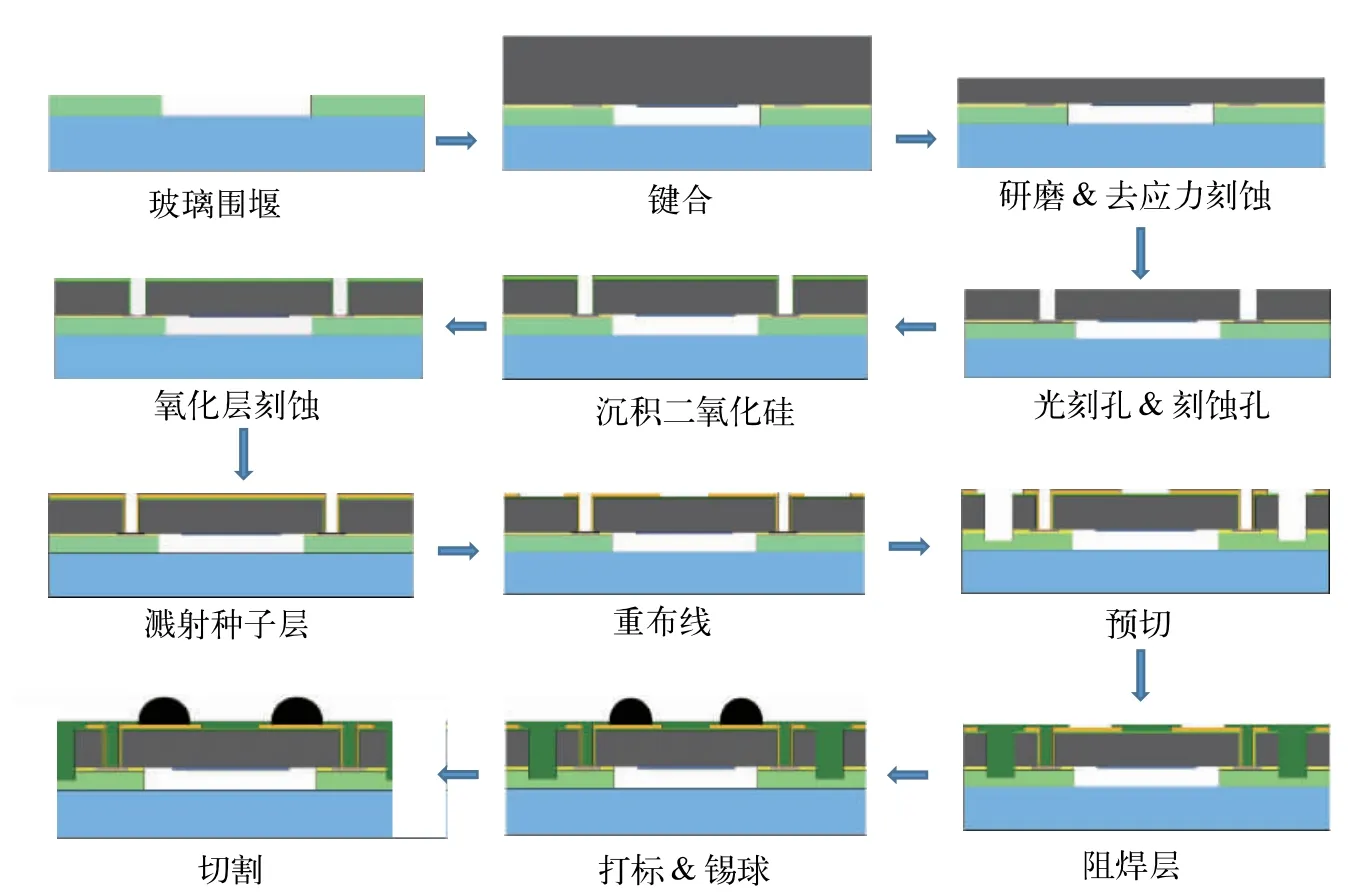

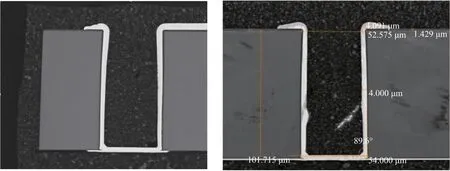

随着CMOS制造工艺的演变,由原先的FSI变成BSI,再演变到如今的Stack和Triple Stack技术,金属Pad中的Low-k材料非常易碎,给封装带来很大挑战。为了满足新兴的CIS晶圆级封装,华天科技(昆山)电子有限公司开发了垂直通孔封装技术。该技术可以满足I/O(Input/Output)数目更多、可靠性要求更高、金属Pad结构更复杂的芯片的封装需求。直孔封装工艺流程如图10所示,首先将来料预处理晶圆和做好围堰的玻璃进行晶圆级永久键合,通过机械研磨和去应力刻蚀达到规定的厚度。采用Bosch刻蚀工艺形成垂直通孔,直孔蚀刻是关键工艺步骤,直孔刻蚀中常见的Scallop、Footing、Notch等问题都会对产品电性能产生较大影响。刻蚀完成后采用超声波清洗去除表面由刻蚀生成的氟化物,清洗效果将直接影响后续的二氧化硅沉积。直孔技术无法采用光刻胶涂布形成绝缘层,因为孔侧壁无法挂胶,因此需要采用PECVD(Plasma Enhanced Chemical Vapor Deposition)沉积二氧化硅绝缘。由于CIS无法耐受超过230℃的温度,因此需要开发低温PECVD技术,解决膜孔底覆盖率、低温膜应力和膜层结合力差的问题。接着是再布线工艺,区别于其他WLP技术,直孔技术需要采用高腔PVD(Physical Vapor Deposition)沉积Ti/Cu种子层,从而满足孔底覆盖率要求,电镀工艺也需要重新优化,增加前处理保证孔底浸润性,实现孔内线路的连续[18-21]。图11为直孔结构SEM图。直孔技术由于通常应用在车载等高端领域,为了保证球高均一性,通常采用植球工艺。直孔技术也通过可靠性验证,测试项目如表3所示。

表3 直孔技术可靠性测试项目

图10 直孔封装工艺流程

图11 直孔结构SEM图

5 结论

本文介绍了几种常见的图像传感器晶圆级封装技术,可以满足FSI、BSI和Stack三种不同CIS的晶圆级封装需求。由于晶圆级封装具有小尺寸、低成本的特点,越来越多不同像素的CIS采用晶圆级封装技术,目前2 M/5 M像素产品是主流,未来随着晶圆级封装技术的不断更新迭代,8 M/13 M像素产品也有望实现晶圆级封装。