微系统发展趋势及宇航应用面临的技术挑战

2021-11-04李培蕾屈若媛姜贸公

张 伟,祝 名,李培蕾,屈若媛,姜贸公

(中国航天宇航元器件工程中心,北京100094)

1 引言

随着我国遥感卫星实现高轨分辨率不断向米级推进,军事通信卫星系统呈现出单星容量不断扩容、传输速率不断提升、新一代导航系统定位精度优于米级的发展趋势。航天器任务的体系化、网络化、智能化已成为未来主流方向。微系统以处理器为核心,包括微电子技术、射频与无线电技术、光电子技术、微机电系统等技术,从系统工程的角度出发,通过单片集成、封装、互联等微细加工等技术,在框架、基板等载体上制造、装配、集成为可提供系统或子系统功能的微小型化器件。微系统作为高度集成的电子产品系统,对于未来宇航装备实现高性能发展将起到越来越强的支撑作用。本文在研究当前国内外微系统技术最新发展趋势的基础之上,结合宇航装备应用需求,分析了微系统电子产品宇航应用面临的技术挑战,并给出了未来微系统宇航应用的发展建议。

2 微系统技术发展趋势

2.1 微系统功能密度、智能化程度不断提升

随着新型架构、新兴材料和先进封装技术的发展,军用微系统正在朝着小型微型化、多功能集成化、灵活智能化等方向发展。从实现方式上来看,一方面重视多种功能的异质、异构集成,在此基础上实现小型微型化;另一方面通过将多个电子元器件进行系统化整合,实现多功能集成化,打造微型系统平台。采用模块化、开放式发展模式,实现先进技术的更快融入和集成,降低系统研发调试的难度和成本;加入自主学习和自主决策能力,提高自适应能力,扩大微系统的作用范围。

美国空军研究实验室代表美国国防部高级研究计划局(Defense Advanced Research Projects Agency,DARPA)授予美国雷神公司空间和机载系统部门“实时可配置加速器(RCA)、时域专用系统级芯片(DSSoC)”项目合同研发异构计算架构,在提供专用处理器性能的同时,保持通用处理器的可编程性。RCA、DSSoC项目寻求利用机器学习、先进异构处理器、通用处理器以及ARM计算软硬件能力来开发新工具和硬件技术,通过单个可编程设备实现多应用系统的快速开发。RCA、DSSoC项目旨在开发由多个内核组成的异构片上系统,这些内核包括通用处理器、专用处理器、硬件加速器、固态存储器和输入/输出。研究内容涉及构建器件工作时可重新配置的硬件和软件,以实现接近专用集成电路的性能,且不会牺牲数据密集型算法的可编程性。Teledyne公司于2009年与DARPA的微系统技术办公室签订合同,开发千吉赫兹电子器件和集成电路。根据DARPA的千吉赫兹电子计划,该公司将研究“革命性的”晶体管技术。HRL实验室是波音公司和通用汽车旗下的研发实验室,其与DARPA合作的GaN项目旨在将GaN应用于碳化硅衬底晶片,研制的集成电路(IC)能够满足最佳的组合效率、输出功率,而此类IC在无线电频率和毫米波半导体技术中同样适用,这类GaN器件和单片微波集成电路(MMIC)将成为促进下一代雷达、电子战系统和通信系统发展的关键。

美国ADI公司和普林斯顿大学合作实现集存储和计算功能于一体的可编程芯片,加速人工智能(Artifical Intelligence,AI)发展,并削减功耗。该芯片基于一种被称为内存计算的技术,可在内存中计算,消除冯·诺依曼架构中最主要的计算瓶颈(存储器墙),内存计算直接在存储中执行计算,从而提高速度和效率。该芯片已集成到可编程处理器架构中,可采用标准编程语言,如C语言,尤其适合在依赖高性能计算但电池寿命有限的手机、手表或其他便携移动设备上使用。

美国DARPA与斯坦福国际研究院签订“终身学习机器(L2M)”项目合同,研发能够持续学习的下一代AI系统,并将在新任务上部署该学习能力以使系统变得更好、更可靠。美国加州大学欧文分校研究团队计划研究海马和皮层的双存储器架构,并将该知识应用于制造智能系统。这些系统通过对比输入和现有存储基础,能够预测可能的输出。从理论上讲,这样的系统可在保持此前学习的基础上变得更具适应性。美国塔夫斯大学研究团队研究了在蝾螈等动物中观察到的再生机理,并以此为基础创造了柔性机器人,这些机器人能够在飞行中改变其结构和功能来适应环境中的变化。斯坦福国际研究院研究团队将研究AI算法,该算法基于存储器合并和回访的生物机制。在该AI技术中,未来的认知系统如自动机器人有望能够在初始部署后持续学习,改进执行性能和整体安全性。

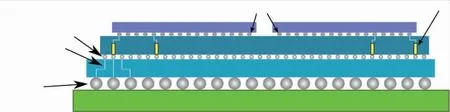

2.2 2.5D/3D先进封装技术助力微系统异质/异构集成

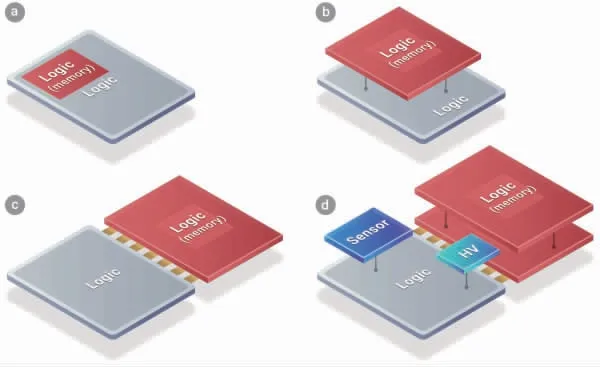

近年来片上系统(System on Chip,SoC)、系统级封装(System in Package,SiP)等微系统产品不断从注重多芯片的多芯片组件(Multichip Module,MCM)封装朝着2.5D/3D、异质/异构集成封装的方向发展,由此带来的新技术包括倒装(Flip-Chip)、微凸点(μBumps)、晶圆级封装(Wafer Level Package)、介质层(Interposer)、再布线层(Re-Distribution-Layer,RDL)、硅通孔(Through Silicon Via,TSV)等[1]。近年来,微系统先进封装技术呈爆炸式发展,如台湾积体电路制造股份有限公司(台积电)的InFO(Integrated Fan-out)、CoWoS(Chip on Wafer on Substrate)、SoIC(System on Integrated Chips)技术,Intel公司的Foveros技术,Amkor公司的SWIFT(Silicon Wafer Integration Fan-out Technology)、HDFO(High Density Fan out)等技术[2]。

台积电于2018年提出的SoIC是一种创新的多芯片堆叠3D封装技术,SoIC基于台积电的CoWoS与多晶圆堆叠封装技术开发,可以达到无凸起的键合结构,把很多不同性质的临近芯片整合在一起,而且其接合材料能直接透过微小的孔隙沟通多层的芯片,使芯片I/O具有强大的可扩展性,实现了高密度的芯片到芯片互连,台积电SoIC封装示意如图1所示。其实现了在相同体积内性能的大幅提升,从外观上看,新集成的芯片就像一个通用的SoC芯片,其尺寸缩小,性能提高,但嵌入了所需的且异质的集成功能。它具有超高密度垂直堆叠,是推进异质芯片集成领域的关键技术支柱。

图1 台积电SoIC封装示意

Intel公司于2019年首次推出Foveros技术,Intel公司Foveros封装结构如图2所示。该技术中Intel公司首次引入了3D堆叠的优势,可实现在逻辑芯片上堆叠功能芯片。主要特点是通过直径为36μm的微凸点进行面对面的芯片对芯片粘接。目前,Intel公司已经有了Foveros技术的芯片样品,并已经做好了规模量产的准备,Intel公司称之为“混合x86处理器“(Hybrid x86 CPU)”。这颗芯片的长宽尺寸只有12mm×12 mm,高度仅仅1 mm,内部3D堆叠封装了多个芯片,待机功耗只有2 mW,最高功耗也不超过7 W[3]。

图2 Intel公司Foveros封装结构

HDFO是基于Amkor公司的SWIFT技术开发而成,是下一代异构芯片封装的发展方向。SWIFT技术是先将有微凸点的芯片互联至RDL预布线的介质层,切单后再倒装至FCBGA基板以完成异构芯片封装。该技术保持了高密度连线,出色的信号质量,且无需TSV,因而可以进一步降低封装成本。HDFO异构芯片封装已成功用于多种应用,包括网通设备、服务器以及多种GPU和FPGA等结构。

近年来,在国家主管机关统筹安排下,按照产品领域和技术领域成体系布局、加强微系统技术和产品开发的协同平台建设的发展理念,中国电子科技集团公司第五十八研究所、西安微电子技术研究所等单位逐步成为国内宇航先进封装技术发展的主力军。FOWLP(Fan-out Wafer Level Package)是一种基于宇航级高密度多芯片重构、晶圆级塑封及多层再布线技术等几大关键技术综合而形成的一种高密度封装技术。中国电子科技集团公司第五十八研究所经过多年发展,已形成较成熟的微系统设计仿真平台和团队,攻克了微纳加工工艺、TSV过孔工艺、晶圆重构技术等关键技术,具备Die-to-Die、Die-to-Wafer、Die-to-Substrate(Si、Glass、BT、LTCCHTCC)高精度微凸点阵列倒装焊接工艺,TSV孔直径为10~30μm,线宽为10μm,RDL层数为1~6层,堆叠层数为10层,并建立了国内先进的微系统工艺平台,成为国内先进封装制造的排头兵。

西安微电子技术研究所是我国航天微电子及封装产业的主力军,于2017年启动了12英寸TSV先进封装生产线项目建设,该生产线兼容8/12英寸晶圆,具备完整的TSV晶圆制备、微模组装工艺能力,互连芯片尺寸为0.05 mm×0.05 mm~100 mm×100 mm,TSV孔直径为10~30μm,硅基板厚度为100~250μm,硅基板最大尺寸为50 mm×33 mm,RDL层数为1~3层。其已打造了国内高水平的三维微系统工艺设计、研发、制造、测试公共服务平台。

2.3 微系统开发生态向快速复用、开放融合方面发展

2.3.1 基于芯粒(Chiplet)的设计方式

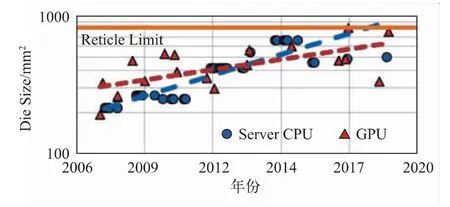

在过去的几年中,摩尔定律的持续放缓对微处理器等超大规模集成电路设计的持续改进带来了各种潜在的阻力,从16 nm/14 nm节点开始,集成电路设计和制造的成本剧增,一个新的工艺节点演进周期从18个月延长至2.5年甚至更长。为了应对这些挑战,基于芯粒的设计理念应运而生,正越来越多地应用于主流微系统电子产品设计中,成为异质集成微系统领域的研究热点。受限于体硅特征尺寸的发展,提高处理器能力和性能的一个可能途径就是制造更大的芯片。但芯片的尺寸目前也逐步达到了光刻的极限[4]。同时小线宽掩模制造成本非常昂贵,而更大的芯片面积大大增加了产生一个或多个制造缺陷的可能性,从而导致低产量和高成本。近年来处理器裸片尺寸的发展趋势如图3所示,从图中可见,裸片尺寸并没有因为集成电路特征尺寸的进一步减小而大幅增大[5]。

图3 微处理器裸片尺寸的发展

基于芯粒的设计思路是通过制造多个更小的芯片,组合起来实现逻辑上的单个微处理器。超微公司(AMD)在2017年发布的第一代AMD EPYCTM CPU处理器上,首次尝试基于微处理器的芯粒设计。该处理器由4个相同的芯片高速缓存组成,采用14 nm工艺技术实现。每个芯片提供8个第一代“Zen”CPU核,2个DDR4存储通道,32路PCle I/O和AMD Fabric互连提供芯片间通信[6]。一个封装由4个芯片组成,共提供32个CPU核、8个DDR4存储通道和128路PCIe I/O。由于封装内的芯片间距离相对较短,因此无需使用硅转接板等更昂贵的解决方案,就可以部署高度优化的高带宽SerDes。成本估算表明,使用芯片的制造成本可以降低41%[7]。

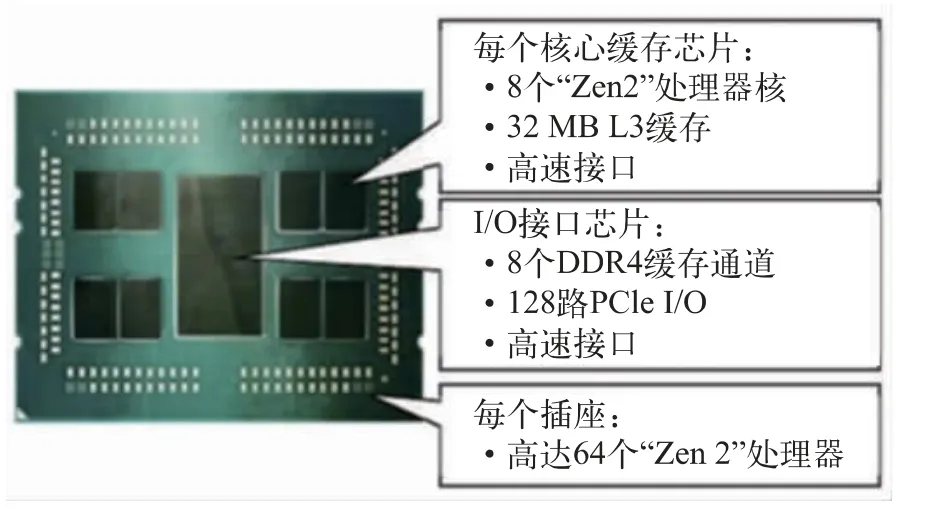

第二代EPYC处理器混合使用了不同工艺节点的芯片,第二代EPYC处理器的组织结构如图4所示。体系结构使用2个不同的芯片,封装中心是I/O模块(IOD)提供了所有的DDR内存控制器和物理接口,IOD周围有多达8个核心缓存芯片(Core Catche Die,CCD),其中每个CCD提供8个“Zen 2”CPU核,以及到IOD的高速接口。其中CCD采用7 nm线宽,DDR4采用12 nm工艺节点。由此可见,通过芯粒封装技术的发展,在相同的封装尺寸下,第二代EPYCTM处理器提供的核总数是第一代处理器的两倍(即64核和32核)。同时,由于多芯片的实现,为系统构架提供了更高的灵活性和可配置特性,每一个单独芯片都可选用不同工艺节点的多种流片设计。

图4 混合工艺节点的第二代AMD EPYC处理器芯粒

国外各大主流集成电路厂商都在芯粒技术路线上规划推出了系列产品。2015年,Marvell公司基于MoChi架构推出了Virtual SoC系列产品,MoChi可以是许多应用的基准架构,包括物联网、智能电视、服务器、笔记本电脑、存储设备等。Xilinx公司于2018年推出包含3个16 nm工艺FPGA和2个动态随机存储器的首款采用CCIX接口的芯片,旨在从裸芯片层面证明CCIX能够支持多核高性能ARM CPU和FPGA加速器。Intel公司于2019年推出Co-EMIB技术,能够将2个或多个Foveros芯片互连,实现更高的计算性能和数据交换能力,还能够以非常高的带宽和非常低的功耗连接模拟器、内存和其他模块,基本达到单芯片性能。

相比于国外已推出的成熟产品,国内也有多家优势单位厂商在芯粒的设计、封装方面开展研究攻关。如上海极戈科技有限公司提出ZiP的集成平台,通过“电路设计+封装+SDK+算法”,实现快速设计到封装,江苏长电科技股份有限公司、天水华天科技股份有限公司、通富微电子股份有限公司等封装优势单位正积极开发用于高性能计算(High Performance Compute,HPC)的2.5D Interposer高端封装技术;北京微电子技术研究所开发集成4个八核处理器芯粒、1个I/O互连芯粒的3300万门FPGA产品,拟实现96 GIPS/192 GFLOPS的信号处理能力。

2.3.2 基于IP的设计方式

IP核的概念源于产品设计的专利证书和源代码的版权,IP核是指已经通过了设计验证、可重用的、具有某种特定功能的模块,设计人员以IP核为基础进行IP复用设计,可以缩短设计所需的周期。IP分为软核、硬核和基于硅片形式的IP,前文所述的Chiplet技术是指对裸片IP进行快速微系统设计转化,而SoC等微系统电子产品集成度高、功能复杂,在研制阶段采用了基于软硬IP核复用的设计方法,如何评测IP核的质量与可靠性是业界所关心的问题。

在2017年11月召开的第7届RISC-V研讨会上,美国DARPA微系统办公室主管阐述了开源硬件知识产权(Intellectual Property,IP)对于国防的重要意义,通过IP核复用以提高研制效率、降低研制成本和时间,但强调开源IP核必须是经过评测合格的[8]。在IP核可复用性方面Synopsys公司与Mentor Graphics公司联合编写了《可重用设计方法学手册》(Reuse Methodology Manual,RMM),定义了IP核可复用的属性[9]。

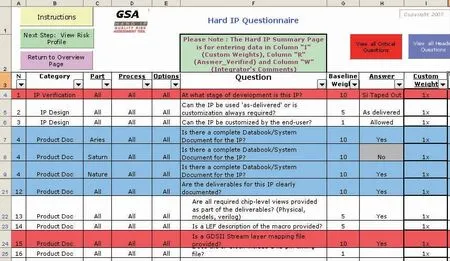

美国航天局和欧洲航天局均非常重视IP核的应用,规定航天器用IP核需要具备一定的成熟度。ESA在航天技术发展路线图中规划了IP核的研发及IP库的建设,ESA通过发布IP、建立IP高层次模型、构建虚拟系统原型等工作建立了开放式统一SoC开发平台,平台中的IP、软硬件设计资源向欧洲各国宇航机构和公司开放使用。通过SoC开发平台,统一了欧洲宇航SoC等复杂器件的核心处理器、接口模块、体系结构等技术方案。国外一些商用IP核信息提供商,例如Cadence的Chip Estimate网站和法国的Design&Reuse网站也具备了上述IP核库的部分特征,也能够提供IP核信息的集中检索服务。此外Design&Reuse还提供IP核评估服务,而Chip Estimate则能够提供基于IP设计的系统级工具服务。2015年全球半导体联盟(Global Semiconductor Alliance,GSA)发布了硬IP质量风险评估工具,也是对IP核的可复用性提出一些问题,并赋以分值,从而实现IP核的量化评估,图5为全球半导体联盟开发的硬IP质量评估工具截图。

图5 全球半导体联盟开发的硬IP质量评估工具

在国内军品IP核标准方面,军用IP核标准的研究工作在国家“十一五”和“十二五”期间得到了预研项目的大力支持。目前形成的《军用数字硬IP核交付项标准》等9项IP核标准,对数字软/硬IP核以及模拟、混合信号/射频IP核的交付内容进行了凝练,对IP核文档结构进行了规范,对IP核的质量做出了规定。这些标准充分考虑了军用IP核高可靠性要求的特点,在交付项、文档撰写及质量评价方面都有所体现。总体来说,国外对IP核质量评测研究较早,并且制订了IP核质量评估标准QIP,对于IP核的质量评估大多都是基于QIP来完成的。对宇航IP核需求较高的机构,如欧洲航天局,会制定自己的IP核设计标准[8]。

2.4 微系统宇航应用可靠性保证技术逐步实现规范化、体系化

2.4.1 可靠性保证标准

在国外相关标准方面,2014年欧洲ESCC提出了生产工艺能力认可的鉴定方式,ESCC 25600《生产过程能力认可要求》中提出了生产过程能力认可的通用要求、流程和方法,ESCC 2566000、ESCC 2566001等子标准明确了混合集成电路生产过程能力认可的详细要求,包括生产厂评估、能力域定义、能力域评估和能力域验证及批准4个方面,但尚未形成专门针对SiP器件的可靠性保证标准。

在关键结构的可靠性评价方面,随着基于TSV的堆叠形式变得更加普遍,更加复杂的器件堆叠形式使得相关测试试验更加困难。JEP 158“硅通孔(TSV)3D叠层芯片:可靠性的相互作用的识别、评估和理解”标准中,给出了采用硅通孔的三维芯片叠层结构中关键结构的主要失效模式,并给出了可靠性评价方法,为了对包含三维叠层芯片的整个器件开展保证工作,还需要参照JEP 150或者其他类似保证方法。

MIL-PRF-38535对传统的密封型Q级和V级、非气密性N级和Y级进行了规定。考虑到新型器件封装技术的复杂性,现有的MIL-PRF-38535可能不再适用,因此,为了将新技术纳入QML体系,美国国防后勤局建立了一种新规格——先进技术微电路(Advanced Technology Microcircuits,ATM),ATM器件主要包括倒装2.5D和3D封装、系统级封装和多芯片组件等,MIL-PRF-ATM主要采用PIDTP流程进入到整个集成电路制造过程中,PIDTP流程针对Y级倒装结构并已经成功应用于MIL-PRF-38535 PIDTP要求,QML-Y级认证是陶瓷非气密性封装倒装芯片质量和可靠性的最高等级。

在国内相关标准中,GJB 2438混合集成电路通用规范和GJB 597半导体集成电路通用规范等标准对集成电路的质量保证做出了规定和要求,包括质量保证大纲制定、通用性能验证和通用设计与结构准则等,但是相关要求、准则没有对SiP器件进行规定,尤其是SiP器件所采用的先进封装与互连工艺等,导致这些标准规范无法适用。此外,由于SiP器件具有小批量、高价值等特点,传统的标准中规定的质量一致性检验和鉴定检验试验项目较多,试验样品数量要求多,导致试验成本大大增加。

为了将宇航用微系统保证工作重心前移,中国空间技术研究院通过多年微系统质量保证工程实践,提出通过微系统工艺能力保证和微系统产品保证两个方面开展保证工作,降低在鉴定或认定阶段的样品消耗,为宇航用微系统保证工作降本增效。其中,微系统工艺能力保证主要针对微系统生产线的工艺过程,包括工艺能力认可和工艺能力维持两个部分。微系统产品保证主要针对在已经通过微系统工艺能力认可的生产线上生产的具体微系统产品,主要包括需求分析、设计保证、评估及验证、鉴定、装机产品质量保证5项主要工作内容,涵盖方案论证、方案设计、初样研制、正样研制等内容。

2.4.2 微系统宇航应用可靠性评价研究

中国空间技术研究院于2014年起关注微系统宇航应用可靠性评价技术研究工作,经过多年的工程实践,提出宇航微系统全寿命周期保证技术,统筹宇航微系统产品规划,从微系统产品需求定义和评价阶段入手,加强研制过程保证和生产制造过程控制,提升IP复用率和成熟度,确保安全性,建立了包括一个核心流程、一套技术体系、一套方法工具、一组专利技术的微系统产品保证方法,经保证的微系统已广泛用于空间站、遥感、导航、通信等多个型号领域。

北京轩宇空间科技公司基于型号需求自主研发了一系列抗辐射宇航级SoC、SiP产品,其中,SoC2008抗辐射控制器、SoC2012多核抗辐射控制器、SiP2113、SiP2115抗辐射计算机模块以及SiP7116太阳敏感模块已经应用于北斗导航的小型化长寿命星敏感器、微小卫星综合电子单元等产品。当前北京轩宇空间科技公司正在研发以SoC2020和SiP6117为代表的下一代异构多核智能处理模块,通过可编程、神经网络加速等新技术应用,可满足未来5~10年先进航天器应用需求。

中国空间技术研究院西安空间无线电技术研究所已有天线控制SiP、信号处理回放SiP等多款宇航产品实现型号应用,目前正规划论证基于40 nm抗辐射加固工艺和多芯片复杂封装工艺,实现射频、中频和数模混合的一体SiP产品,高可靠、小型化的满足卫星有效载荷的高性能数字处理需求。

3 微系统宇航应用面临的技术挑战

3.1 微系统宇航应用需求

尽管微系统在民用领域广泛应用,代表了先进技术水平,但是在宇航领域应用前,考虑到可靠性和空间环境适应性问题,不能直接进行宇航应用,必须进行全面的测试试验等评估保证工作,摸清可靠性数据以支撑宇航装备选用。分析未来宇航装备对于微系统的应用需求主要体现在以下5个方面。

1)多元功能异质、异构集成:宇航微系统功能和性能需求不断提升,通过智能化算法和架构技术提高系统效率,高性能抗辐照星载控制器SoC、抗辐照高能效智能异构阵列SoC、星载抗辐射计算机SiP模块等高性能产品进一步实现宇航电子系统的功能集成化[10]。此外,传统信号处理器件叠加射频功能、光电模块、微机电系统传感模块,甚至同时叠加多种功能模块的需求越来越迫切。

2)具备良好散热的微小型化:由于航天器在空间环境中能源供给和散热条件有限,宇航微系统设计应充分考虑器件功耗、封装散热能力,在功能性能、可靠性、散热等满足要求的前提下尽量选择小型化封装[11]。

3)工作温度范围:微系统在空间环境温度的变化会影响元器件的性能参数,进而对元器件的正常工作产生影响,需要对航天器用微系统的温度特性提出明确要求。一般而言,宇航级元器件的工作温度范围为-55~125℃,考虑到微系统的功能、封装复杂性、低温对于微系统的性能和可靠性影响较小、高温影响较大等特点,可适当降低对于微系统的工作上限范围,至少满足工作温度-55~105℃。

4)优异的抗辐照特性:空间辐照环境下,宇宙射线和带电粒子会引发微处理器产生总剂量辐照效应、单粒子翻转效应及单粒子闩锁(Single Event Latchup,SEL)效应。为了确保航天器用微系统的高可靠应用,有必要提出抗辐照能力要求。应用于高轨、高可靠卫星应用的微系统产品,抗辐照能力最低应满足电离总剂量辐照能力不小于100 krad(Si),SEL阈值不小于75 MeV·cm2/mg,单粒子翻转错误率不大于1×10-10次/d·bit;面向低成本、小卫星应用的产品抗辐照能力最低应满足电离总剂量辐照能力不小于10 krad(Si),SEL阈值不小于75 MeV·cm2/mg。

5)高可靠性、长寿命要求:当前我国航天器在轨工作寿命一般在10年以下。随着未来高价值、系统组网航天器的快速发展,航天器在轨工作寿命一般要求大于15年。这要求电子系统核心器件必须满足大于15年的工作寿命要求。

3.2 面临的技术挑战

新型微系统技术在宇航电子产品中的应用快速增长,各单位近年来快速发展微系统产品技术,研发了各类微系统电子产品。预计未来航天器对微系统产品年需求每年呈现30%以上的增长,在促进宇航电子系统微小型化的同时,还需要保证微系统技术的可靠应用。

3.2.1 先进架构和智能化算法带来功耗增加和评测难度增大

1)先进算法带来功耗不断增加

先进架构和先进算法带来功能密度的不断提升,造成了微系统功耗不断增加。由于在宇航应用条件下受到在轨散热措施的限制,微系统的功耗也受到严格限制,需要在算法复杂度提升的同时充分考虑低功耗设计问题,降低微系统器件的功耗。

2)AI等新型算法的可靠性成为关注要点

AI微系统将逐步应用于航天器深空探测、智能遥感等领域。目前国内针对航天器用AI器件已处于研发阶段,但国内针对其可靠性评价的方法尚未开展研究,有必要结合航天器的实际应用特点,研究AI等新型算法在空间复杂环境、无人值守、系统高可靠等条件下的应用可靠性,促进AI技术的宇航应用。

3.2.2 复杂封装结构带来热学、力学可靠性以及电学可靠性的全方位挑战

1)散热问题

由于先进封装密度不断提高,外形尺寸不断缩小,导致电子器件的工作温度过高,性能显著下降,热学问题越来越受关注。先进封装器件往往结构更加复杂,一般可能会包括微凸点、陶瓷基板、硅转接板、TSV、RDL层等多种结构,由不同的材料通过封装工艺组合而成,当温度发生变化或器件内部温度分布不均时,材料间热膨胀系数的差异会造成材料间失配,导致器件失效。

2)力学可靠性问题

针对2.5D/3D封装,在服役过程中会遇到振动、冲击的作用,使PCB或基板发生较大的动态弯曲变形,在封装内引起较高的应力。航天电子设备将在更恶劣的环境下工作,恶劣的振动和冲击环境会使封装发生较大的动态变形,导致更严重的交变应力和应变,存在BGA焊球开裂、TSV硅片翘曲、RDL层分层等可靠性风险[12]。

3)三维设计电磁兼容问题

高速互连是信号不完整的直接根源,主要表现在两个方面:第一,三维堆叠的基板结构不一致,要对不同的基板综合进行互连设计,同时还要综合不同通道之间的互连设计;第二,由于电磁场是在空间中传播,三维传输电路在空间中堆叠交错布设,射频信号传输中势必造成互相干扰。电磁兼容问题是三维互连设计必然要面临的问题,其复杂性远远超过二维平面传输结构。

3.2.3 宇航用IP评测的标准、工具和方法尚不完善

1)目前针对宇航用高可靠IP核方面的相关标准尚处于空白状态[13],需要针对航天领域在环境适应性、安全性、降额、高可靠性等方面的应用需求,研究制定相关航天器用可靠性IP核交付项标准和评测标准[14]。

2)目前针对IP核评测的方法和工具尚不健全,需要开发专用工具对IP核的安全性、抗辐射能力、功能和性能完备性进行评价,以满足宇航领域高可靠集成应用需求。

3.2.4 芯粒宇航应用的软硬件生态环境亟待建立

1)芯粒通用性与优化

通用芯粒的基础结构有利于通用基板的实现,方便任意组合的芯片的快速集成;而通用性可能制约性能、成本、功率或其他重要因素的权衡。因此,如何在通用性和优化之间取得有效的平衡是通用芯粒的设计挑战。目前,各大厂商都在积极定义自己的接口协议,以实现小范围内的通用化设计。

2)功能结构划分

对于一个给定的系统设计,有多种构架组合实现方案。例如前文介绍的AMD的前两代EPYCTM处理器展示了两种不同的方法,在成本、性能、灵活性、工程实现和满足不同市场需求方面具有不同的优势。因此,急需开展架构性能与成本的评估方法研究[15-16]。

3)全周期可靠性评价

芯粒的构建需要一个高效的产业生态系统的支撑,其中包括IP、已知好芯片、联合仿真平台、封装平台等。而在这个全产业链的各个环节都存在知识产权侵犯、设计思路窃取等安全问题[17],同时大规模多芯片混合封装器件的高可靠应用保证技术尚不成熟,因此芯粒产品生产和保证存在安全可靠风险。

3.2.5 提质增效是微系统宇航应用可靠性保证的重点目标

由于微系统器件样本量小、价格昂贵,传统的质量保证试验与评价技术周期较长、成本较高,形成高效率、低成本的微系统器件保证方法是当前面临的重要挑战之一,尤其是针对宇航应用环境,需要在深入研究失效机理、失效激发方法、可靠性评价方法等的基础上,研究适用于宇航用微系统器件的质量保证方法,并形成保证标准及体系。

由于微系统器件种类丰富、结构复杂,新型工艺和新型结构带来了新的应用风险,但目前相比于传统器件积累数据量少、数据挖掘不充分,合理进行微系统器件质量保证过程中的数据处理与分析是关键技术挑战之一。

4 宇航微系统未来发展建议

目前航天器用高可靠性IP核方面的相关标准尚处于空白状态,需要针对航天领域在环境适应性、安全性、降额、高可靠性等方面的应用需求,研究制定相关航天器用可靠性IP核交付项标准和评测标准。

芯粒作为灵活异质、短周期、低成本的微系统解决思路,可预见未来将是高性能处理器的发展方向,因此,目前急需开展互联标准制定、复杂封装工艺、联合仿真工具、IP库及业态等关键技术的预先研究和攻关储备。与此同时,芯粒技术的发展和成熟更需要一个新生态的培育,用户方、生产方、质量保证方共策合力,提早谋划,尽早实现芯粒技术的宇航高可靠产品化。

AI微系统将逐步应用于航天器深空探测、智能遥感等领域。目前国内针对航天器用AI器件已处于研发阶段,但国内针对其可靠性评价方法尚未开展研究,有必要结合航天器的实际应用特点,研究AI等新型算法在空间复杂环境、无人值守、系统高可靠等条件下的应用可靠性,促进AI技术的宇航应用。

先进封装产品结构复杂,且宇航用军用及航天用环境与普通的商用环境相比,条件更加严苛,尤其是对扇出型晶圆级封装这种新型复杂结构带来了更大的考验,应尽快建立相应的可靠性评价手段及标准,以期更好、更可靠地应用先进封装电子产品。

由于微系统器件组成复杂、技术先进,宇航应用数据积累较少,目前针对微系统器件尚未形成统一的保证要求,国内外相关机构均在积极探索针对性保证方法。在后续工作中,需针对新型互连封装结构开展失效机理研究,明确失效模式和失效激发应力,形成相关试验方法,尤其是针对宇航应用环境的真空、辐射、极端温度等特殊环境应力,制定满足宇航应用要求的质量保证试验与评价方法。

5 结论

本文从分析宇航微系统发展现状出发,分析了宇航领域对微系统的性能和功能、环境适应性等的要求,围绕IP核、芯粒、设计方法、封装技术、质量保证及标准等微系统关键技术最新研究进展及挑战进行分析总结,结合宇航应用现状给出了微系统应用可靠性后续发展建议。