本安电路电容放电模型与仿真分析*

2021-11-02赵永红

赵永红

(1. 中国煤炭科工集团太原研究院有限公司,山西 太原 030006;2. 煤矿采掘机械装备国家工程实验室,山西 太原 030006)

为了提高本安设备的工作性能,电路设计人员往往需要在电路中设计一定数量的大电容元件,而这些电容元件会存储较大能量,当电路发生故障时,大电容就会释放能量产生火花放电现象[1-3]. 按照GB3836.4规定,当电容值超出了标准允许值,或者火花放电能量超出规定的阈值(如:I类设备525 μJ[4])后,产生的放电火花会引燃瓦斯发生爆炸危险,导致设计的电路不满足本安防爆要求[5]. 因此,对于电容电路来说,如何最大限度得消除电容电路放电火花或降低放电火花能量,并对所采用方法的有效性进行便捷高效的验证是研究本质安全电路的重要内容.

目前,国内很多学者针对电容放电能量抑制方法及放电特性进行了研究,张刚[6]给出了抑制电容放电能量的多种方法,但属于指导性的,没有进一步分析影响程度;徐直[7]对简单电路放电特性进行了分析,但未建立电路模型;于月森等[8,9]对复合电路数学模型进行了推导,模型仅考虑了电容、电感自身参数,未考虑电路元件参数、连接线路、开关接点等实际情况. 在此基础上,本文通过分析影响电容放电能力因素,结合电容放电实际电路,建立了基于MATLAB的电容等效电路模型[10-13],并采用不同的放电形式对所建模型的放电过程进行仿真,最后通过IEC火花试验实验[14-16]验证了模型的正确性,实现了利用等效电路模型评定容性电路[17,18]本安性能的可行性.

1 电容放电能量影响因素及抑制方法

1.1 电容放电能量影响因素

电容储存能量的大小决定了爆炸危险性程度的高低. 稳态时,储存能量公式为

(1)

由此可见,影响火花放电能量的主要因素是电容值和电容端电压. 为了满足本安电路的防爆要求,可重点考虑可降低电容值和电容端电压的方法.

1.2 电容放电能量抑制方法

抑制电容放电能量最常用的方法有等效电容法(串联电阻)和降低电容端电压两种. 等效电容法是在电容支路中串联可靠电阻[19],使电容内阻增大,这样串联电阻和电容整体形成一个新的等效电容组件,该等效电容组件对外呈阻性,可大幅度降低电路的闭合放电能量. 降低电容端电压一般采取在电容两端并联合适的双重化稳压二极管或在本安输出的关联设备与所连接的本安设备之间加双重化过流过压保护电路等方法.

上述两种方法均是针对理想状态下纯电容电路而言,然而,实际电路中还包括等效串联电感、回路中的连接导线和开关元件等,这些元件参数直接影响电路本安性能. 因此,直接应用上述方法与实际电路存在较大偏差,用其评定实际电容电路是不准确的. 本文通过模拟和试验结合的方法,研究了等效电容法及电容端电压变化对电容放电能量的影响,并建立了仿真模型和数学模型,能够方便准确地评定出等效电容法和降低端电压法对电容放电能量的影响.

2 电容放电测试电路及仿真模型

2.1 电容放电测试电路

实验室电容放电测试电路系统一般包括直流稳压电源、电容、串联电阻、负载电阻和数字示波器.

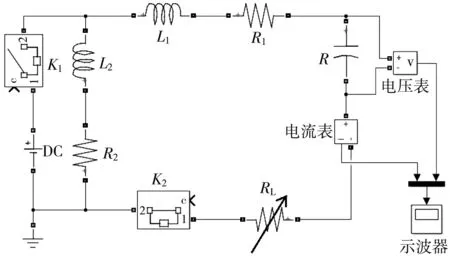

本次实验电容放电测试电路如图 1 所示.

图 1 电容放电实际测试电路

其中,直流稳压电源:0 V~50 V 内连续可调,精度 0.1 V;固体钽电容:C=50 μF;串联电阻R:0 Ω~100 Ω可调,负载电阻RL和数字示波器(泰克). 测试时,先通过直流稳压稳流电源对钽电容C充电,充电完毕后通过瞬动开关K将电容的能量泄放,用示波器记录电容C放电时电流以及电容两端电压变化情况.

2.2 电容放电仿真模型

根据实际本安电路的影响因素,建立电容放电电路等效模型时,不仅考虑上述因素,电路中还应该包括电容的等效串联电阻、等效串联电感、回路中的连接导线和开关元件等[20].

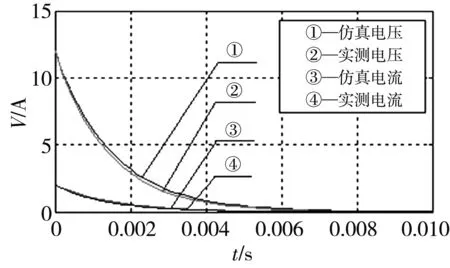

本次实验利用MATLAB建立的电容放电电路等效模型如图 2 所示. 其中,钽电容:C=50 μF,钽电容的等效串联电阻为R1;引线电阻:R2=1 mΩ;串联电阻RL:0 Ω~100 Ω可调,钽电容的等效串联电感为L1;采用 LCR 测试仪测得钽电容的等效串联电阻、等效串联电感和引线的电感值分别为290 mΩ、0.75 μH 和 34.2 nH.

图 2 电容放电电路等效模型

3 电容放电测试分析

3.1 利用等效电容法

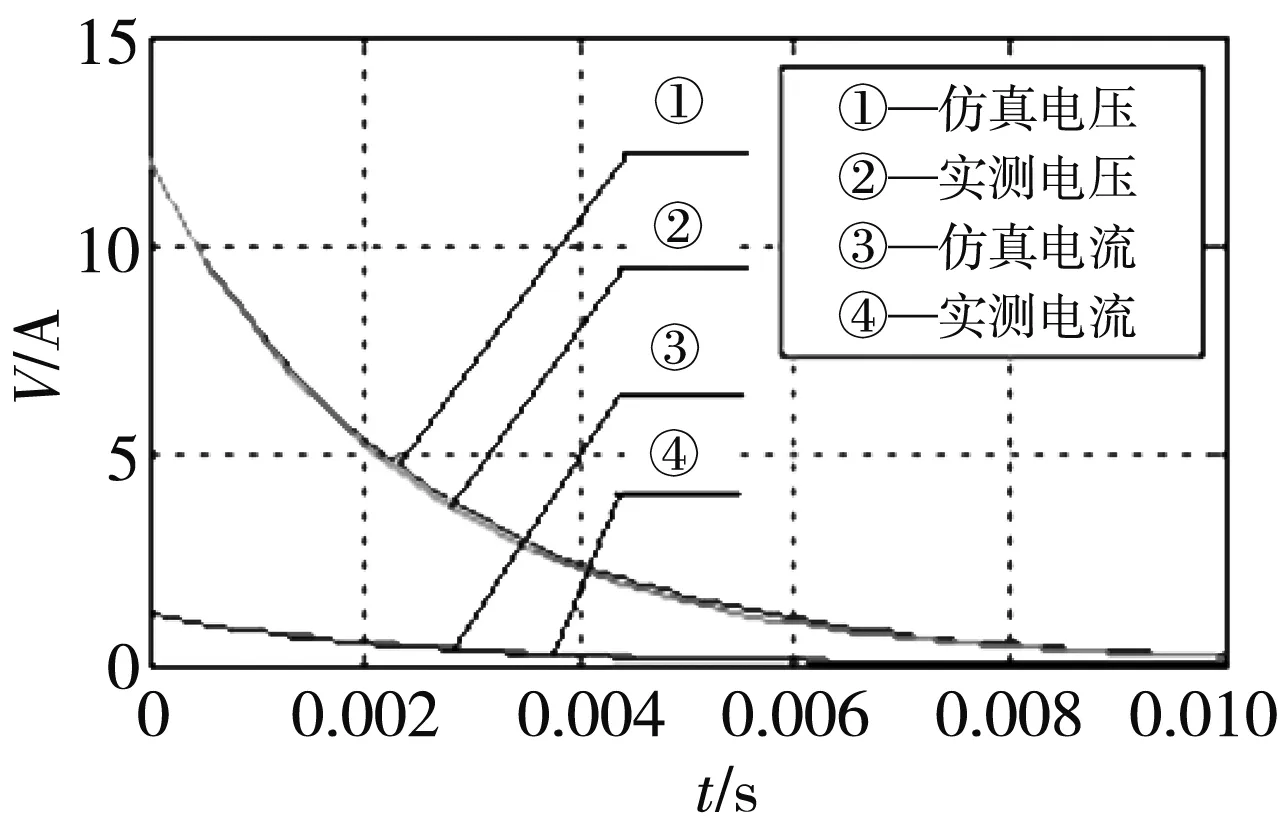

设端电压V1=12 V不变,改变电容串联电阻RL值分别为10 Ω、30 Ω、50 Ω,在测试电路输出端用导线直接短接,采用示波器测试回路中的电流以及电容两端电压变化曲线与仿真电路的结果对比图如图 3 所示.

(a) 串联电阻R=10 Ω

(b) 串联电阻R=30 Ω

(c) 串联电阻R=50 Ω

从图 3 中可以看出,当串联电阻分别为 10 Ω、30 Ω和50 Ω时,放电时间分别约为3 ms、8 ms和10 ms以上. 随着电容串联的电阻的减小,电压电流变化越来越快,放电电流幅值越来越大,表明放电时间越来越短,放电能量越来越集中,引燃爆炸性气体的可能性越来越大.

3.2 利用降低电容端电压法

设串联电阻RL=30 Ω不变,改变其充电电压U的值分别为5 V、10 V、15 V,在测试电路中改变输出端用导线直接短接,采用示波器测试回路中的电流以及电容两端电压变化曲线与仿真电路的结果对比图如图 4 所示.

(a) 端电压U=5 V

(b) 端电压U=10 V

(c) 端电压U=15 V

从图 4 中可以看出,不同放电电压下,电容放电时间基本相同,放电全部完成时间均为8 ms,端电压变化对放电时间无显著影响,所以可以得出放电电压越大,相同时间内放电能量越集中,爆炸危险性越高.

另外从图 3、图 4 中可见,所建立的等效电路模型的仿真测试曲线与实际测试电路曲线均保持一致,证明了建立的电容放电模型与实际电路的相符性.

3.3 电容放电模型仿真分析

通过上述曲线可以看出,电压、电流曲线与放电时间的乘积就是电容放电的能量. 为了更加准确方便评定等效电容法和降低端电压法对电容放电能量的影响,实现定性评价转为定量评价,根据图 2 建立的等效模型可得如下数学模型

(2)

进一步推得火花放电能量W为

式中:U0为电容两端初始电压;t为时间;c为常数.

应用MATLAB软件对等效电容法、调整电容两端电压两种情况的电容放电电流、放电电压、放电能量特性进行仿真,分别得到:

1)在固定电容为50 μF,保持电容端电压 12 V 不变的情况下,放电能量随串联电阻及时间变化的三维仿真曲线如图 5 所示.

从图 5 可以看出,在同一电容,固定端电压条件下:①当串联电阻从0 Ω~100 Ω连续变化时,相同放电时间内放电能量随着电阻的增大而减小,且电容放电时间也在增加,说明串联电阻对放电能量和放电速度有明显的抑制作用. ②随着串联电阻的增加,总的放电能量随着串联电阻的增加而减小,说明整个放电过程中串联电阻消耗了一定的能量. ③本曲线绘制了电容串联不同电阻值与放电能量的对应关系,将串联电阻与放电能量数量化,较为精确、定量地给出了在此条件下串联电阻与放电能量数值对应关系.

图 5 固定电容值和端电压下不同电阻

2)在固定电容为50 μF,保持串联电阻30 Ω不变的情况下,放电能量随端电压及时间变化的三维仿真曲线如图 6 所示.

图 6 固定电容值和串联电阻下不同端电压对应的放电能量曲线

从图 6 中可以看出,在串联固定电阻情况下:①当端电压从0 V~15 V连续变化时,相同放电时间条件下端电压越大放电能量越大,且随着电压的增加,放电能量增速明显加大. ②放电时间随端电压的增加而不断增加. ③本曲线绘制了端电压与放电能量的对应关系,将端电压与放电能量数量化,较为精确、定量地给出了在此条件下端电压与放电能量数值对应关系.

以上模型是结合实际使用情况,综合考虑了电路中其他元件的参数,包括连接线路参数,电容内部电感、电阻等,相比理想状态下的其他纯电容电路分析方法,能够较真实地反应实际应用情况,按此模型分析得出的数据比较准确.

3.4 火花试验验证

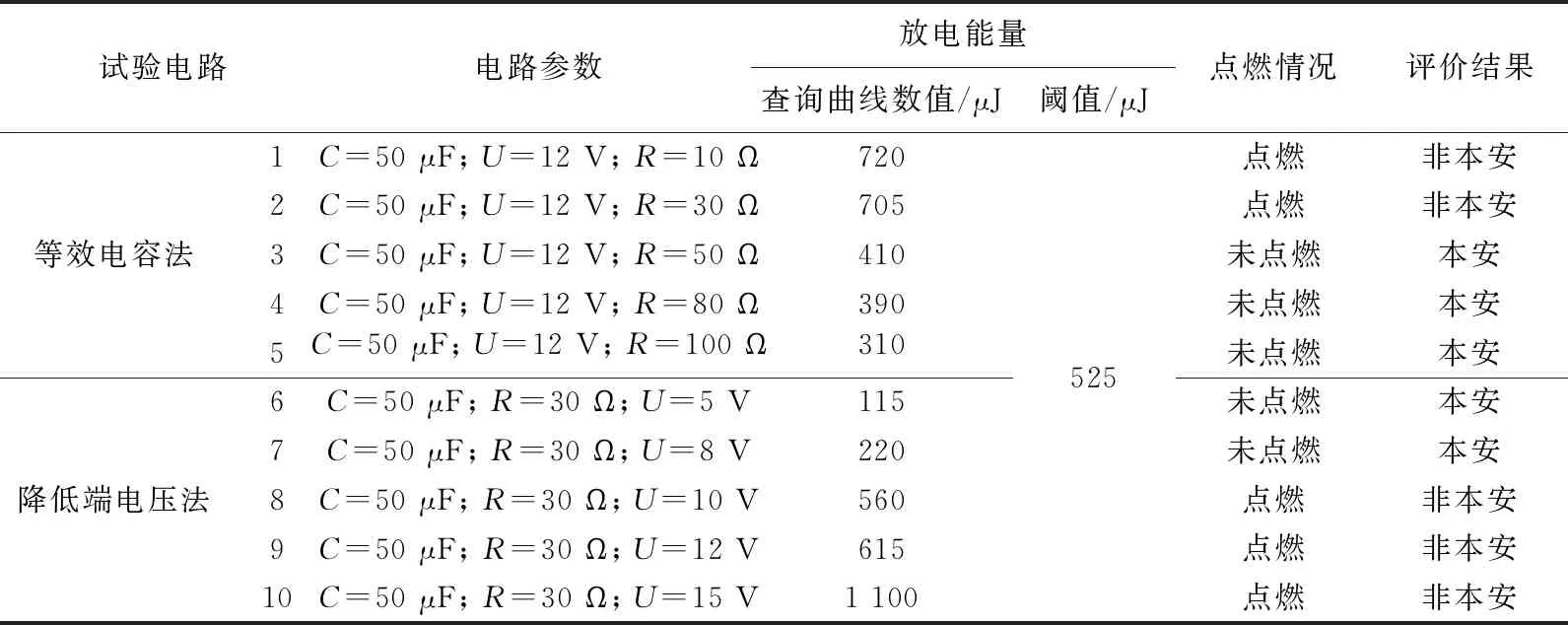

为了验证所建立的本安电路电容放电模型的可行性,设定了2组共6种电路参数,并对其采用IEC火花试验装置进行火花点燃试验,电路参数及点燃情况见表1.

表1 电容电路火花点燃情况

通过对选取的电路参数进行评价比较,分别查询利用建立的仿真模型绘制的放电能量曲线对应的放电能量数值,当数值未超过花火试验装置点燃能量阈值时,未发生火花点燃情况,可评定为本安电路;当数值超过花火试验装置点燃能量阈值时,均发生了火花点燃情况,电路不能评定为本安电路. 因此说明仿真模型评价结果与火花点燃试验评价结果一致,证明了该方法的可行性.

4 结 论

1) 通过实验测试电路与仿真电路的测试结果对比证明,利用MATLAB建立的电容放电电路等效模型与实际电路放电情况基本一致;在此基础上建立了对应的电容电路数学模型,并用MATLAB软件对该模型进行仿真,分别生成了采用等效电容法和降低端电压法两种情况下的放电能量曲线,然后通过IEC火花试验装置对电容放电电路进行火花点燃试验,发现利用本文建立的仿真模型评价结果与火花点燃试验评价结果一致,证明了该模型的正确性和可行性.

2) 等效电容法分析测试结果表明,相同放电时间内放电能量随着串联电阻的增大而减小,且电容放电时间也在增加,串联电阻对放电能量和放电速度有明显的抑制作用;随着串联电阻的增加,总的放电能量随着串联电阻的增加而减小,整个放电过程中串联电阻消耗了一定的能量.

3) 降低端电压法分析测试结果表明,相同放电时间条件下,端电压越大放电能量越大,且随着电压的增加,放电能量增速明显加大;放电时间随端电压的增加而不断增加.

4) 设计人员可以在等效电容值不在标准要求的范围内时,或者没有专用的本安电路火花试验装置进行验证时,通过本方法对所设计电路中电容放电能量进行模拟仿真,验证设计的电路是否符合本质安全电路要求,从而节约开发验证成本,减少反复,缩短开发周期. 但是需要特别说明的是设计的产品在进行防爆认证检验时会增加1.5倍安全系数,这一点设计时需予以考虑.