基于碳化硅衬底的宽禁带半导体外延

2021-10-27开翠红杨德仁皮孝东1

开翠红,王 蓉,杨德仁,皮孝东1,

(1.浙江大学材料科学与工程学院,硅材料国家重点实验室, 杭州 310027;2.浙江大学杭州国际科创中心, 杭州 311200)

0 引 言

以碳化硅(SiC)、氮化镓(GaN)为代表的第三代半导体材料,由于其宽带隙、高电子饱和漂移速度、高热导率、大击穿场强等优势,是制备高功率密度、高频率、低损耗电子器件的理想材料[1-2]。其中,SiC功率器件具有能量密度高、能耗小、体积小的优势,在新能源汽车、光伏、轨道交通、大数据等领域有广阔的应用前景。GaN射频器件具有高频、高功率、较宽频带、低功耗、小尺寸的优势,在5G 通信、物联网、军用雷达等领域有广泛的应用。此外,GaN基功率器件已广泛应用到了低压领域。除SiC、GaN以外,近年来新兴的氧化镓(Ga2O3)材料有望与现有的SiC及GaN技术形成技术互补,在低频、高压领域具有潜在的应用前景[3]。

宽禁带半导体在高温、高压、高功率场景中有应用优势,而这些场景对器件的散热性能以及可靠性提出了严峻考验。SiC衬底具有高热导率、高化学稳定性、耐高温等优异性能,基于其制备的第三代半导体器件拥有更高的散热性能,能够提升器件的性能与可靠性,也有利于减小系统散热模块体积。SiC衬底是发展较成熟的第三代半导体材料,目前已实现商业化。国际上,主流产品从4英寸(1英寸=2.54 cm)向6英寸转化,8英寸衬底已经被成功研发出来,代表公司包括Cree、DowCorning、SiCrystal、Ⅱ-Ⅵ、Norstel等。国内SiC产业起步较晚,目前主流产品为4英寸,6英寸衬底目前已在市场上推出。主要企业包括天岳、天科合达等。SiC衬底的晶体质量不断提升,尺寸逐渐增大,成本不断降低,使得基于SiC衬底的宽禁带半导体电子器件的市场占有率逐年提升。而在SiC衬底上制备高质量外延材料是提高器件性能及可靠性,推动第三代半导体在生产生活中的应用的关键。

本文主要讲述基于SiC衬底的宽禁带半导体GaN、SiC、Ga2O3等的外延生长研究,分别介绍其存在的问题和相应的解决方案,并展望了基于SiC衬底的宽禁带半导体外延的发展前景。

1 基于SiC衬底的GaN异质外延

Ⅲ族氮化物的禁带宽度在0.7~6.2 eV范围内连续可调,且具有高电子饱和漂移速度、耐高温、大功率密度等优点,使得其在光电子和微电子领域具有广阔的应用前景[4-6]。由于同质衬底的研发目前尚处于起步阶段,其质量与尺寸仍需进一步提高,且价格昂贵,所以目前Ⅲ族氮化物多通过异质外延获得。异质外延的常用衬底包括Si、蓝宝石和SiC,其基本参数如表1所示。其中,蓝宝石衬底热导率低、解理困难,主要应用在LED产业。在微电子领域所用衬底包括Si和SiC,GaN-on-Si主要应用在功率器件上,目前在中低压领域占有一定市场,由于Si与GaN间大的晶格失配和热失配限制材料质量,Si衬底GaN基器件难以实现高压环境应用。SiC衬底与GaN的晶格失配及热失配较小,且具有较高的击穿场强及热导率,能够外延获得高质量GaN。但是目前其成本相对Si较高,主要应用在对材料质量要求更高的射频器件领域,如电信和军事领域,也是GaN射频市场的主导技术。根据国际知名行业咨询机构 Yole 的统计, GaN基射频芯片的市场份额在5年内将达20亿美元。随着GaN-on-SiC成本不断降低,器件性能和可靠性不断提升,GaN-on-SiC将有望与GaN-on-Si市场竞争[7]。

表1 GaN及其常用衬底(蓝宝石、Si、SiC)的基本参数[8-9]Table 1 Basic parameters of GaN and its commonly used substrates including sapphire, Si, SiC[8-9]

1.1 SiC衬底外延GaN存在的问题

目前在SiC衬底上外延GaN存在以下几点技术难点:(1)衬底表面氧化层、亚表面损伤层、缺陷等影响GaN外延层的质量。(2)GaN在SiC衬底表面难以成核,由于Ga原子在SiC衬底表面浸润性差,直接在SiC衬底表面生长GaN生长速度慢、材料质量差。(3)衬底表面原子排布诱导GaN外延层中形成堆垛层错(BSFs),对于SiC衬底上外延GaN,衬底上有多种可能的原子排列次序,导致其上外延GaN层初始原子堆垛次序不统一,容易产生堆垛层错[10]。堆垛层错(SFs)沿着c轴引入内建电场,导致面内载流子分离以及器件漏电等问题出现[11-12];(4)晶格失配与热失配问题。SiC衬底与GaN晶格常数和热膨胀系数不同,使GaN层受到压应力,热膨胀系数差异导致生长完成后的降温过程中GaN薄膜受到张应力。应力与GaN带隙呈线性关系,每1 GPa双轴应力带来的带边峰的线性移动为(20±3) meV[13]。此外,应力的存在导致GaN外延层中产生了高密度的缺陷。

1.2 解决方案

1.2.1 SiC衬底表面处理

SiC衬底表面处理是SiC衬底外延GaN面临的重要问题之一。早期由于SiC衬底切磨抛工艺过程带来的划痕、亚损伤层、污染物残留等问题较多,研究者在外延之前采用湿法腐蚀降低衬底表面缺陷对GaN外延薄膜质量的影响。Lin等[14]在分子束外延(MBE)前,对SiC衬底在H2/He(1∶1)等离子体气氛中650 ℃处理90 min,随后通过MBE外延生长GaN。该课题组对比了SiC衬底和蓝宝石衬底上外延GaN的晶体质量与电学性质。如图1所示,SiC衬底上外延GaN电子迁移率与结晶质量均高于蓝宝石衬底外延[15]。然而由于GaN外延常用的金属有机化合物气相外延(MOCVD)多数不具备等离激元产生系统,上述方法在MOCVD中不适用。在MOCVD外延中,研究者通过稀释的HF缓冲液刻蚀[16-17]去除SiC衬底表面破坏层。此外,也有研究者采用湿法刻蚀与原位刻蚀结合的方式清理SiC衬底表面。Zhang等[18]在衬底清洗后,在MOCVD腔室中对衬底在H2和NH3混合气氛中进行高温退火处理,最终外延得到了高质量外延层。而Koleske等[19]将衬底清洗后放入MOCVD腔室中在H2气氛进行高温热退火,提高了衬底表面质量。随着SiC晶圆切磨抛工艺以及衬底封装工艺的进步,衬底表面质量得到改善。目前SiC衬底表面采取机械化学抛光的处理方式已做到基本无划痕,氮气氛围的封装工艺也可避免SiC表面与氧气的长时间接触,因此多数外延不再采用额外的化学腐蚀,而是直接采用原位高温H2或H2/NH3混合气体高温热处理的方式进行衬底处理[20-22]。

图1 蓝宝石衬底与SiC衬底上GaN外延薄膜的(a)电子迁移率;(b)(0002)面XRD θ-mode反射曲线[15]Fig.1 (a) Electron mobilities and (b) (0002) surface XRD θ-mode reflection curves of GaN grown on sapphire and SiC substrates[15]

1.2.2 外延生长调控

本节将介绍SiC衬底上外延生长高质量GaN 薄膜的研究进展。针对SiC衬底外延GaN存在的堆垛层错(SFs)缺陷问题、Ga原子浸润性差问题以及晶格失配与热失配问题等,综述引入缓冲层(包括AlN、AlGaN、AlN/GaN、SiNx等)、直接外延GaN、图形化衬底等方案对GaN薄膜的质量改善情况。

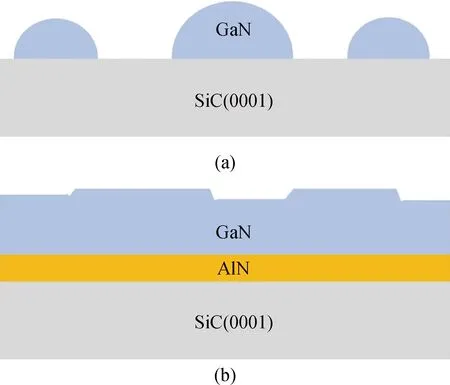

引入缓冲层是GaN外延生长中常用的改善外延层结晶质量的方法。引入AlN缓冲层能够有效改善SiC表面浸润层,调控应力,阻挡衬底缺陷向GaN外延层的延伸,从而改善GaN外延层质量。如图2所示,直接在SiC衬底表面外延生长GaN,由于两者间原子浸润性差,GaN在衬底表面为3D岛状生长,外延层受到的应力全部释放,只保留了降温过程中产生的张应力。引入AlN缓冲层可有效改善原子浸润性,使GaN外延层呈二维生长,缓冲压应力释放,GaN外延层仍然保持压应力状态,从而提升GaN外延层结晶质量[23]。

图2 (a)GaN/SiC, (b)GaN/AlN/SiC外延生长模式示意图Fig.2 Schematic diagram showing the epitaxial growth mode of (a) GaN/SiC and (b) GaN/AlN/SiC

采用AlN缓冲层方法是目前GaN-on-SiC的主流技术,AlN的生长参数对后续高质量GaN外延至关重要。从20世纪90年代以来,研究者们通过优化厚度、温度以及生长步骤等方法对AlN缓冲层进行了优化。在厚度调控方面,Tanaka等[24]的研究表明,表面粗糙度小、结晶质量好的超薄AlN缓冲层有利于降低GaN外延层中的位错密度。当AlN缓冲层厚度为1.5 nm时,GaN层中的位错密度低至107~108cm-2。之后,Ding等[25]提出AlN缓冲层太薄不利于降低GaN外延层中的位错密度。基于厚度为100 nm的AlN缓冲层,他们获得了高质量的GaN外延薄膜,其(002)和(102)XRD的半峰宽分别为184 arcsec 和 275 arcsec。在温度调控方面,Warren等[26]提出AlN缓冲层生长温度为500~1 050 ℃时得到的是多晶AlN层,不利于高质量GaN的获得,将生长温度提高至1 100 ℃以上可获得高质量的AlN单晶层,并有利于降低GaN外延层中的位错密度,他们获得0.5 μm GaN的位错密度约1×109cm-2。Koleske等[19]研究了AlN缓冲层生长温度对GaN层电学特性的影响,发现对于4H-和6H-SiC衬底,最优AlN缓冲层的最佳生长温度分别为980 ℃及1 080 ℃。在生长步骤方面,Cho等[27]提出采用两步生长法(温度分别为1 250 ℃及1 300 ℃)可优化AlN缓冲层表面形貌与结晶质量,有利于降低GaN外延层的应力与位错密度,他们最终获得的GaN位错密度为(6~9)×108cm-2。Li等[28]通过交替通入三甲基铝(TMA)/NH3的方式优化AlN缓冲层质量,外延获得GaN(厚度1.8 μm) XRD (002)半峰宽为167 arcsec,(102)面半峰宽为240 arcsec。尽管文献中关于AlN缓冲层优化的条件有所不同,但是可以得到结论:结晶质量好,表面形貌平滑的AlN缓冲层有利于优化GaN外延层质量。

除优化AlN缓冲层生长参数外,GaN外延生长优化也是获得高质量外延层的关键。关于AlN缓冲层上GaN外延模式:2003年,Einfeldt等[29]研究了AlN缓冲层上GaN外延生长模式,认为模式为层状与岛状混合生长。一年后,Moran 等[30]观察到GaN外延生长模式为岛状生长,位错产生于岛与岛合并的边缘以及继承自AlN层。之后,Cho等[31]研究发现,GaN在AlN缓冲层上呈岛状生长易产生SFs,调控生长参数以实现二维生长,能够抑制SFs缺陷的形成。他们在AlN/GaN界面插入Al组分逐渐减小的AlGaN缓冲层,以缓冲由于界面应力导致的三维岛状生长。通过调节AlGaN渐变层的Al组分与厚度,最终有效降低了GaN层中SFs的缺陷密度。目前,GaN-on-SiC已经产业化,Cree公司(3 μm)GaN-on-SiC产品(006)面XRD半峰宽<250 arcsec[32]。

虽然AlN缓冲层能够有效提高SiC表面浸润性,缓解SiC衬底与GaN之间应力,但是AlN缓冲层带来的热阻问题造成HEMT沟道温度增加,抑制器件峰值功率密度[33],此外AlN的宽带隙会阻挡电子输运,不利于SiC基GaN垂直器件的发展。因此,研究者们提出通过引入AlGaN缓冲层、优化直接外延GaN的生长条件等方式来获得高质量的GaN。对于AlGaN缓冲层,研究表明为改善SiC表面浸润性,AlGaN中Al组分须大于等于6%[34]。与AlN缓冲层相比, AlGaN缓冲层上GaN受到的应力较小,受界面驱动力影响其生长初期岛的形成被抑制,外延生长模式为台阶流生长。受AlGaN相分离问题的影响,GaN外延层易出现深槽型缺陷[29]。在SiC上直接外延GaN为三维岛状生长,易在表面产生六边形岛状起伏。2000年,Lahrèche等[35]提出了三步生长法直接外延GaN来提高材料质量:先生长薄的3D GaN (100~130 nm);再在NH3气氛中原位退火使表面变平滑;最后调整生长参数2D外延GaN,外延GaN XRD 摇摆曲线半峰宽(002)面107 arcsec,(105)面190 arcsec。尽管文献中通过调整外延参数能获得高结晶质量GaN,但是SiC衬底上直接外延的GaN受张应力影响,在外延厚度超过1 μm时易出现裂纹。2016年,Sun等[36]通过三甲基铝(TMAl)预处理的方式,在SiC与GaN界面形成AlGaN薄层,获得1.2 μm无裂纹GaN,其位错密度中螺位错密度为4.7×107cm-2,刃位错密度为1.4×109cm-2。2021年,Feng等[37]采用同样预通TMAl的方式,获得了2 μm厚无裂纹GaN, 其(002)和(102)XRD半峰宽均为180 arcsec。

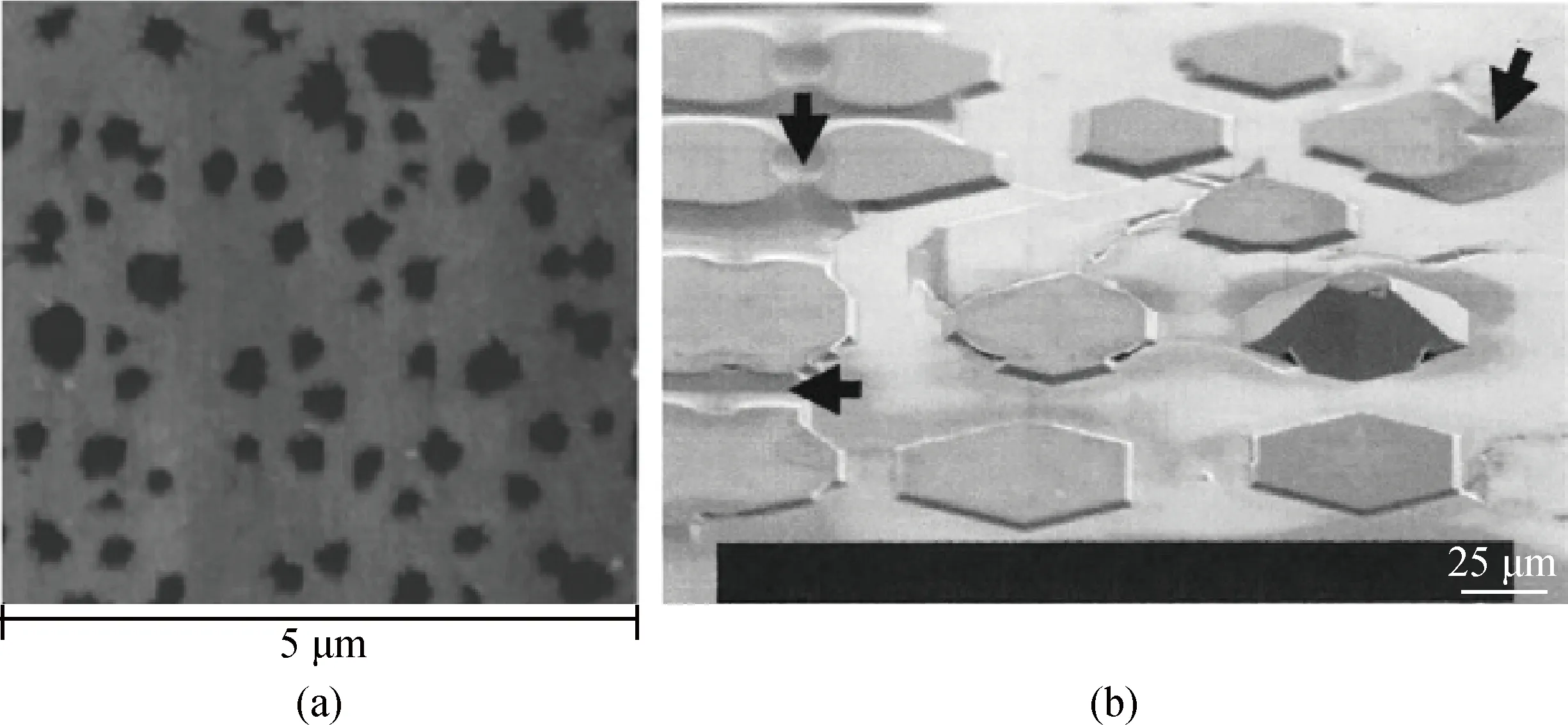

此外,也有研究者采用图形化衬底的方式在SiC衬底上外延GaN。2002年,Yun等[38]使用表面有孔洞的SiC衬底(见图3 (a))外延GaN,使GaN外延层中的位错密度降低了一个数量级(位错密度1×109cm-2)。同年,Neudeck等[39]用表面有mesa-pattern的SiC衬底(见图3 (b))外延GaN显著降低位错密度,但是表面出现由于岛合并导致的pit缺陷[40]。虽然该方法起到降低位错密度的作用,但是外延得到的GaN位错密度仍然较高,因此近年来少有相关报道。2013年,Song等[41-42]在SiC衬底外延GaN过程中原位引入SiNx缓冲层,有效提升了外延层结晶质量,外延GaN 的(002)XRD半峰宽161 arcsec,(102)面半峰宽为225 arcsec。2005年,Huang等[43]提出通过控制衬底斜切角的方法调控外延层的应力释放,证明有倾角SiC衬底有利于面内应力的释放。2021年,Su等[44]对比无倾角和4°倾角SiC衬底上HEMT器件性能,发现4°倾角衬底上器件性能更好。但是也有研究表明,有倾角SiC衬底上外延GaN缺陷和应力分布不均匀,易导致外延片裂纹产生[45-46]。目前,大部分GaN-on-SiC采用无倾角SiC衬底。

图3 (a)表面有孔洞的SiC衬底SEM照片[38];(b)表面有mesa-pattern的SiC衬底SEM照片[39]Fig.3 SEM images of (a) SiC substrate with holes on the surface[38] and (b) SiC substrate with mesa-pattern on the surface[39]

2 SiC同质外延

SiC材料在智能电网、光伏、电动汽车、工业电机、铁路交通等领域有广阔应用前景[47]。外延是制备SiC基器件的关键技术。常见的SiC同质外延生长技术有化学气相沉积技术(CVD)、液相外延技术(LPE)和MBE等。相比之下,CVD具有可以在较高生长速率下获得高质量外延层,可以对SiC外延层的厚度实现精确控制,并且能够可控实现SiC原位掺杂等多种优点,已成为SiC外延生长的主流技术,并得到了广泛应用[48]。在SiC的多型体中,由于4H-SiC的禁带宽度较大、载流子迁移率较高、掺杂剂离化能较低,是功率电子领域常用的一种材料[9]。在4H-SiC同质外延研究中,研究者们的关注重点集中在高质量厚膜外延、掺杂浓度控制、缺陷调控三个方面。

2.1 高质量SiC厚膜外延

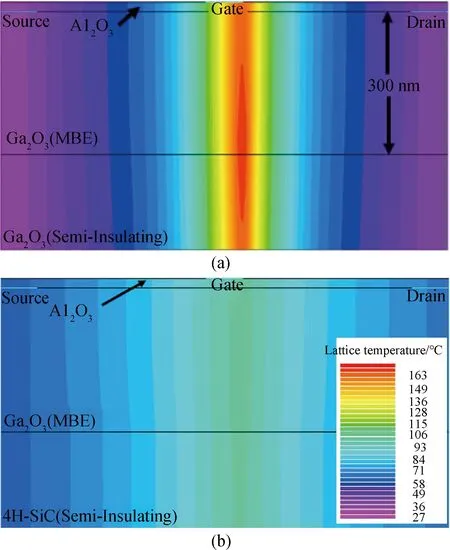

SiC功率器件中,在外延的SiC漂移层中平衡外延层厚度及掺杂浓度是获得高耐压器件的关键。表2中是典型SiC双极器件中击穿电压对漂移区掺杂浓度和厚度要求[49]。目前,SiC同质外延主要采用CVD法进行生长,通常采用H2作为载气,硅烷(SiH4)和丙烷(C3H8)作为Si源与C源。CVD法外延生长时间过长易造成腔体内状态不稳定,掉落物增多。因此,高质量厚膜SiC漂移层的外延生长需要开发高速外延生长方法。通过提高源流量的方式可将外延生长速度提高至10 μm/h以上。但是高的Si源流量易造成Si团簇的形成,这些Si团簇在衬底表面形成Si液滴,成为缺陷成核点,造成外延层表面形貌退化,降低结晶质量[50]。通过提高外延生长温度的方法,可有效提高外延生长速度[51-54]。Kordina等[51]提出了高温CVD生长SiC的方法,并在2 300 ℃下以500 μm/h的生长速度,获得了背景载流子浓度为6×1015cm-3的SiC薄膜。在生长气氛中引入Cl元素,可有效减小Si团簇的形成,并抑制高速外延情况下SiC表面形貌与结晶质量的退化。Crippa等[55]在外延过程中引入了HCl气体,在相同Si/H2比例下,由于Si液滴的形成被抑制,样品表面形貌显著改善,如图4所示。随后,他们经过工艺调整,将外延生长速率提高至112 μm/h[56-58]。除引入HCl以外,采用含Cl化合物,如SiCl4[59-60]、SiHCl3[61-62]、SiH3Cl[63]、CH3Cl[64-65]、SiCCl3H3[66-67]等作为Si源或C源均可有效提升外延生长速度,目前通常使用SiHCl3作为Si源,C2H4作为C源。此外,提高衬底转速、提高反应室压力等方式同样可以有效提高SiC的外延生长速度[68-71]。

图4 SiC外延薄膜的光学显微镜图片[55]。(a)Si/H2=0.1%;(b)Si/H2=0.1%含HClFig.4 Optical microscopic images of the SiC epitaxial film[55]. (a) Si/H2=0.1%; (b) Si/H2=0.1% with HCl

2.2 SiC外延层中的掺杂浓度控制

控制外延层的掺杂浓度对SiC功率器件的性能至关重要。外延层掺杂浓度与掺杂源流量、C/Si比、温度、反应室压强、生长速度等生长参数有关。Larkin等[72]提出点阵竞争理论来解释CVD外延SiC过程中的掺杂控制,他们认为,电子浓度与C/Si比成反比,而空穴浓度与C/Si比成正比。接下来,该作者证明,磷(P)、氮(N)掺杂在C面更容易并入,而铝(Al)、硼(B)掺杂更容易在Si面并入[73]。对于n型掺杂的调控,通常采用N作为掺杂元素,N的离化能低,容易实现100%离化,故n型掺杂较容易实现。高的掺杂源流量、反应室压力,低的生长温度、C/Si比有利于N原子并入[74]。生长速度对N原子并入的影响与SiC晶面有关,对于Si面,N并入效率随着生长速度增加而减小,而C面N原子并入效率与生长速度成正比[75]。对于p型掺杂,通常采用Al作为掺杂元素。Al的离化能约为230 meV,室温下无法实现完全电离[76]。只有当Al的浓度超过5×1020cm-3,达到简并掺杂时,Al才几乎完全电离[77]。为帮助理解Al原子在SiC中并入机理,Ferro等[78]提出表面空位诱导掺杂模型,认为Al并入主要由于SiC表面或者近表面瞬时形成的Si空位,提高Si空位的吸附稳定性或减少其分解时间有利于Al原子并入。目前,Cree公司生产的Si面SiC外延层中n型载流子浓度为5×1014~1×1019/cm3,p型载流子浓度为5×1014~1×1020/cm3[79]。

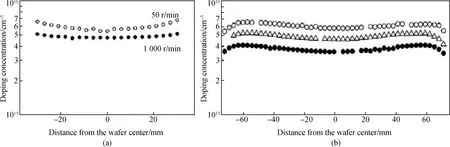

除掺杂浓度以外,外延层的掺杂均匀性是研究者们的另一关注重点。图5(a)展示了衬底转速对径向n型掺杂浓度均匀性的影响。可以看出,从衬底中心到边缘,掺杂浓度逐渐增加。提高衬底转速可有效提升载流子浓度分布的均匀性。图5(b)展示了生长速度对径向掺杂浓度均匀性影响,随着生长速度的升高,径向掺杂浓度均匀性降低[80]。合理的控制外延生长速度有利于掺杂浓度与均匀性的调控,然而SiC厚膜外延需要高的生长速度,因而在外延生长过程中,需要基于外延目的调控外延生长参数,最终获得符合要求的外延材料。

图5 (a)衬底转速和(b)生长速度45 μm/h(三角形),54 μm/h(空心圆),77 μm/h(实心圆)对径向掺杂浓度均匀性的影响[80]Fig.5 (a) Substrate rotation speed and (b) growth rate 45 μm/h (triangle), 54 μm/h (hollow circle), 77 μm/h (solid circle) influence on the uniformity of radial doping concentration[80]

2.3 SiC外延层中的缺陷调控

有效调控SiC外延层中的缺陷是确保SiC功率器件性能与可靠性的关键。SiC外延层中的缺陷主要分为层错、位错、表面缺陷及点缺陷。

图方向观察Shockley SFs堆垛次序示意图[81];(b)不同构型Frank-type SFs堆垛次序示意图[82]Fig.6 (a) Schematic diagram of the stacking sequence of Shockley SFs viewed from the direction (b) schematic diagram of the stacking sequence of Frank-type SFs with different configurations[82]

表3 室温下不同构型SFs对应的发光波长[82]Table 3 Corresponding emission wavelengths of different configurations of SFs at room temperature[82]

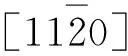

4H-SiC中位错包括螺位错(TSD)、刃位错(TED)、基平面位错(BPD)、微管(MP)等,可通过缺陷选择刻蚀观察到,图7为选择刻蚀后4H-SiC中位错的光学显微形貌图[92-93]。其中螺位错主要来自衬底螺位错向外延层蔓延[94],影响器件击穿电压,造成器件可靠性降低[95-96]。刃位错主要来自衬底刃位错的延伸[97],同时由于基平面位错向刃位错的转化,外延层中刃位错密度增加,刃位错对器件性能影响较小。微管缺陷目前已经可以得到很好的控制。基平面位错造成双极器件正向电压漂移,影响器件稳定性[98]。在晶体生长过程中基平面位错沿着(0001)面滑移,目前90%以上的基平面位错在SiC外延层与衬底界面转化为刃位错[99-100]。但是仍有部分BPD延伸至外延层,对器件性能带来致命影响[101]。将基平面位错转化为刃位错是SiC外延研究关注重点之一。Ohno等[102]研究了外延生长参数对基平面位错演变的影响,发现生长温度对基平面位错演变无影响,高C/Si比和低的生长速率有利于抑制衬底基平面位错向SiC外延层的传播。基平面位错向刃位错的转换与位错线和生长方向的夹角α相关,如图8所示,减小衬底倾斜角度,能够增加基平面位错与生长方向的夹角,减小刃位错与生长方向的夹角,从而增加基平面位错向刃位错的转换效率[99]。Myers-Ward等[103]在4°倾角SiC衬底上获得BPD转换效率≥97%的外延层。Wheeler等[98]发现低掺杂浓度n-SiC外延层有利于BPD向TED的转化,在n掺杂浓度<1016cm-3时BPD转换效率达到96%~99%。Zhang等[100]发现在熔融KOH中刻蚀后的SiC衬底上外延能够提升BPDs的转化效率,他们通过这种方式获得了无BPD缺陷的SiC外延层。此外,采用KOH-NaOH-MgO共熔混合物刻蚀衬底[104]、氢气原位刻蚀衬底[105]、间隔再生长方法[106]、引入缓冲层[107-108]等方式也能够有效提高BPDs的转换效率,甚至达到100%转换。

图7 刻蚀后Si面4H-SiC表面光学显微形貌图[92-93]Fig.7 Optical microscopic images of Si surface 4H-SiC after etching[92-93]

图8 衬底沿方向倾斜情况下BPD位错线以及TED位错线与生长方向之间夹角[99]Fig.8 Angle between the BPD dislocation line, the TED dislocation line and the growth direction when the substrate is tilted along the direction[99]

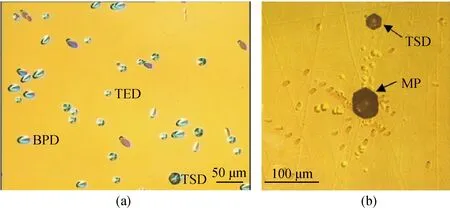

表面缺陷起因于SiC衬底表面颗粒物、结晶缺陷、表面划痕、亚损伤层,在台阶流控制生长机理下在外延层表面形成不完整性形貌缺陷,这些缺陷通过强光束、显微镜可被观察到。对器件性能造成致命影响的缺陷主要包括掉落物、三角形缺陷、彗星缺陷、胡萝卜缺陷, 其表面形貌如图9所示[109-110]。其中掉落物通过定期清理反应室部件、避免使用易脱落颗粒物部件的方式能够有效消除。三角形缺陷显著降低pn结二极管耐压特性[111],对于结型势垒肖特基二极管(JBS),三角形缺陷造成器件在低偏压下正向电流和反偏下漏电流的增加[112]。彗星型缺陷造成器件击穿电压降低、反向漏电增加[113],而胡萝卜型缺陷主要影响器件反向漏电流,对器件击穿电压无影响[95]。由于三角形缺陷对器件带来致命影响,研究者对三角形缺陷形成原因及消除手段进行了探索。Li等[114]发现三角形缺陷起源于衬底表面螺位错或者自发成核,通过优化H2刻蚀时间和温度以及C/Si比能够降低三角形缺陷浓度。Leone等[115]证明低的生长温度以及C/Si比有利于减少三角形缺陷的形成。Yan等[116]提出C/Si比是优化SiC外延层结晶质量的关键参数,相比于无偏角衬底,偏4°衬底上C/Si比可调节窗口更大。

图9 SiC中的(a)三角形缺陷[109],(b)胡萝卜缺陷[110]和(c)彗星型缺陷[110]Fig.9 (a) Triangular defect[109], (b) carrot defect[110] and (c) comet defect[110] in SiC

点缺陷在SiC禁带中引入深能级,起复合中心或陷阱中心作用,影响材料中少子寿命及不均匀性。SiC中常见深能级缺陷中心主要为Z1/2(Ec-0.63 eV)、EH6/7(Ec-1.48 eV)、HK2(EV+0.84 eV)、HK3(EV+1.24 eV)、HK4(EV+1.44 eV)[117-119]。其中HK2、HK3、HK4三种缺陷通过1 450~1 550 ℃退火几乎可完全消除。Z1/2与EH6/7缺陷热稳定性高,是限制载流子寿命,导致器件漏电流增大的原因[120-121]。研究表明,Z1/2与EH6/7缺陷与C空位(VC)的不同电荷态相关[122-123]。经过多年的发展,研究者们提出了多种有效减少Z1/2与EH6/7缺陷浓度的方式。Hiyoshi等[124]认为热氧化处理后SiO2/SiC界面高浓度C以间隙原子向SiC内部扩散与C空位复合或者形成复合缺陷,最终达到降低C空位缺陷的目的。随后他们发现,虽然热氧化能够有效降低Z1/2与EH6/7缺陷浓度,但是同时引入了高浓度的缺陷能级HK0(EV+0.78),在Ar气氛围中1 550 ℃退火能够有效消除该缺陷[125]。Storasta等[126]通过C离子注入在SiC外延层中提供C间隙原子,之后退火使间隙原子扩散填充C空位,成功将Z1/2与EH6/7缺陷浓度降低了两个数量级。其他研究发现,随着外延过程中C/Si比的增加,Z1/2浓度降低,这也证明Z1/2与C空位相关。降低外延生长温度可降低Z1/2与EH6/7缺陷浓度[127-129]。在p型SiC中,热氧化和C离子注入对载流子寿命的改善效果并不理想[130]。研究者们发现,热氧化之后在H2氛围中进行退火处理能够增加载流子寿命,说明在p型SiC中,除C空位以外还有另外一种能够被H2钝化的缺陷对载流子寿命带来致命影响[131]。

3 基于SiC衬底的其他宽禁带半导体材料外延

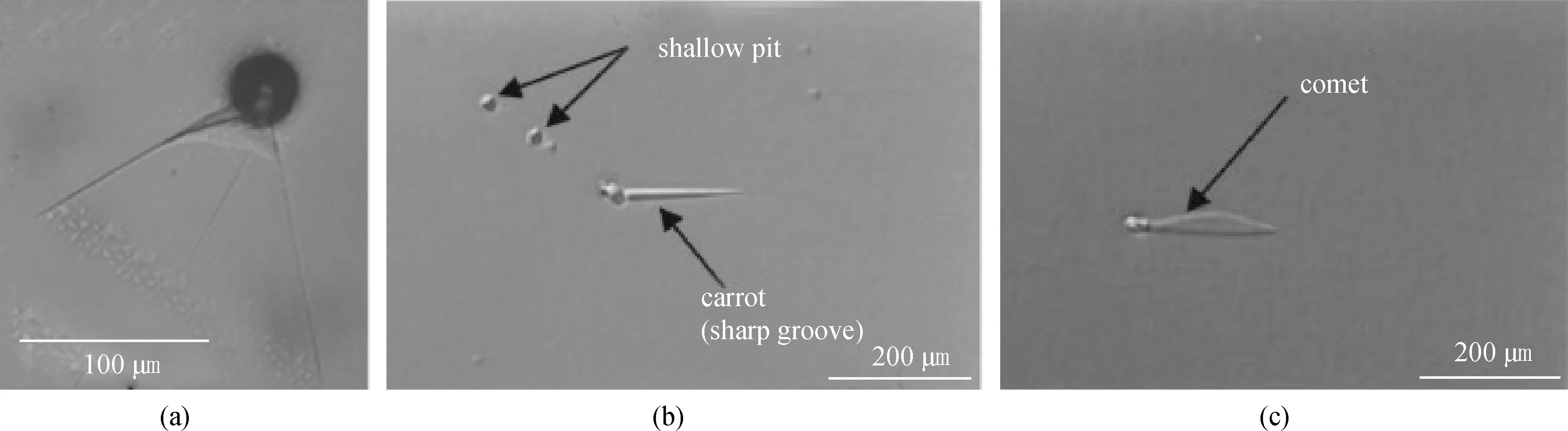

Ga2O3作为新兴宽禁带半导体材料,有望对现有的SiC及GaN技术形成技术互补,在低频、高压领域有潜在的应用前景。Ga2O3存在多种晶相,其中β-Ga2O3晶相最稳定。β-Ga2O3具有宽带隙(4.8 eV)和高击穿电场(8 MV·cm-1)等优异特性,在功率电子器件领域具有较大应用潜力。但是其极低的热导率限制了β-Ga2O3在高压条件下的应用。得益于良好的导热性及其与β-Ga2O3较小的晶格失配(1.3%),SiC衬底在外延β-Ga2O3领域具有广阔的应用前景。Russell等[132]通过仿真验证了采用4H-SiC衬底的β-Ga2O3MOSFET内部温度分布更均匀(见图10)。Nepal等[133]利用MBE在SiC衬底上外延β-Ga2O3,测得Ga2O3/SiC界面的热导率为(140±60) MW/(m2·K), 表明SiC衬底能够有效改善Ga2O3外延层的散热问题。但是,在Ga2O3/SiC界面处形成的SiOx多晶层会影响Ga2O3结晶质量,这是SiC衬底上外延β-Ga2O3须解决的关键问题之一。

图10 (a)β-Ga2O3衬底,(b)4H-SiC衬底 MOSFET Vgs=8 V时模拟晶格温度分布图[132]Fig.10 Simulation lattice temperature distribution of MOSFET (Vgs=8 V) based on (a) β-Ga2O3 substrate,(b) 4H-SiC substrate[132]

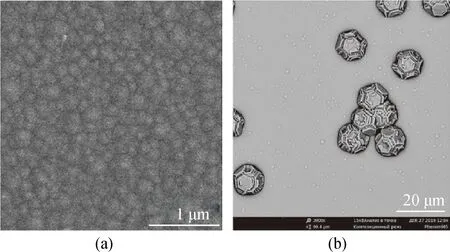

此外,亚稳相的ε-Ga2O3由于具有P63mc结构,有利于与SiC、GaN等宽禁带半导体结合应用。SiC衬底与ε-Ga2O3晶格失配较小,且衬底为P63mc结构,对亚稳ε-Ga2O3的形成具有诱导作用。Xia等[134]采用MOCVD在6H-SiC衬底上获得了晶相统一、表面平坦的ε-Ga2O3,表面形貌如图11(a)所示。900 ℃退火后,ε-Ga2O3全部转换为β-Ga2O3。之后Nikolaev等[135]通过HVPE在4H-SiC衬底上外延ε-Ga2O3只得到了部分六方对称的岛状结构,如图11(b)所示。他们认为这些六角对称岛的形成并不是都与外延层晶格结构相关,而是由旋转畴的形成引起的[135]。目前基于SiC衬底的Ga2O3外延研究尚处于起步阶段,如何获得高结晶质量连续薄膜仍然需要进一步努力。

图11 (a)6H-SiC衬底外延ε-Ga2O3[134],(b)4H-SiC衬底外延ε-Ga2O3[135]的表面SEM照片Fig.11 Surface SEM images of epitaxial ε-Ga2O3 on (a) 6H-SiC substrate[134] and (b) 4H-SiC substrate[135]

4 结语与展望

本文总结了SiC衬底上GaN、SiC、Ga2O3等外延生长与缺陷调控研究进展。尽管SiC衬底与GaN晶格失配较小,但是仍然存在晶格失配与热失配、Ga原子浸润性差、衬底缺陷等问题,影响高质量GaN外延层的获得。采用AlN、AlGaN缓冲层、图形化衬底、掩膜等方法能够有效改善GaN外延质量。如何平衡GaN与SiC衬底之间的应力,在SiC衬底上直接外延高质量GaN仍需要进一步探索。SiC同质外延是制备功率器件的基础,高质量大尺寸厚膜外延是提高器件耐压特性的关键,目前主要通过提高生长速度获得SiC厚膜,如何在提高外延生长速度的同时确保外延层的高质量是SiC同质外延面临的重要挑战。对于SiC衬底上外延Ga2O3的研究尚处于起步阶段,如何获得晶相统一、表面平坦的单晶薄膜尚需要继续研究。随着SiC衬底上外延宽禁带半导体材料技术的不断突破,宽禁带半导体电子器件将会更深入地应用于高频、高功率、低损耗等领域,实现宽禁带半导体应用的全面突破。